0 引言

虛擬儀器LabVIEW目前已廣泛應(yīng)用于測試領(lǐng)域,出發(fā)點和歸宿是“軟件化的真實儀器”。LabVIEW同時又是一個優(yōu)秀的仿真系統(tǒng),但真正處于仿真目的使用的并不多見,本文提出數(shù)字“虛擬芯片”概念,并基于LabVIEW實現(xiàn)仿真運用。

所謂“虛擬芯片”,是在充分利用LabVIEW圖形化語言風(fēng)格和強(qiáng)大信號處理功能的基礎(chǔ)上,設(shè)計具有一定顯示界面的虛擬輸入/輸出端子、能完成相應(yīng)的數(shù)字邏輯運算功能或數(shù)字信號處理功能的計算機(jī)程序,也就是LabVIEW的VI。應(yīng)當(dāng)說這是新時期數(shù)字邏輯電路設(shè)計、實驗或教學(xué)的一種新舉措,基于LabVIEW的數(shù)字虛擬芯片和原理圖設(shè)計與其他仿真系統(tǒng)相比,不但有自身的特點,也是對虛擬儀器系統(tǒng)LabVIEW應(yīng)用新領(lǐng)域的拓展和補(bǔ)充。

1 基于LabVIEW實現(xiàn)虛擬數(shù)字邏輯電路仿真的可行性及優(yōu)點

由前面板實現(xiàn)數(shù)字電路的各種控制和顯示,由程序流程圖實現(xiàn)數(shù)字電路的邏輯運算功能,是基于虛擬儀器LabVIEW進(jìn)行數(shù)字邏輯電路仿真設(shè)計的基礎(chǔ)。LabVIEW的前面板提供了大量數(shù)值、布爾控件。后面板提供了大量的函數(shù)模塊,使用這些函數(shù)可以很方便地調(diào)用或設(shè)計出各種門電路、編碼器、譯碼器、運算器、存儲器、觸發(fā)器、定時器、ADC/DAC等數(shù)字電路設(shè)計中常用的器件模塊。在數(shù)字電路中,高電平和低電平2種邏輯狀態(tài)可用前面板中的布爾控件提供;而電路設(shè)計中的各種模擬量可以用各種數(shù)值型控件及函數(shù)信號發(fā)生器產(chǎn)生和提供。基于LabVIEW實現(xiàn)虛擬數(shù)字邏輯電路的可行性及優(yōu)點,還表現(xiàn)在以下幾方面:

(1)可充分使用LabVIEW強(qiáng)大的輸入/輸出控件資源

(2)LabVIEW中的圖形化語言風(fēng)格適合數(shù)字電路的邏輯圖構(gòu)建:

布爾控件圖標(biāo)與數(shù)字邏輯門電路符號相近;圖形化的G語言風(fēng)格適合邏輯圖的連接。

(3)可開發(fā)通用或?qū)S玫臄?shù)字虛擬芯片庫(模塊庫)

(4)LabVIEW虛擬儀器可實現(xiàn)與外部數(shù)據(jù)的交換

2 基于LabVIEW的數(shù)字虛擬芯片設(shè)計方法

下面從一個有異步復(fù)位、置位端子的虛擬觸發(fā)器單元設(shè)計開始,以LabVIEW中邏輯運算VI作為虛擬“門電路”單元,構(gòu)建通用數(shù)字邏輯芯片、計數(shù)器74160虛擬“芯片”,討論并實現(xiàn)該虛擬芯片的仿真應(yīng)用。

2.1 具備異步復(fù)位、置位端的虛擬觸發(fā)器設(shè)計

低電平有效的異步置位、復(fù)位功能的虛擬JK觸發(fā)器特性方程可表示為:

![]()

當(dāng)滿足約束條件RD+SD=1,即RD、SD不同時為有效電平(邏輯值0)時,這2個端子可作為異步置位端(SD)和異步復(fù)位端(RD),即有:

使用過程中應(yīng)當(dāng)注意滿足約束條件(當(dāng)RD+SD=O時,始終有QN+1=O)。

根據(jù)式(1)構(gòu)建的低電平有效的異步置位、復(fù)位功能的JK觸發(fā)器LabVIEW后面板如圖1所示,其異步置位、復(fù)位端動作不受同步CP控制,直接實現(xiàn)操作(觸發(fā)器狀態(tài)直接被置位或復(fù)位)。為實現(xiàn)CP輸入下降沿有效的動作方式,程序中引入了條件結(jié)構(gòu)控制。當(dāng)無有效CP邊沿輸入時,輸入觸發(fā)器端子的數(shù)據(jù)是J=K=“false”,等價于J=K=0,觸發(fā)器處于保持狀態(tài);只有當(dāng)有效CP下降沿輸入時,觸發(fā)器才接收輸入控件J,K的數(shù)據(jù),實現(xiàn)相應(yīng)的動作。圖1中左下角部分程序就是實現(xiàn)CP下降沿輸入有效的控制程序部份。

定義圖1中VI的各輸入、輸出端子,編輯好相應(yīng)的VI圖標(biāo),將其保存為一獨立VI文件,最后得到對應(yīng)的VI圖標(biāo)及連線如圖2所示。這樣的VI圖標(biāo)即可看作一個虛擬觸發(fā)器。

圖2中2個圖標(biāo)為同一VI在LabVIEW中的2種不同顯示方式,且2個圖標(biāo)為同一VI分別以不同文件名保存的2個文件。(程序完全相同)

2.2 基于虛擬JK觸發(fā)器及LabVIEW虛擬“邏輯門”構(gòu)

虛擬儀器LabVIEW中的邏輯運算VI,可以完成各種基本邏輯運算,在仿真數(shù)字邏輯電路時可當(dāng)作虛擬的“門電路”直接使用,部份圖標(biāo)如圖3所示。

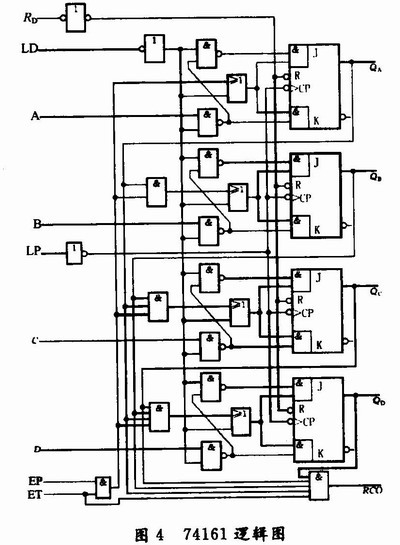

集成計數(shù)器74161的內(nèi)部邏輯圖如圖4所示。

它是4位二進(jìn)制同步加法計數(shù)器,有異步清零、預(yù)置數(shù)端子和兩個使能控制端子,各端子的含義如下:

(1)RD:異步清零端,低電平有效

(2)LD:預(yù)置數(shù)使能控制端,低電平有效

(3)預(yù)置數(shù)據(jù)輸入端:A、B、C、D

(4)CP;時鐘輸入端,上升沿有效

(5)狀態(tài)輸出端:QA~QD

(6)RCO:進(jìn)位輸出

74161的邏輯功能:

(1)異步清零功能:當(dāng)RD=0時,不管其余輸入端狀態(tài)如何,計數(shù)器均被置零,且不受CP控制,故稱為“異步清零”。

(2)同步并行預(yù)置數(shù)功能:當(dāng)RD=1且LD=0時,每一個有效CP都將A、B、C、D輸入端的數(shù)據(jù)傳送至QA~QD狀態(tài)端子接收。

(3)狀態(tài)數(shù)據(jù)保持功能:當(dāng)RD=LD=1,且ET·EP=0時,無論CP有無,計數(shù)器處于保持狀態(tài)(QA~QD保持不變)。保持狀態(tài)分2種情況:

EP=0,ET=1:進(jìn)位輸出RCO保持不變;ET=O,無論EP為何值,進(jìn)位輸出RCO=0。

(4)計數(shù)功能:當(dāng)RD=LD=EP=ET=1時,電路處于正常的加法計數(shù)狀態(tài)。

根據(jù)74161邏輯圖,編制相應(yīng)的LabVIEW后面板,結(jié)果如圖5所示。從圖5中可以看出,對應(yīng)很好。

保留并定義所有輸入端和輸出端子,編輯圖標(biāo),將程序保存為子VI,稱之為虛擬74161芯片,其VI圖標(biāo)及連線端口如圖6所示。

下面討論虛擬芯片74161設(shè)計及應(yīng)用。

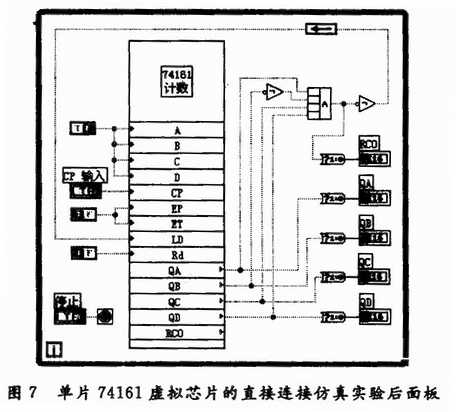

運用1片74161及LabVIEW系統(tǒng)中的邏輯運算VI(相當(dāng)于虛擬門)圖標(biāo)直接連接,構(gòu)建一個14進(jìn)制計數(shù)器,實驗后面板(虛擬邏輯圖)如圖7所示。

圖7所示后面板中用一片74161虛擬芯片,基于74161置數(shù)歸零法來實現(xiàn)14進(jìn)制計數(shù)功能(帶進(jìn)位輸出)。計數(shù)容量為0000~1101,置數(shù)控制端輸入取![]() 。

。

相應(yīng)的實驗前面板如圖8所示。計數(shù)狀態(tài)設(shè)置為RD=EP=ET=“True”,相當(dāng)于邏輯1,可從CP控件手動輸入計數(shù)脈沖實現(xiàn)計數(shù)并實驗。圖中顯示為計數(shù)至1101時,進(jìn)位輸出為1的狀態(tài)。當(dāng)下一個CP到來時,則全部清零重新計數(shù)。

仿真實驗的結(jié)果表明,虛擬74161具有實際電路芯片相同的邏輯功能。

3 時序虛擬芯片設(shè)計應(yīng)注意的關(guān)鍵問題

對于組合邏輯,只須按邏輯圖直接進(jìn)行連線即可,但對于時序邏輯,應(yīng)當(dāng)注意下述問題:

(1)需要將狀態(tài)數(shù)據(jù)緩存時,應(yīng)當(dāng)在數(shù)據(jù)傳遞過程中使用反饋節(jié)點或移位寄存器。

(2)任一觸發(fā)器或時序芯片單元,在同一虛擬電路中不能重復(fù)使用(調(diào)用)文件名相同的同一子VI程序。

原因是當(dāng)調(diào)用某時序子VI時,其保存的狀態(tài)數(shù)據(jù)將發(fā)生變化,從而導(dǎo)致用到同一VI的其他經(jīng)程序單元狀態(tài)數(shù)據(jù)發(fā)生不可預(yù)知的錯誤。即虛擬電路中使用的任一時序單元對應(yīng)的子Vl都應(yīng)當(dāng)保證是惟一的獨立(子)程序,要多次使用就必須分別以不同文件名保存后再分別調(diào)用。

4 結(jié)語

將虛擬儀器的強(qiáng)大功能應(yīng)用于數(shù)字邏輯電路的仿真,在虛擬儀器系統(tǒng)中構(gòu)建各種虛擬“芯片”,并以此作為虛擬“元件”,可進(jìn)一步“搭建”各種虛擬“數(shù)字電路”。虛擬儀器應(yīng)用于數(shù)字電路的仿真技術(shù),可以高效快捷地設(shè)計數(shù)字電路的原理圖、分析數(shù)字電路的邏輯功能及開展基于虛擬儀器的數(shù)字電路實驗、教學(xué),同時還能拓展虛擬儀器新的應(yīng)用領(lǐng)域。