摘 要: 介紹一種基于PCI總線的高效鏈?zhǔn)?/a>" title="鏈?zhǔn)?>鏈?zhǔn)?/a>DMA控制器的設(shè)計與實(shí)現(xiàn),用于高速寬帶的計算機(jī)外設(shè)接口。利用Altera公司的PCI核——PCI_MT32搭建基于此控制器的數(shù)據(jù)采集平臺,并成功應(yīng)用在DVB數(shù)據(jù)接收卡中。

關(guān)鍵詞: PCI 鏈?zhǔn)?DMA控制器

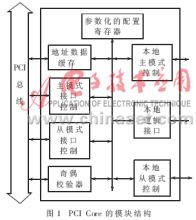

1991 年P(guān)CISIG(外圍部件互連專業(yè)組)成立,提出了PCI的概念[1]。Altera公司提供的軟件包:PCI Compiler可以參數(shù)化地生成用于PCI接口的IP核——Megacore。該IP核包含了PCI控制電路的所有功能,完成總線協(xié)議的轉(zhuǎn)換,并將復(fù)雜的、電氣和時序要求高的PCI轉(zhuǎn)換為易于操作的本地接口邏輯。用戶可以基于其生成的IP核模塊,設(shè)計自己的外部設(shè)備接口邏輯。Altera的MegaCore包括四種類型:PCI_MT64、PCI_MT32、PCI_T64和PCI_T32[1]。它們都具有靈活的通用接口,遵循PCI協(xié)議2.2版,嚴(yán)格的工業(yè)級驗(yàn)證和多款優(yōu)化FPGA。考慮通常的PC主板都支持32位PCI,而且DMA控制器必須工作在主模式下,因此選擇了PCI_MT32,其模塊結(jié)構(gòu)如圖1所示。

·參數(shù)化的配置寄存器:保存PCI設(shè)備的基本信息,可以通過軟件參數(shù)設(shè)定寄存器。

·地址數(shù)據(jù)緩存:緩存PCI總線上的地址數(shù)據(jù)。

·主模式接口控制模塊" title="控制模塊">控制模塊:在主模式下對PCI總線的操作。

·從模式接口控制模塊:在從模式下對PCI總線的操作。

·奇偶校驗(yàn)器:當(dāng)校驗(yàn)出錯時,生成一個報錯信號輸出到配置寄存器。

·本地主模式控制模塊:主模式下,控制本地邏輯的接口。

·本地從模式控制模塊:從模式下,控制本地邏輯的接口。

·本地邏輯接口模塊:控制本地端接口的地址、數(shù)據(jù)、控制、字節(jié)使能等。

1 DMA控制器

針對高帶寬、低延時和大數(shù)據(jù)量的多媒體數(shù)據(jù),設(shè)計了基于PCI core的DMA數(shù)字衛(wèi)星電視接收卡。DVB協(xié)議中的基本數(shù)據(jù)單元為192字節(jié),因此把一次DMA傳輸?shù)臄?shù)據(jù)包定為192字節(jié)。

1.1 DMA控制器的結(jié)構(gòu)

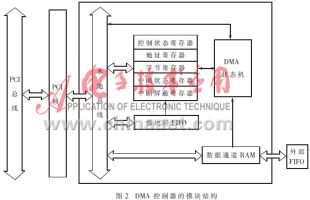

DMA控制器由DMA寄存器、描述符" title="描述符">描述符FIFO、DMA狀態(tài)機(jī)、數(shù)據(jù)通道" title="數(shù)據(jù)通道">數(shù)據(jù)通道RAM四個模塊構(gòu)成,如圖2所示。

DMA寄存器是主機(jī)控制DMA的窗口,包括控制狀態(tài)寄存器" title="狀態(tài)寄存器">狀態(tài)寄存器、地址寄存器、字節(jié)寄存器、中斷狀態(tài)寄存器和中斷屏蔽寄存器[2]。描述符FIFO是一個32×256的FIFO,在鏈?zhǔn)紻MA模式下可以暫存128組DMA的描述符。DMA狀態(tài)機(jī)是控制PCI總線數(shù)據(jù)傳輸?shù)暮诵模髂J较碌腄MA有主模式寫和主模式讀兩種類型。主模式寫是把數(shù)據(jù)通道RAM里的數(shù)據(jù)包通過PCI總線傳送到從設(shè)備,主模式讀則讀取從設(shè)備的數(shù)據(jù)包傳送到數(shù)據(jù)通道RAM中[4]。

1.2 DMA寄存器

DMA寄存器的地址直接映射到PCI的地址空間,其基地址由PCI Core中的配置寄存器Bar0決定。主機(jī)通過訪問這些寄存器來控制DMA操作。

·控制狀態(tài)寄存器:主機(jī)通過寄存器配置DMA狀態(tài)機(jī),同時也可以獲得當(dāng)前數(shù)據(jù)傳輸?shù)臓顟B(tài)。

·地址寄存器:保存PCI總線地址,即DMA傳輸?shù)哪繕?biāo)地址。當(dāng)?shù)刂芳拇嫫魍瓿蓪懖僮鳎珼MA狀態(tài)機(jī)將被啟動。

·字節(jié)寄存器:其初始值為一次DMA傳輸數(shù)據(jù)的大小,PCI每傳送一個數(shù)據(jù),字節(jié)寄存器的值就減1,減到0則DMA停止傳輸。

·中斷狀態(tài)寄存器:為主機(jī)提供PCI設(shè)備的中斷狀態(tài)。

·中斷屏蔽寄存器:可以屏蔽PCI設(shè)備的中斷請求。

1.3 DMA狀態(tài)機(jī)

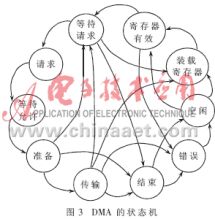

DMA的狀態(tài)機(jī)如圖3所示。

·空閑狀態(tài):狀態(tài)機(jī)無數(shù)據(jù)傳輸時默認(rèn)停留在這一狀態(tài)。通過寫DMA寄存器,可啟動一次DMA傳輸。

·裝載寄存器狀態(tài):當(dāng)鏈?zhǔn)絺鬏敃r,進(jìn)入裝載寄存器狀態(tài)。將描述符 FIFO中的一組描述符裝入字節(jié)寄存器和地址寄存器后,進(jìn)入寄存器有效狀態(tài)。

·寄存器有效狀態(tài):DMA傳輸前,如果外部FIFO中的數(shù)據(jù)已經(jīng)準(zhǔn)備好,則進(jìn)入等待請求狀態(tài)。

·等待請求狀態(tài):等待一個數(shù)據(jù)包從外部FIFO送入數(shù)據(jù)通道RAM,進(jìn)入請求狀態(tài)。

·請求狀態(tài):申請PCI總線的控制權(quán),進(jìn)入等待允許狀態(tài)。

·等待允許狀態(tài):當(dāng)PCI設(shè)備獲得了總線的控制權(quán),進(jìn)入準(zhǔn)備狀態(tài)。

·準(zhǔn)備狀態(tài):當(dāng)數(shù)據(jù)傳輸結(jié)束或者PCI總線終止傳輸,則進(jìn)入結(jié)束狀態(tài);當(dāng)PCI總線插入等待周期,則返回等待請求狀態(tài),重新申請總線的控制權(quán);當(dāng)PCI總線的地址期結(jié)束將要進(jìn)入數(shù)據(jù)期,則進(jìn)入傳輸狀態(tài)。

·傳輸狀態(tài):當(dāng)數(shù)據(jù)傳輸結(jié)束或者PCI總線終止傳輸,則進(jìn)入結(jié)束狀態(tài);當(dāng)PCI總線插入等待周期,則返回等待請求狀態(tài),重新申請總線的控制權(quán);當(dāng)本次數(shù)據(jù)傳輸結(jié)束,但是本次鏈?zhǔn)紻MA沒有結(jié)束,則進(jìn)入裝載寄存器狀態(tài)。

·結(jié)束狀態(tài):一次DMA結(jié)束,或者一次鏈?zhǔn)紻MA結(jié)束,狀態(tài)機(jī)進(jìn)入結(jié)束狀態(tài),同時發(fā)出中斷信號。

·錯誤狀態(tài):當(dāng)PCI abort、 PCI system error、 PCI parity error、FIFO full等錯誤出現(xiàn)時,狀態(tài)機(jī)進(jìn)入錯誤狀態(tài),同時發(fā)出中斷信號。

1.4 DMA操作流程

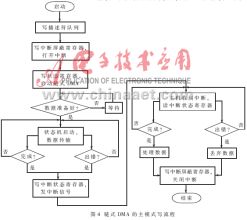

以非鏈?zhǔn)紻MA的主模式寫為例,主機(jī)首先寫控制狀態(tài)寄存器、中斷屏蔽寄存器、字節(jié)寄存器、地址寄存器,而后狀態(tài)機(jī)啟動;當(dāng)外部FIFO數(shù)據(jù)準(zhǔn)備好,數(shù)據(jù)先傳到數(shù)據(jù)通道RAM,再以DMA方式寫到目標(biāo)地址;判斷DMA是否完成或出錯,寫中斷狀態(tài)寄存器,發(fā)出中斷信號;主機(jī)收到中斷后,讀中斷狀態(tài)寄存器確定中斷類型,如果發(fā)現(xiàn)DMA完成,則處理數(shù)據(jù),如果發(fā)現(xiàn)DMA出錯,則丟棄數(shù)據(jù)。

鏈?zhǔn)紻MA可以認(rèn)為是一組DMA的串連,其流程如圖4所示。其中每一次DMA的數(shù)據(jù)包大小和目標(biāo)地址可以不同,直到這一組DMA結(jié)束,發(fā)出一個中斷信號。以主模式寫為例,主機(jī)首先把多組字節(jié)寄存器和地址寄存器的值寫入描述符 FIFO,每一組字節(jié)寄存器和地址寄存器就是一個描述符;主機(jī)再寫中斷屏蔽寄存器和控制狀態(tài)寄存器即啟動了DMA狀態(tài)機(jī),開始鏈?zhǔn)降臄?shù)據(jù)傳輸。

與非鏈?zhǔn)紻MA相比,鏈?zhǔn)紻MA有更多的優(yōu)點(diǎn),以一次寫入128個描述符的鏈?zhǔn)紻MA為例:

·節(jié)省軟件的開銷。非鏈?zhǔn)紻MA每啟動一次傳輸,只能傳一個數(shù)據(jù)包,而鏈?zhǔn)紻MA一次寫入128組描述符,就可以傳128個數(shù)據(jù)包。非鏈?zhǔn)紻MA一個數(shù)據(jù)包傳輸結(jié)束主機(jī)就響應(yīng)一次中斷,而鏈?zhǔn)紻MA每128個數(shù)據(jù)包傳輸結(jié)束主機(jī)響應(yīng)一次中斷。鏈?zhǔn)紻MA啟動和響應(yīng)頻率降為原來的1/128,從而提高了傳輸速度。

·節(jié)省硬件資源。如果希望用非鏈?zhǔn)紻MA可靠地傳輸一個大數(shù)據(jù)包,需要RAM的容量至少等于這個數(shù)據(jù)包的大小。例如非鏈?zhǔn)紻MA一次傳128×192字節(jié)的數(shù)據(jù),則需要192K位的存儲容量。而鏈?zhǔn)紻MA可以把此數(shù)據(jù)包分成128次傳輸,僅使用1.5K位的存儲容量,節(jié)省RAM資源。

·靈活的地址管理。鏈?zhǔn)紻MA可以對每個數(shù)據(jù)包任意分配目標(biāo)地址,那么一次操作可以讀寫一個從設(shè)備的多個地址空間,甚至多個從設(shè)備的多個地址空間。

2 設(shè)計結(jié)果

用VHDL編寫邏輯代碼,用ModelSim仿真,圖5是部分仿真波形:PCI的關(guān)鍵信號、DMA狀態(tài)機(jī)、DMA寄存器。這是鏈?zhǔn)紻MA啟動寫操作時的信號變化,數(shù)據(jù)包的大小是192字節(jié),目標(biāo)基地址是0x40000104。

使用Altera公司的QuartusII對設(shè)計綜合,選用器件Cyclone EP1C6Q240C8,綜合結(jié)果如表1所示。

最高時鐘頻率可以達(dá)到86.57MHz。綜合生成網(wǎng)表文件下載到FPGA,經(jīng)過實(shí)際測試,系統(tǒng)運(yùn)行正常。用邏輯分析儀測試PCI的關(guān)鍵信號,非鏈?zhǔn)紻MA和鏈?zhǔn)紻MA傳輸128個數(shù)據(jù)包的統(tǒng)計信息如表2所示。

鏈?zhǔn)紻MA的平均數(shù)據(jù)率達(dá)到44.4Mbps,幾乎是非鏈?zhǔn)紻MA的2倍,這主要得益于軟件響應(yīng)時間的縮短。因此,對于非鏈?zhǔn)紻MA,數(shù)據(jù)包越大數(shù)據(jù)率就越快;對于鏈?zhǔn)紻MA,在數(shù)據(jù)包大小固定的前提下,數(shù)據(jù)包個數(shù)越多,相對響應(yīng)時間會越少,數(shù)據(jù)率越快。

參考文獻(xiàn)

1 PCI Local Bus Specification Revision 2.2. December 18,1998

2 Altera Corporation. PCI MegaCore Function User Guide, 2003

3 Altera Corporation. PCI_MT32 MegaCore Function Reference Design, 2003

4 李貴山, 戚德虎. PCI局部總線開發(fā)指南. 西安:西安電子科技大學(xué)出版社,1997