許多嵌入式應(yīng)用都會(huì)用到A/D轉(zhuǎn)換器。然而,如果錯(cuò)誤連接了A/D轉(zhuǎn)換器輸入端的電路,就會(huì)無(wú)意識(shí)的破壞A/D轉(zhuǎn)換的測(cè)量。

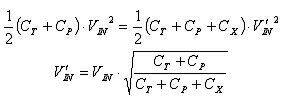

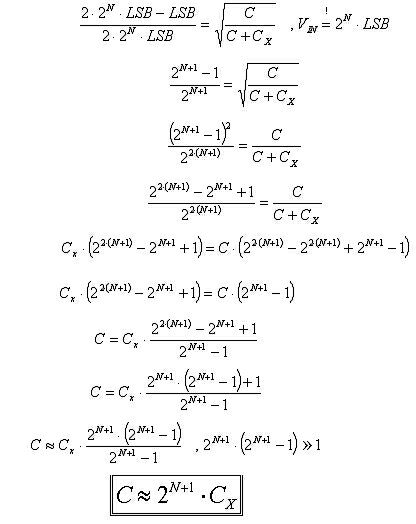

圖1是A/D轉(zhuǎn)換器和集成采樣保持(S/H)電路的典型應(yīng)用實(shí)例。這是一個(gè)非常簡(jiǎn)單的應(yīng)用,幾乎不可能出現(xiàn)錯(cuò)誤連接。然而它確實(shí)是錯(cuò)誤的,由此檢測(cè)到的A/D轉(zhuǎn)換器的數(shù)值將低于預(yù)期的數(shù)值。

要了解錯(cuò)在哪里,我們就得先檢查采樣保持電路。如今的采樣保持電路遠(yuǎn)比圖例中的電路要復(fù)雜得多,但基本的原理還是相同的。在采樣過(guò)程中開關(guān)處于閉合狀態(tài),并對(duì)采樣電容進(jìn)行充電。為了保護(hù)外部電路,防止由于電容突然與自己的輸出相連而對(duì)外部電路形成沖擊,我們?cè)谄霞闪艘粋€(gè)模擬緩沖器。我們?cè)诶碚撛O(shè)計(jì)和圖紙?jiān)O(shè)計(jì)時(shí)都會(huì)用到理想的緩沖器,但真實(shí)的電子世界里并不存在這樣的理想狀況。在這里,緩沖器更像是一個(gè)阻抗變換器,它會(huì)把自己輸出端電容量的變化轉(zhuǎn)化為其輸入端電容量的變化。

A/D轉(zhuǎn)換器的輸入端與一個(gè)外部放大器相連。由于采樣過(guò)程非常迅速,比外部放大器的帶寬快得多,因此無(wú)論A/D轉(zhuǎn)換器的輸入端怎樣變化,都不受外部放大器的影響。

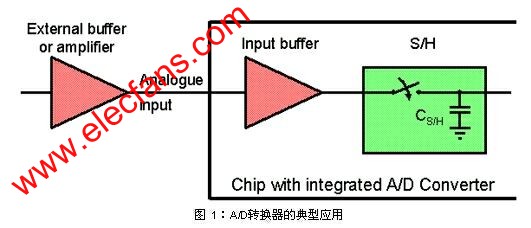

圖2是一個(gè)等效電路,它使我們能夠了解整個(gè)采樣過(guò)程。在采樣發(fā)生前,PCB導(dǎo)線和芯片引腳的組合電容(CT+CP)被充電為輸入電壓VIN。在采樣時(shí),由片上輸入緩沖器的電容與放電的采樣保持電容合并而成的(CX),與這些組合電容處于并聯(lián)狀態(tài),因此輸入引腳的電壓將下降。在這種情況下,唯一能向這些電容器傳遞更多電荷并抬高輸入電壓的器件就只有外部放大器,但它的反應(yīng)非常遲緩。此時(shí),輸入的電壓值會(huì)下降多少呢?

我們先假設(shè)某些合理值,例如(CT+CP)=5pF,CX=0.5pF。根據(jù)上面的公式計(jì)算,輸入電壓將下降到95%!

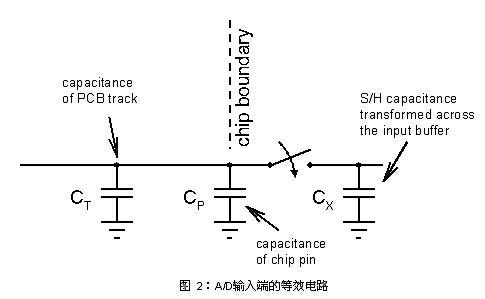

很明顯,通過(guò)提高依附于A/D轉(zhuǎn)換器輸入端的電容量,就可以減輕壓降。我們先來(lái)計(jì)算一下要想使壓降低于A/D轉(zhuǎn)換器的1/2 LSB,所需要的最小電容量。

當(dāng)輸入電壓為允許的最大值時(shí),情況將最糟糕。如果假設(shè)A/D轉(zhuǎn)換器的解析度為N位時(shí),其允許的最大輸入電壓相當(dāng)于2N.LBS。

因此如果我們用12位A/D轉(zhuǎn)換器、輸入電容的變化值為0.5pF時(shí),與A/D轉(zhuǎn)換器輸入端相連的最小電容必須大于2130.5pF(例如4nF),以便使壓降小于1/2LSB。

眾所周知,芯片制造商通常不能為設(shè)計(jì)師提供足夠的數(shù)據(jù)。我看過(guò)許多A/D轉(zhuǎn)換器的datasheet,發(fā)現(xiàn)它們都沒(méi)有提供采樣過(guò)程中輸入電容的變化數(shù)據(jù)。但我們能夠通過(guò)測(cè)量輕松得到這個(gè)參數(shù),而測(cè)量所需要的設(shè)備僅為一臺(tái)示波器和一臺(tái)信號(hào)發(fā)生器。值得說(shuō)明的是,這一簡(jiǎn)單測(cè)量的結(jié)果并不準(zhǔn)確,但至少可以讓我們粗略地估計(jì)出這一參數(shù)值。我們可以通過(guò)觀測(cè)芯片引腳的壓降,計(jì)算出電容值的變化情況。

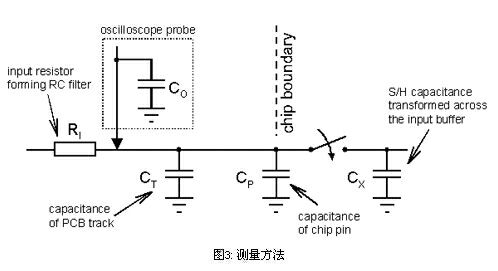

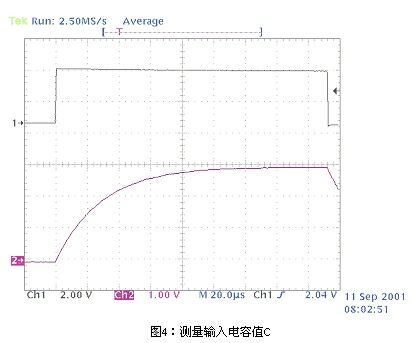

測(cè)量方法如圖3所示。為了方便測(cè)量,RC網(wǎng)絡(luò)的時(shí)間常數(shù)要足夠長(zhǎng),因此輸入電阻RI的阻值要足夠大。我在測(cè)量中就用了1MOhm的電阻。圖4和圖5顯示的測(cè)量采用了飛思卡爾半導(dǎo)體的混合控制器DSP56F805。這些測(cè)量值是適用于整個(gè)DSP56F80x系列的快速A/D轉(zhuǎn)換器的典型值。首先,我們得測(cè)量與A/D輸入端相連的電容值(C=CO+CT+CP)。我們先對(duì)輸入電阻施加一個(gè)方波信號(hào),然后通過(guò)顯示屏觀察結(jié)果波形的時(shí)間常數(shù)(如圖4)。我們可以從顯示屏上直接推算出這一時(shí)間常數(shù),但最好把數(shù)據(jù)輸入到excel中以求計(jì)算結(jié)果更精確。在圖4的例子中,時(shí)間常數(shù)大約為28.5μs。

因此在上面的例子中,C≈28.5μs/6.2832/1M Ohm≈4.54pF.

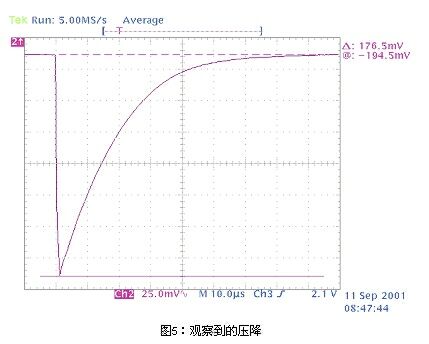

現(xiàn)在,我們將在允許的范圍內(nèi)對(duì)輸入電阻施加最高的DC電壓,啟動(dòng)A/D轉(zhuǎn)換。圖5顯示了最終的壓降:在3.3V時(shí),壓降約為176mV。

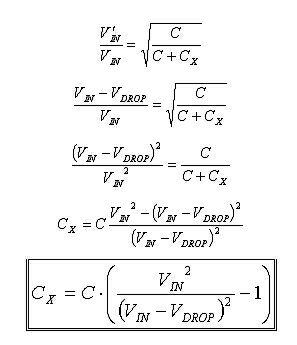

一旦我們測(cè)量到了壓降值,我們就可以計(jì)算出A/D轉(zhuǎn)換器輸入電容量的變化情況。

在這個(gè)例子中,CX=4.54pF?(3.32/3.1242-1)≈4.54pF?0.116≈0.53pF。

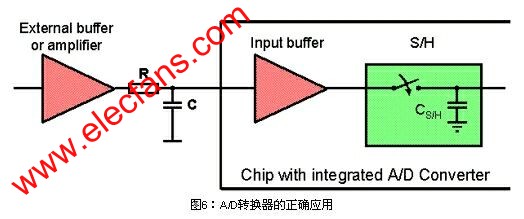

放大器通常不是電容性負(fù)載。因此圖6中增加了一個(gè)外部輸入電阻。由此形成的RC網(wǎng)絡(luò)還具有濾波功能,可以濾除高頻噪音。

A/D轉(zhuǎn)換器的輸入漏電流通常低于1μA。如果我們采用幾百ohm的電阻來(lái)充當(dāng)輸入電阻,則通過(guò)該電阻的壓降將為100μV左右,低于1/2LSB。