摘要:為滿足單片機學習中對實踐技能的要求,提高單片機開發(fā)系統(tǒng)的穩(wěn)定性和可擴展性,降低系統(tǒng)功耗,設(shè)計了一種基于FPGA的C8051F單片機開發(fā)板。利用FPGA實現(xiàn)鍵盤掃描、液晶驅(qū)動、地址譯碼以及其他外設(shè)接口,大幅度簡化外圍電路結(jié)構(gòu)。系統(tǒng)可在高低頻時鐘間切換以減小功耗,并增加了音頻處理模塊,實現(xiàn)基本的音頻信號的存儲和回放。實驗結(jié)果表明,該電路板相比普通的單片機開發(fā)板系統(tǒng)功耗減小50%左右,擁有最高達25 MIPS的處理速度,單片機可以直接驅(qū)動多達20多個LS TTL門電路,F(xiàn)PGA的引入使得外擴其他電路更為方便和靈活,具有良好的擴展性。

關(guān)鍵詞:單片機;FPGA;外圍電路;電路板

目前高校單片機教學中大多是以MCS51單片機為首選機型進行講解,所開發(fā)的教學實驗系統(tǒng)也多是基于MCS51系列單片機開發(fā)設(shè)計的。然而,隨著單片機的應(yīng)用進入SoC時代,其不足和缺陷也顯而易見:片上資源不夠豐富,功耗較大,處理速度很有限,電路龐大且復雜,可靠性和可維護性較差,難以滿足高水平的設(shè)計要求。

為了進一步簡化電路結(jié)構(gòu),提出一種C8051F單片機實驗系統(tǒng)設(shè)計方案,該方案采用FPGA實現(xiàn)單片機各種外設(shè)接口。FPGA作為一種可編程邏輯器件憑借其優(yōu)越的可擴展性能受到設(shè)計者的青睞,逐漸成為分立元件的替代者。通過對FPGA編程,實現(xiàn)任何數(shù)字元件的邏輯功能,設(shè)計者可以通過原理圖輸入或硬件描述語言,方便地設(shè)計一個數(shù)字系統(tǒng),這使得單片機外圍電路的設(shè)計簡單、靈活、可靠。

本系統(tǒng)是為單片機實踐教學而開發(fā)的,因此要求單片機的功能齊全,滿足教學中各種實驗的要求。一般的實驗板的功能有:模擬數(shù)字信號轉(zhuǎn)換實驗、通信接口實驗、存儲器實驗、各種顯示實驗,人機交互實驗等等。除此之外,還要考慮由于是非商業(yè)性質(zhì)的開發(fā),對一些功能的精度要求不是很高,在選擇最理想價格的同時,選擇盡可能多而全的片上資源,留待后期開發(fā)擴充。

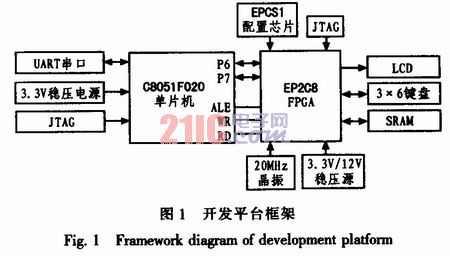

基于以上考慮,該平臺使用SoC系統(tǒng)級的C8051F020單片機作為核心控制器,CycloneⅡEP2C8型FPGA實現(xiàn)外設(shè)接口,加上LCD、鍵盤、UART串口等人機交互的模塊。

C8051F系列單片機是以流水線方式處理指令的CIP-5l內(nèi)核,完全集成的混合信號系統(tǒng)級芯片(Soc),片內(nèi)集成了數(shù)據(jù)采集和控制系統(tǒng)中常用的模擬、數(shù)字外設(shè)及其他功能部件。C8051F020單片機具有片內(nèi)調(diào)試電路,通過4引腳的JTAG接口可以進行非侵入式、全速的在系統(tǒng)調(diào)試。

FPGA即現(xiàn)場可編程門陣列,它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。FPGA使用靈活,同一片F(xiàn)PGA通過不同的編程數(shù)據(jù)可以產(chǎn)生不同的電路功能。

1 系統(tǒng)總體方案

本文設(shè)計并實現(xiàn)了基于FPGA的單片機開發(fā)平臺,該平臺主要包括有:單片機及其外設(shè)、FPGA擴展電路、電源及下載電路。開發(fā)平臺框架如圖l所示。

1.1 單片機外設(shè)

包括液晶顯示器(LCD)、鍵盤、SRAM、UART串口等,對FPGA進行編程來實現(xiàn)LCD、鍵盤、SRAM的接口電路。

1.2 FPGA擴展電路

包括主動串行(AS)配置電路、JTAG在線調(diào)試電路、輸入輸出電路等。采用EPCSlN8型芯片對FPGA進行主動串行(AS)配置,同時兼有JTAG在線調(diào)試模式。

1.3 電源及下載電路

單片機和FPGA均采用3.3V/1.2V穩(wěn)壓源供電,兩者均可通過JTAG接口進行在線調(diào)試。

FPGA和單片機以典型的三總線連接進行數(shù)據(jù)通信及控制,單片機內(nèi)部集成的數(shù)字/模擬資源和FPGA剩余的引腳通過插針引出,供用戶使用。將以上模塊有機結(jié)合起來,形成一個性能優(yōu)越的開發(fā)平臺,能夠滿足不同層次的設(shè)計需求。

2 硬件電路設(shè)計

在單片機系統(tǒng)的人機交互部分通常有液晶顯示器(LCD)、鍵盤和存儲器等外設(shè),因此需要用大量的標準邏輯器件對單片機進行擴展,這些器件的組合使用會導致設(shè)計周期長、可維護性差,用FPGA來實現(xiàn)單片機的外圍接口電路,能大大簡化電路結(jié)構(gòu),節(jié)省CPU資源。

2.1 鍵盤接口模塊

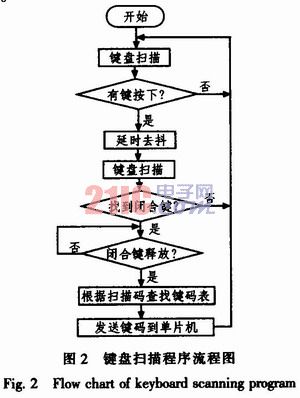

因為按鍵機械觸點的彈性作用,一個按鍵開關(guān)在閉合時不會馬上穩(wěn)定的導通,在斷開時也不會馬上斷開,因而在閉合及斷開的瞬間都會伴隨一連串的抖動,對于靈敏度較高的電路,這種抖動可能會造成誤動作而影響操作正確性。常用的去抖動的方法為延時去抖動法,即檢測出鍵閉合后執(zhí)行一個延時程序,產(chǎn)生5~lO ms的延時;讓前沿抖動消失后,再一次檢測鍵的狀態(tài),如果仍保持閉合狀態(tài)電平,則確認為真正

有鍵按下。當檢測到按件釋放后,也要給5~10 ms的延時,待后沿抖動消失后,才能轉(zhuǎn)入該鍵的處理程序。

對FPGA編程完成消除抖動及按鍵識別,由抖動消除模塊、鍵盤掃描電路、鍵盤譯碼電路、按鍵數(shù)據(jù)寄存器等組成。

鍵盤接口電路的工作流程為:采取逐行掃描法,F(xiàn)PGA周而復始地對鍵盤進行掃描,當有鍵按下時,先對按鍵進行延時去抖處理,將按鍵信號存入寄存器,掃描信號來臨時,根據(jù)按鍵掃描碼查找鍵碼表,并將其送回給單片機。程序流程如圖2所示。

2.2 液晶顯示模塊

液晶顯示器(LCD)以其微功耗、體積小、顯示內(nèi)容豐富、超薄輕巧等諸多優(yōu)點,在便攜式儀表和低功耗應(yīng)用系統(tǒng)中得到越來越廣泛的應(yīng)用。

LCD可分為段位式LCD、字符式LCD和點陣式LCD。其中,段位式LCD和字符式LCD只能用于字符和數(shù)字的簡單顯示,不能滿足圖形曲線和漢字顯示的要求;而點陣式LCD不僅可以顯示字符、數(shù)字,還可以顯示各種圖形、曲線及漢字,并且可以實現(xiàn)屏幕上下左右滾動,動畫功能,反轉(zhuǎn),閃爍等功能,用途十分廣泛。

點陣式LCD分為帶漢字字庫和不帶漢字字庫兩種,帶字庫LCD若要顯示漢字只要傳給漢字內(nèi)碼,而不帶字庫LCD顯示漢字時要先求出漢字字模,然后跟顯示圖形一樣顯示漢字。

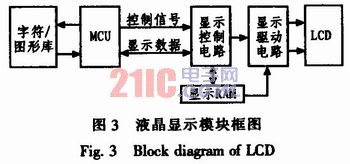

本開發(fā)系統(tǒng)采用博控公司生產(chǎn)的NS240*128A點陣圖形型LCD,不帶中文字庫。由于液晶顯示器是典型的慢速設(shè)備,如果直接與高速的單片機相連時,會浪費大量的時間,可以考慮在單片機和液晶顯示器中間加入FPGA,由FPGA直接驅(qū)動和控制液晶顯示器。液晶顯示模塊框圖如圖3所示。

單片機將字庫/圖形庫內(nèi)的圖形或文字數(shù)據(jù)以及這些數(shù)據(jù)在液晶上所顯示的位置信息傳送給由FPGA芯片構(gòu)成的液晶控制IP核。由于LCD是慢速設(shè)備,單片機發(fā)送至LCD控制器的顯示數(shù)據(jù)信息的速度通常大于LCD顯示更新速度,因此需將這些數(shù)據(jù)和信息送入數(shù)據(jù)存儲器中緩存。由于FPGA芯片的片內(nèi)RAM容量有限,系統(tǒng)中外擴了1片RAM作為顯示數(shù)據(jù)緩沖器。由FPGA芯片構(gòu)成的顯示控制IP核需讀取外擴顯示RAM中的數(shù)據(jù),再通過顯示驅(qū)動電路按字節(jié)送至LCD進行顯示:因此在所設(shè)計的顯示驅(qū)動電路中設(shè)計了一個雙端口RAM,既能將顯示數(shù)據(jù)緩存器中的顯示數(shù)據(jù)寫入雙端口RAM,同時又能將雙端口RAM中的數(shù)據(jù)讀出,再將數(shù)據(jù)送至LCD數(shù)據(jù)接口。

2.3 SRAM模塊

C8051F020內(nèi)部有位于外部數(shù)據(jù)存儲器空間的4 096字節(jié)的片上RAM,還有外部數(shù)據(jù)存儲器接口EMIF,可用于訪問片外存儲器和存儲器映射的I/O器件。外部數(shù)據(jù)存儲器接口EMIF可配置到低I/O端口P0~P3,也可配置到高I/O端口P4~P7。而且,既可以配置為數(shù)據(jù)、地址復用方式,也可以配置為非復用方式。若要節(jié)省端口I/O,可采用數(shù)據(jù)、地址復用方式,能節(jié)省8根端口線,但是速度較慢,若要提高速度,則可

以采用非復用方式。

2.3.1 配置外部存儲器接口的步驟

1)將EMIF選到低端口(P3~P0)或選到高端口(P7~P4)。

2)選擇復用方式或非復用方式。

3)選擇存儲器模式(只用片內(nèi)存儲器、不帶塊選擇的分片方式、帶塊選擇的分片方式或只用片外存儲器)。

4)設(shè)置與片外存儲器或外設(shè)接口的時序。

5)選擇所需要的相關(guān)端口的輸出方式。

在本系統(tǒng)中考慮到(28051F020單片機的PO~P3口大部分為功能復用引腳,為使單片機的資源得到最大的開發(fā),將單片機的高端I/O口,即P4~P7接入FPGA,并通過FPGA對RAM進行訪問。將單片機配置為高端口(P4~P7)、地址/數(shù)據(jù)總線分時復用方式,F(xiàn)PGA控制RAM的片選、讀/寫等操作,其中注意FPGA、單片機、RAM的時序統(tǒng)一問題。

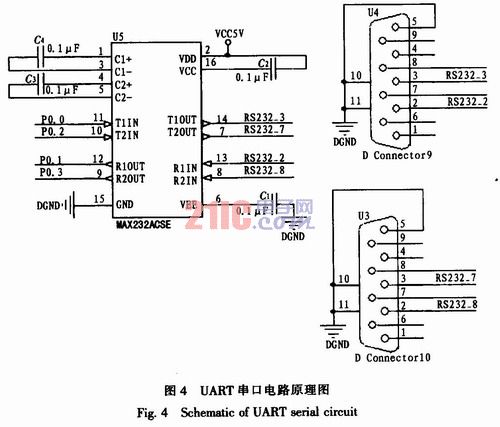

2.4 UART串口

UART是一種通用串行數(shù)據(jù)總線,該總線雙向通信,可以實現(xiàn)全雙工傳輸和接收。在嵌入式設(shè)計中,UART用來與PC進行通信,包括與監(jiān)控調(diào)試器和其他器件,如EEPROM通信。

UART首先將并行數(shù)據(jù)轉(zhuǎn)換成串行數(shù)據(jù)來發(fā)送。消息幀從一個低位起始位開始,后面是若干數(shù)據(jù)位,一個可用的奇偶校驗位和一個高位停止位。接收器發(fā)現(xiàn)開始位時它就知道數(shù)據(jù)準備發(fā)送,并嘗試與發(fā)送器時鐘頻率同步。在接收過程中,UART從消息幀中去掉起始位和結(jié)束位,對進來的字節(jié)進行奇偶校驗,并將數(shù)據(jù)字節(jié)從串行轉(zhuǎn)換成并行。UART也產(chǎn)生額外的信號來指示發(fā)送和接收的狀態(tài)。例如,如果產(chǎn)生一個奇偶錯誤,UART就置位奇偶標志。

C805lF020單片機中有兩個增強型串行口:UART0和UARTl。所謂增強型是指,這兩個串口都具有幀錯誤檢測和通信地址硬件識別功能。它們都可以工作在全雙工異步方式或半雙工同步方式,并且支持多處理器通信。開發(fā)板外擴兩個增強型UART串口,實現(xiàn)單片機與PC機、單片機和單片機之間的通信。其電路連接如圖4所示。

2. 5 A/D和D/A模塊

C8051F020有一個片內(nèi)12位ADC(ADCO)和一個8位ADC(ADCl),通道輸入多路選擇開關(guān)和可編程增益放大器。

ADC的電壓基準可以在模擬電源電壓(AV+)和一個外部VREF引腳之間選擇。A/D轉(zhuǎn)換有4種啟動方式:軟件命令、定時器2溢出、定時器3溢出和外部信號輸入。這種靈活性允許用軟件事件、外部硬件信號或周期性的定時器溢出信號觸發(fā)轉(zhuǎn)換。轉(zhuǎn)換結(jié)束由一個狀態(tài)位指示,或者產(chǎn)生中斷(如果中斷被使能)。在轉(zhuǎn)換完成后,12位或8位轉(zhuǎn)換結(jié)果數(shù)據(jù)字被鎖存到兩個特殊功能寄存器中。這些數(shù)據(jù)字可以用軟件控制為左對齊或右對齊。

C805lF020內(nèi)部有兩個片內(nèi)12位電壓方式數(shù)/模轉(zhuǎn)換器(DAC)。每個DAC的輸出擺幅均為0 V到(VREF-1LSB),對應(yīng)的輸入碼范圍是Ox000到OxFFF。C8051F020的VREF引腳可以由內(nèi)部電壓基準或一個外部源驅(qū)動。如果使用內(nèi)部電壓基準,為了使DAC輸出有效,該基準必須被使能。

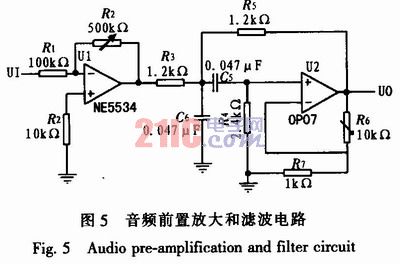

本文設(shè)計了利用A/D和D/A模塊進行簡單的語音信號的存儲和回放,基本思想是將模擬語音信號經(jīng)過前置放大和濾波電路的處理,通過模數(shù)轉(zhuǎn)換器A/D轉(zhuǎn)換成數(shù)字信號,再通過單片機控制存儲在存儲器中,回放時,由單片機控制將數(shù)據(jù)從存儲器中讀出,然后通過數(shù)模轉(zhuǎn)換器D/A轉(zhuǎn)換成模擬信號,經(jīng)放大在揚聲器或耳機上輸出語音。音頻前置放大和濾波電路如圖5所示。

3 結(jié)束語

本開發(fā)系統(tǒng)采用MCU+FPGA結(jié)構(gòu),單片機負責過程控制和數(shù)據(jù)處理,F(xiàn)PGA實現(xiàn)各種外設(shè)的接口,同時FPGA還可以為單片機提供存儲器和I/O口等資源。由于電路中具有數(shù)字部分和模擬部分,在PCB制板時特別注意抗干擾處理,例如加去耦電容、數(shù)字地和模擬地一點連接、數(shù)字電源和模擬電源隔離等措施。

需要注意的是,采樣后的數(shù)字語音信號由于數(shù)據(jù)量很大,為了節(jié)省存儲空間,可以采取相應(yīng)的編碼技術(shù)去除冗余度,回放的語音質(zhì)量性噪比(RSN)較高。系統(tǒng)采用3.3 V供電單片機,功耗降低50%左右。通過配置內(nèi)部寄存器和外部時鐘切換電路,可靈活配置系統(tǒng)時鐘。通過單片機內(nèi)部交叉開關(guān)的配置,設(shè)計者可以實現(xiàn)數(shù)字和模擬外設(shè)的引腳分配和器件的使能。經(jīng)過測試,各模塊均能夠達到設(shè)計要求,具有良好的可擴展性和穩(wěn)定性,適合作為電子設(shè)計大賽和電子愛好者的開發(fā)用板。