摘要:闡述基于三星ARM處理器S3C2410A和嵌入式操作系統(tǒng)Windows CE.net構(gòu)造微型工程地震儀的設(shè)計(jì)原理和實(shí)現(xiàn)方法。在現(xiàn)有工程地震儀的基礎(chǔ)上,結(jié)合嵌入式技術(shù)構(gòu)造攜帶方便、功耗低、體積小的微型工程地震儀,可以適應(yīng)不同的工作場(chǎng)合,滿足工程勘探的需要。

1 引言

隨著嵌入式微處理器和嵌入式操作系統(tǒng)的發(fā)展,嵌入式系統(tǒng)在通訊、控制和消費(fèi)電子等諸多領(lǐng)域得到了廣泛的應(yīng)用。嵌入式系統(tǒng)通常是面向特定應(yīng)用的嵌入式CPU,與通用型的最大不同就是嵌入式CPU大多工作在為特定用戶群設(shè)計(jì)的系統(tǒng)中,它通常都具有低功耗、體積小、集成度高等特點(diǎn),能夠把通用CPU中許多由板卡完成的任務(wù)集成在芯片內(nèi)部,從而有利于嵌入式系統(tǒng)設(shè)計(jì)趨于小型化,以動(dòng)能力增強(qiáng),與網(wǎng)絡(luò)的耦合也越來越緊密。

本文利用ARM嵌入式系統(tǒng)構(gòu)造微型化的工程地震儀雛形,以滿足特定條件的工作需要,降低功耗,節(jié)省能源以延長(zhǎng)工作時(shí)間,減小儀器尺寸和重量,使儀器更為輕便。

2 現(xiàn)有工程地震儀簡(jiǎn)介

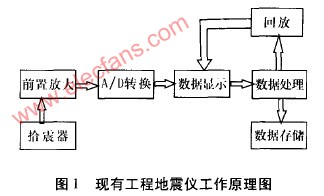

工程地震儀應(yīng)用于地基、路基與基礎(chǔ)工程檢測(cè);隧道工程檢測(cè);大中型水庫的運(yùn)行觀測(cè);橋梁工程檢測(cè);環(huán)境與地質(zhì)災(zāi)害檢測(cè)與評(píng)價(jià)等工程領(lǐng)域的地震檢測(cè)任務(wù)l2 。一般來講工程地震儀器利用錘擊、電火花或爆炸等作為激發(fā)震源,硬件上由前置放大器,數(shù)據(jù)采集卡,A/D轉(zhuǎn)換器,工控機(jī)(便攜式微機(jī))等部分組成。而數(shù)據(jù)采集,數(shù)據(jù)處理,分析軟件都存儲(chǔ)在工控機(jī)內(nèi),可以隨時(shí)處理現(xiàn)場(chǎng)所采集的原始數(shù)據(jù),發(fā)現(xiàn)問題及時(shí)處理。其功能一般有:瞬態(tài)多點(diǎn)端雷波勘探淺層反射測(cè)量淺層折射測(cè)量波速(剪切波)測(cè)量多波高密度地震映像樁基檢測(cè)土建工程質(zhì)量檢測(cè)場(chǎng)地常時(shí)微動(dòng)測(cè)量震動(dòng)爆破測(cè)量。如圖1 所示

其中,數(shù)據(jù)的顯示,數(shù)據(jù)的處理和存儲(chǔ)都是用工業(yè)控制微機(jī)來完成的,下面是一款典型的現(xiàn)有工程地震儀器工業(yè)控制微機(jī)的硬件配置:

CPU :PIII 500MHz

內(nèi)存:128MB

硬盤:不小于40GB

光驅(qū):內(nèi)置

顯示屏:800×600點(diǎn)陣VGA液晶顯示屏(TFT真彩)

輸入設(shè)備:觸摸屏輸入、精致小鍵盤、光電鼠標(biāo)

接口:雙串一并、雙USB口、鼠標(biāo)口、鍵盤口等標(biāo)準(zhǔn)口

移動(dòng)存儲(chǔ):256M電子U盤

現(xiàn)有工程地震儀由于工控機(jī)功耗較高,體積尺寸大,野外攜帶不很方便,尤其是當(dāng)野外工作需要電池支持時(shí),受功耗的影響工作時(shí)間可能受一定的限制。對(duì)于某些特定場(chǎng)合,如煤礦井下作業(yè)時(shí)要考慮到防爆因素,必須在儀器外裝加防爆外殼,而防爆因素與功耗,體積等密切相關(guān),這便要求有相對(duì)功耗小,體積重量小的微型工程地震儀的出現(xiàn)。

3 系統(tǒng)硬件設(shè)計(jì)

3.1 工作原理

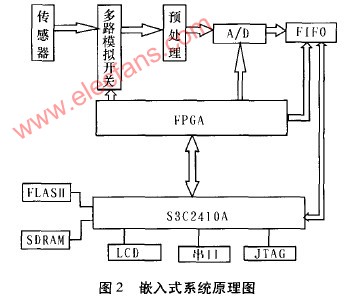

系統(tǒng)硬件主要分為ARM處理器模塊、協(xié)處理器FPGA模塊、預(yù)處理和A/D模塊、通用外設(shè)模塊4個(gè)部分,ARM處理器和現(xiàn)場(chǎng)可編程門陣列(FP.GA)共同組成監(jiān)控系統(tǒng)的核心處理單元。現(xiàn)場(chǎng)勘探檢測(cè)時(shí),可利用爆炸的方式作為激發(fā)震源,當(dāng)一次爆炸啟動(dòng)后,傳感器信號(hào)通過模擬開關(guān),先經(jīng)過前置放大和濾波等預(yù)處理,獲取符合A/D轉(zhuǎn)換芯片要求的信號(hào),經(jīng)過A/D轉(zhuǎn)換,進(jìn)入FIFO,然后由嵌入式微處理器讀取并處理數(shù)據(jù),然后將數(shù)據(jù)存儲(chǔ)到SIM卡或USB存儲(chǔ)設(shè)備中。在A/D轉(zhuǎn)換模塊中,采用多路模擬開關(guān),可完成大數(shù)量點(diǎn)的數(shù)據(jù)采集。FPGA是整個(gè)系統(tǒng)的控制中心,控制采集通道的切換,A/D轉(zhuǎn)換芯片的啟停,轉(zhuǎn)換后的數(shù)據(jù)在FIFO中的存放以及向主處理器$3C2410A產(chǎn)生中斷請(qǐng)求讀取FIFO中的數(shù)據(jù)。如圖2所示。

3.2 硬件介紹

3.2.1 協(xié)處理器模塊

系統(tǒng)的協(xié)處理器采用Xilinx公司的FPGA,型號(hào)為SPARTANIIE XC2SIOOE。該芯片共有2700個(gè)邏輯單元,10萬個(gè)邏輯門,片內(nèi)塊RAM為40KB。其具體實(shí)現(xiàn)以下功能:

· A/D模塊讀/寫時(shí)序控制;

· 生成FIFO,其主要功能是存儲(chǔ)經(jīng)A/D編碼的數(shù)據(jù):

· 提供ARM處理器控制信號(hào)。

FPGA芯片分4部分來實(shí)現(xiàn)上述功能:

(1)內(nèi)部控制信號(hào)產(chǎn)生器

FPGA對(duì)50 MHz時(shí)鐘分頻產(chǎn)生A/D芯片采樣時(shí)鐘Sampleclk和ARM處理器外部時(shí)鐘Sysclk;Sysclk經(jīng)鎖相環(huán)電路(PLL)后產(chǎn)生ARM處理器工作所需的時(shí)鐘信號(hào) 。

(2)ARM控制器

提供ARM處理器正常工作所必須的各種控制信號(hào);實(shí)現(xiàn)ARM處理器地址總線、數(shù)據(jù)總線和外部中斷信號(hào)接入 。

(3)A/D控制器

控制A/D模塊的數(shù)據(jù)轉(zhuǎn)換。產(chǎn)生A/D轉(zhuǎn)換起始信號(hào)(/HOLD),檢測(cè)數(shù)據(jù)轉(zhuǎn)換完成信號(hào)(/EOC),產(chǎn)生FIFO寫入信號(hào),實(shí)現(xiàn)數(shù)據(jù)轉(zhuǎn)換通道選擇。

(4)FIFO存儲(chǔ)器

生成FIFO,完成A/D轉(zhuǎn)換數(shù)據(jù)的存儲(chǔ)。

3.2.2 ARM處理器模塊

ARM 處理器模塊由FLASH、SDRAM 和s3C2410共同構(gòu)建。系統(tǒng)選用Samsung公司的K9F1208UOA構(gòu)建8位FLASH 存儲(chǔ)器系統(tǒng)。K9F1208UOA單片容量為64 MB;選用兩片單片容量32 MB。數(shù)據(jù)寬度為16位HY57V561620CT,并聯(lián)構(gòu)建32位SDRAM存儲(chǔ)器系統(tǒng),共64 MB的SDRAM空問可以滿足嵌入式操作系統(tǒng)和各種復(fù)雜算法的運(yùn)行要求。ARM處理器對(duì)各模塊的控制則是通過底層驅(qū)動(dòng)控制協(xié)處理器FPGA產(chǎn)生各種控制信號(hào)來實(shí)現(xiàn)。

3.2.3 預(yù)處理和A/D模塊

傳感器傳播的模擬信號(hào)比較微弱,需要經(jīng)過前置放大等預(yù)處理后方具備數(shù)據(jù)有效性。預(yù)處理主要是由前置放大電路構(gòu)成,A/D模塊主要由模擬開關(guān)和A/D轉(zhuǎn)換芯片構(gòu)成。模擬開關(guān)采用AD公司的AD7506,可實(shí)現(xiàn)12通道數(shù)據(jù)采集。A/D轉(zhuǎn)換芯片采用CIRRUS公司的CS5381,是120dB、192kHz高性能立體聲24位Σ 一△ A/D變換器,內(nèi)置雙極性電路構(gòu)成的混合集成轉(zhuǎn)換顯片,具有外接元件少,功耗低,精度高等特點(diǎn),并且具有自動(dòng)校零和自動(dòng)極性轉(zhuǎn)換功能,只需外接少量的阻容件即可構(gòu)成一個(gè)完整的A/D轉(zhuǎn)換器。

3.2.4 接口和顯示模塊

包括常用的接口和顯示器件。接口包括常用的串口等,用以進(jìn)行數(shù)據(jù)的外部存儲(chǔ)。顯示模塊主要包括構(gòu)成操作的LCD和觸摸屏等外圍顯示設(shè)備。

4 嵌入式系統(tǒng)軟件設(shè)計(jì)

軟件部分分為FPGA控制程序和ARM處理器兩部分,F(xiàn)PGA用VHDL來設(shè)計(jì),基于s3C2410A的軟件設(shè)計(jì)主要任務(wù)有數(shù)據(jù)采集的驅(qū)動(dòng)程序,操作系統(tǒng)的移植以及上層應(yīng)用軟件的設(shè)計(jì)。嵌入式操作系統(tǒng)應(yīng)用WinCe.net,上層應(yīng)用軟件開發(fā)使用Embedded Visual C++,底層驅(qū)動(dòng)和ARM處理器的調(diào)試則使用c語言。

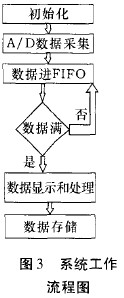

系統(tǒng)開始工作后ARM處理器和FPGA協(xié)處理器中的FIFO開始初始化。經(jīng)A/D轉(zhuǎn)換后的數(shù)據(jù)存入對(duì)應(yīng)的FIFO中。FIFO中的數(shù)據(jù)容量達(dá)到一定限度即產(chǎn)生巾斷,ARM處理器中的主程序產(chǎn)生中斷等待線程;一旦中斷產(chǎn)生則進(jìn)入中斷服務(wù)程序,讀取數(shù)據(jù),之后進(jìn)入ARM系統(tǒng)進(jìn)行相應(yīng)的處理,然后存儲(chǔ)到存儲(chǔ)設(shè)備。如圖3所示。

4.1 嵌入式操作系統(tǒng)WindowsCE.net的裁減

使用集成開發(fā)環(huán)境Platform Builder根據(jù)提示完成操作系統(tǒng)鏡像的定制、編譯與調(diào)試工作,并可在此環(huán)境巾進(jìn)行應(yīng)用軟件、驅(qū)動(dòng)程序的開發(fā)。在ARM中植入Windows CE.net平臺(tái),首先根據(jù)目標(biāo)設(shè)備的硬件配置及需要,對(duì)Windows CE.net進(jìn)行基本定制,開發(fā)并安裝驅(qū)動(dòng)程序,增加必要的特性,生成鏡像文件,通過JTAG將bootloader寫入flash后,通過網(wǎng)卡將鏡像文件下載到目標(biāo)設(shè)備中,進(jìn)行調(diào)試 同時(shí)要導(dǎo)出SDK,以備后面用EVC開發(fā)應(yīng)用程序。

4.2 數(shù)據(jù)采集驅(qū)動(dòng)程序

在數(shù)據(jù)采集中,主要對(duì)外部I/0口的訪問,Wince的BSP都實(shí)現(xiàn)WRITE—PORT—UCHAR和READ— PORT— UCHAR函數(shù)。訪問方式采用中斷方式。WinCE把中斷處理分為兩部分中斷服務(wù)例行程序ISR和中斷服務(wù)線程,用戶的中斷處理主要在IST中完成 。。這里采用基于中斷方式的非標(biāo)準(zhǔn)驅(qū)動(dòng),要實(shí)現(xiàn)兩個(gè)步驟:編寫中斷服務(wù)線程IST和注冊(cè)中斷服務(wù)線程。中斷信號(hào)由FIFO經(jīng)FPGA不斷產(chǎn)生,每發(fā)生一次中斷,運(yùn)行在核心態(tài)的中斷服務(wù)例行程序就調(diào)用一次IST。

4.3 中斷控制

系統(tǒng)如果對(duì)A/D轉(zhuǎn)換數(shù)據(jù)采用實(shí)時(shí)讀取的方式,則必然導(dǎo)致ARM處理器工作效率較低,所以在電路設(shè)計(jì)時(shí)采用中斷方式。A/D模塊輸出數(shù)據(jù)以循環(huán)方式分別寫入FIFO中。一旦FIFO中可使用數(shù)據(jù)容量減小到一定限度則產(chǎn)生中斷,ARM處理器進(jìn)入中斷服務(wù)程序并讀取FIFO中的數(shù)據(jù)。

4.4 上層應(yīng)用軟件

上層應(yīng)用軟件的開發(fā)包含以下模塊:

數(shù)據(jù)采集系統(tǒng):實(shí)施采集的控制和監(jiān)測(cè)。

數(shù)據(jù)處理系統(tǒng):簡(jiǎn)單處理采集到的數(shù)據(jù),如數(shù)字濾波等。

圖形顯示系統(tǒng):將采集到的數(shù)據(jù)以波形的形式顯示在顯示儀器L。

數(shù)據(jù)存儲(chǔ)系統(tǒng):構(gòu)造數(shù)據(jù)存儲(chǔ)系統(tǒng),使數(shù)據(jù)以文件形式存入存儲(chǔ)設(shè)備(FLASH閃存,USB外設(shè),存儲(chǔ)卡等),硬件上還要求支持USB通用串行總線,支持設(shè)備的熱插拔,傳輸速度快.結(jié)構(gòu)簡(jiǎn)單。

5 結(jié)束語

本文所研制的微型工程地震儀系統(tǒng)綜合利用了嵌入式系統(tǒng)設(shè)計(jì)技術(shù),與傳統(tǒng)地震勘探設(shè)備相比大大提高了設(shè)備的便攜性和節(jié)能性。同時(shí),該系統(tǒng)注重?cái)?shù)據(jù)快速存儲(chǔ)的研究,并在實(shí)際系統(tǒng)中加以應(yīng)用。本系統(tǒng)在設(shè)計(jì)時(shí)充分考慮了電路的靈活性和通用性,可根據(jù)不同的功能要求編寫相應(yīng)的VHDL語言程序。系統(tǒng)所使用的Windows CE操作系統(tǒng)可以任意裁剪,這對(duì)于功能的轉(zhuǎn)換很有幫助。本系統(tǒng)已研制完畢,現(xiàn)處于現(xiàn)場(chǎng)實(shí)驗(yàn)階段。隨著計(jì)算機(jī)技術(shù)和網(wǎng)絡(luò)技術(shù)的發(fā)展,嵌入式微處理器的性能的提高,嵌入式系統(tǒng)將在工業(yè)控制領(lǐng)域得到更廣泛的應(yīng)用。