抖動(dòng)和SNR詳解

德州儀器

摘要: 您在使用一個(gè)高速模數(shù)轉(zhuǎn)換器(ADC)時(shí),總是期望性能能夠達(dá)到產(chǎn)品說(shuō)明書載明的信噪比(SNR)值,這是很正常的事情,。

Abstract:

Key words :

您在使用一個(gè)高速模數(shù)轉(zhuǎn)換器 (ADC) 時(shí),總是期望性能能夠達(dá)到產(chǎn)品說(shuō)明書載明的信噪比 (SNR) 值,,這是很正常的事情。您在測(cè)試 ADC 的 SNR 時(shí),,您可能會(huì)連接一個(gè)低抖動(dòng)時(shí)鐘器件到轉(zhuǎn)換器的時(shí)鐘輸入引腳,,并施加一個(gè)適度低噪的輸入信號(hào),。如果您并未從您的轉(zhuǎn)換器獲得 SNR 產(chǎn)品說(shuō)明書標(biāo)稱性能,則說(shuō)明存在一些噪聲誤差源,。如果您確信您擁有低噪聲輸入信號(hào)和一種較好的布局,,則您的輸入信號(hào)頻率以及來(lái)自您時(shí)鐘器件抖動(dòng)的組合可能就是問(wèn)題所在。您會(huì)發(fā)現(xiàn)“低抖動(dòng)”時(shí)鐘器件適合于大多數(shù) ADC 應(yīng)用,。但是,,如果 ADC 的輸入頻率信號(hào)和轉(zhuǎn)換器的 SNR 較高,則您可能就需要改善您的時(shí)鐘電路,。

低抖動(dòng)時(shí)鐘器件充其量有宣稱的 1 微微秒抖動(dòng)規(guī)范,,或者您也可以從一個(gè) FPGA生成同樣較差的時(shí)鐘信號(hào)。這會(huì)使得高速 ADC 產(chǎn)生 SNR 誤差問(wèn)題包括 ADC 量化噪聲,、差分非線性 (DNL) 效應(yīng),、有效轉(zhuǎn)換器內(nèi)部輸入噪聲和抖動(dòng)。利用方程式1 中的公式,,您可以確定抖動(dòng)是否有問(wèn)題,,公式給出了外部時(shí)鐘和純 ADC 抖動(dòng)產(chǎn)生的 ADC SNR 誤差。

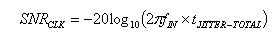

方程式 1

方程式 1

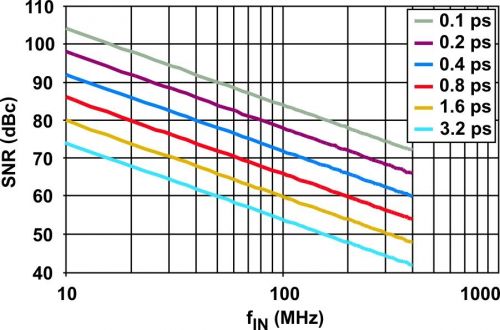

在該方程式中,,fIN 為轉(zhuǎn)換器的輸入信號(hào)頻率,。另外,tJITTER-TOTAL 為時(shí)鐘信號(hào)和ADC時(shí)鐘輸入電路的 rms 抖動(dòng),。請(qǐng)注意,,fIN 并非時(shí)鐘頻率 (fCLK)。外部時(shí)鐘器件到 ADC 的 1 微微秒抖動(dòng)適合于一些而不是所有高速 ADC 應(yīng)用,,如圖1 所示,。

圖1抖動(dòng)產(chǎn)生的SNR 為輸入信號(hào)的函數(shù)

方程式1 讓您能夠計(jì)算出特定 ADC 的要求時(shí)鐘抖動(dòng)估計(jì)值。例如,,一個(gè) 70 dB SNR 的 ADC,輸入信號(hào)為 100 MHz,,您可以計(jì)算得到 tJITTER_TOTAL 的值為 503 微微秒,。如果輸入 ADC 孔徑抖動(dòng)為 150 微微秒,則由方程式2 可得到一個(gè)較高的外部時(shí)鐘抖動(dòng)要求估計(jì)值,。

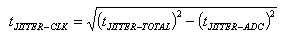

方程式 2

方程式 2

在方程式 2 中,,tJITTER-CLK為注入 ADC 時(shí)鐘的抖動(dòng),而 tJITTER-ADC為 ADC 的孔徑抖動(dòng),、時(shí)鐘振幅和斜率,。繼續(xù)我們的估算,我們讓 tJITTER-ADC 只與 ADC 的 150 微微秒內(nèi)部抖動(dòng)相等,,并忽略時(shí)鐘振幅和斜率的影響,。利用方程式2,,tJITTER-CLK 的高估值為 480 微微秒。

在本文中,,我們只初步研究了改善高速 ADC 時(shí)鐘信號(hào)背后存在的一些問(wèn)題,。我們需要更多地關(guān)注時(shí)鐘振幅和斜率,因?yàn)樗鼈冇绊懴到y(tǒng)抖動(dòng),。另外,,我們還需要知道如何實(shí)施低抖動(dòng)時(shí)鐘電路的硬件部分。

在本文介紹的第二種時(shí)鐘設(shè)計(jì)之中,,您需要認(rèn)真關(guān)注幾件事情,。時(shí)鐘抖動(dòng)在 ADC 輸入頻率和實(shí)際時(shí)鐘抖動(dòng)方面影響 ADC 的 SNR 性能。另外,,不要總是相信時(shí)鐘器件廠商,!在您轉(zhuǎn)向產(chǎn)品以前,請(qǐng)使用 ADC 廠商提供的評(píng)估板來(lái)測(cè)試您的時(shí)鐘源,。您會(huì)對(duì)最終結(jié)果更為欣喜,。

參考文獻(xiàn):

- 《高速數(shù)據(jù)轉(zhuǎn)換器時(shí)鐘》,作者:Eduardo Bartolome,、Vineet Mishra,、Goutam Dutta 以及 David Smith,模擬應(yīng)用期刊,,TI,,slyt075,1Q05,。

- 《使用高 IF 采樣 A/D 轉(zhuǎn)換器超越基帶頻率》,,作者:Chuck Sanna,Planet Analog,,2007 年 9 月 5 日,。

- 視頻:《高速 ADC 時(shí)鐘》,作者:Lin Wu,,TI,,2008 年。

此內(nèi)容為AET網(wǎng)站原創(chuàng),,未經(jīng)授權(quán)禁止轉(zhuǎn)載,。