大型LED 顯示系統(tǒng)是隨著計(jì)算機(jī)及相關(guān)微電子、光電子技術(shù)的迅猛發(fā)展而形成的一種電子廣告媒體,它利用發(fā)光二極管構(gòu)成的點(diǎn)陣模塊或像素單元組成大面積顯示屏幕,主要用于顯示字符、圖像等信息。它采用低電壓掃描驅(qū)動,具有: 耗電少、壽命長、成本低、亮度高、故障少、視角大、可視距離遠(yuǎn)等優(yōu)點(diǎn)。隨著LED材料技術(shù)和工藝的提升,大型LED顯示系統(tǒng)以突出的優(yōu)勢成為平板顯示的主流產(chǎn)品之一,廣泛應(yīng)用在如證券交易,機(jī)場航班,港口,車站等場合,在信息顯示領(lǐng)域得到廣泛應(yīng)用。

1 系統(tǒng)結(jié)構(gòu)與原理

大型LED顯示系統(tǒng)一般分為顯示驅(qū)動模塊和主控板兩部分。

1.1 顯示模塊

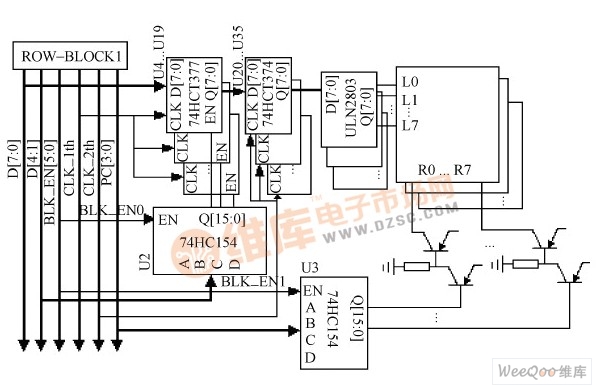

大型LED顯示系統(tǒng)是利用人眼視覺特點(diǎn)采用逐行掃描和列驅(qū)動方式以節(jié)省硬件開支,本系統(tǒng)采用1 /16逐行掃描方式,所以整個(gè)顯示屏被分為16 行同名行,顯示模塊原理圖如圖1所示。

圖1 顯示模塊原理圖。

每個(gè)顯示模塊為1個(gè)64 ×32的小點(diǎn)陣屏,分為兩部分,上下各16 行,每部分有8 組列數(shù)據(jù)鎖存器。上下兩部分復(fù)用1個(gè)4~16譯碼器U3,選通驅(qū)動1 /16逐行掃描顯示,并需要16組列驅(qū)動鎖存器鎖存列顯示數(shù)據(jù)。采用并行總線數(shù)據(jù)傳輸方式時(shí),需要1個(gè)4~16譯碼器U2選通使能列鎖存器。在點(diǎn)陣數(shù)據(jù)刷新時(shí),需要使用兩級鎖存器鎖存列顯示數(shù)據(jù),否則會出現(xiàn)顯示拖尾現(xiàn)象。本次正在顯示的數(shù)據(jù)存在第二級鎖存器中,主控板對屏端第一級鎖存器寫下一行要顯示的數(shù)據(jù)進(jìn)行列數(shù)據(jù)刷新,當(dāng)下一行要顯示的數(shù)據(jù)傳輸完畢后,一起鎖存到第二級鎖存器輸出并選通驅(qū)動下一行顯示。采用并行總線方式下二級鎖存器仍比數(shù)據(jù)串行傳輸再轉(zhuǎn)成并行輸出的方案經(jīng)濟(jì)。

顯示模塊與模塊之間橫向級聯(lián)時(shí),運(yùn)用錯位級聯(lián)的思想,使其具有良好的通用性和可嵌入性。選通線每到一級時(shí)就會錯位一次并傳到下一級,總是使第一根選通線BLK_EN0作第一級列鎖存器譯碼器的使能控制線,n根選通線就能依次選通n級橫向級聯(lián)模塊,這樣就可以用相同的顯示模塊任意組合成橫向級聯(lián)的條屏。

運(yùn)用錯位級聯(lián)思想,使橫向級聯(lián)的顯示模塊上的第一級鎖存器的譯碼器U2 能夠依次選通,該譯碼器又能依次選通第一級列數(shù)據(jù)鎖存器,這樣橫向級聯(lián)屏上的第一級列數(shù)據(jù)鎖存器就能看成一段連續(xù)的存儲單元,這是使用DMA 并行數(shù)據(jù)傳輸控制的基礎(chǔ)。

1.2 主控電路與LED屏的接口設(shè)計(jì)

本顯示系統(tǒng)選用基于ARM7TDM I內(nèi)核并帶有內(nèi)部DMA控制器的S3C44B0X作主控制器,使其工作在ARM狀態(tài),并使用16位總線。由于把LED屏虛擬的視為一段連續(xù)的存儲單元,故為其分配地址空間0x2000000~0x4000000。

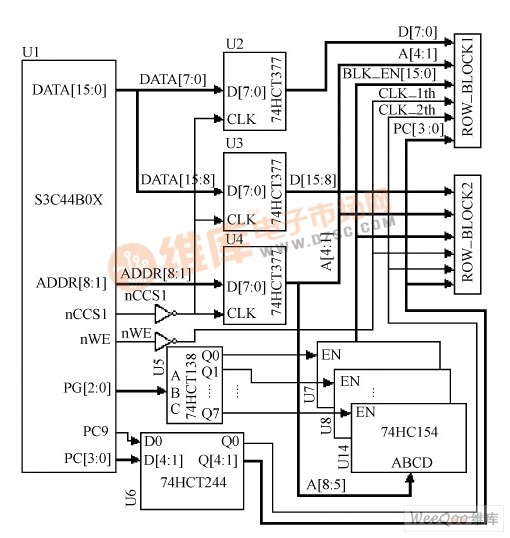

主控板與LED屏接口電路原理圖如圖2所示。

一個(gè)大型LED顯示屏的結(jié)構(gòu)可分為縱向級聯(lián)和橫向級聯(lián),這種結(jié)構(gòu)類似于一個(gè)三維數(shù)組。假設(shè)一個(gè)三維數(shù)組LED [ i ] [ j] [ k ] ,其中:

i = 0,1,2,……,m 表示LED屏縱向級聯(lián)級的序號。

j = 0,1,2,……,n 表示LED屏橫向級聯(lián)級的序號。

k = 0,1,2,……,16 表示顯示模塊上16 個(gè)第一級列數(shù)據(jù)鎖存器的序號。

由于系統(tǒng)使用16位并行總線數(shù)據(jù)傳輸方式,并將LED屏視為一段連續(xù)的存儲單元,故使用A [ 4∶1 ]

作顯示模塊上選通第一級列數(shù)據(jù)鎖存器譯碼器(圖1中U2) 的譯碼輸入,即為三維數(shù)組的k變量; 使用A [ 8 ∶5 ] 作選通橫向級聯(lián)顯示模塊的譯碼器(圖2中U14) 譯碼輸入,即為三維數(shù)組的j變量;由于LED 屏要具有良好的靈活性,又由于采用DMA傳輸數(shù)據(jù)要求點(diǎn)陣碼存放順序的技術(shù)要求,縱向級聯(lián)級選通不滿足使用地址總線譯碼選通的條件,所以使用S3C44B0X的PG [ 2∶0 ] 作縱向級聯(lián)級選通譯碼器的譯碼輸入,即三維數(shù)組的i變量。

圖2 主控板與LED顯示屏接口電路原理圖。

由于地址和數(shù)據(jù)總線上的狀態(tài)不斷變化,所以在對LED屏進(jìn)行寫操作時(shí),地址和數(shù)據(jù)信號應(yīng)進(jìn)行鎖存,主控板上分別使用U2、U3和U4鎖存對LED寫操作時(shí)的地址和數(shù)據(jù)總線的狀態(tài)。LED屏分配首址為0x2000000,當(dāng)對其進(jìn)行寫操作時(shí),S3C44B0X的nGCSl和nWE腳會出現(xiàn)可編程控制時(shí)延的有效低電平。nGCSl經(jīng)一個(gè)非門作U2、U3和U4的鎖存使能控制信號,保證僅在對LED屏訪問時(shí),地址和數(shù)據(jù)總線上的信號才被鎖存。nWE經(jīng)一個(gè)非門作屏端第一級列數(shù)據(jù)鎖存器(圖1中U4~U19) 的鎖存使能控制信號,保證只有當(dāng)刷新數(shù)據(jù)穩(wěn)定出現(xiàn)在列數(shù)據(jù)鎖存其輸入端時(shí)才被鎖存。S3C44B0X的PC I0作所有屏端第二級鎖存器(圖1中U20~U35) 的鎖存使能控制信號線; S3C44BOX的PC [ 3∶0 ] 作16行驅(qū)動譯碼器(圖1中U3) 的譯碼輸入。由于數(shù)據(jù)傳輸時(shí)只需要主控板對LED屏輸出控制,不需要信號反饋,所以接口電路采用廉價(jià)的5V供電的HCT電路芯片方案,就可滿足主控芯片313V到LED屏5V的邏輯電平轉(zhuǎn)換。

在DMA傳輸數(shù)據(jù)時(shí),更關(guān)心的是DMA的寫操作,時(shí)序如圖3所示。t1時(shí)刻DMA寫操作開始,地址和數(shù)據(jù)總線上出現(xiàn)LED屏相應(yīng)位置的地址和刷新數(shù)據(jù); t2時(shí)刻nGCS1引腳出現(xiàn)有效低電平,地址和數(shù)據(jù)總線上的數(shù)據(jù)被鎖存到U2~U4并輸出; t3時(shí)刻nWE引腳出現(xiàn)有效低電平,U2~U4的輸出數(shù)據(jù)被鎖存到屏端第一級列數(shù)據(jù)鎖存器并輸出。這樣主控制器就完成了一次列數(shù)據(jù)的刷新。

圖3 DMA的寫操作時(shí)序圖。

2 軟件設(shè)計(jì)

2.1 LED屏顯示程序設(shè)計(jì)

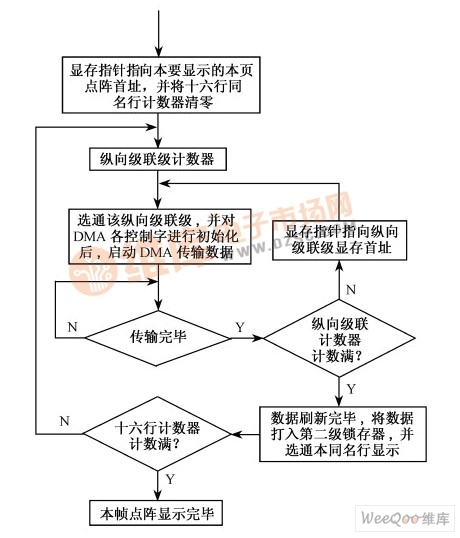

由于使用了S3C44B0X內(nèi)部DMA控制器進(jìn)行數(shù)據(jù)的傳輸與控制,顯示程序得到很大簡化,程序流程如圖4所示。點(diǎn)陣碼的傳輸全由DMA 控制器完成,只需在啟動DMA數(shù)據(jù)傳輸前將點(diǎn)陣碼的首址、LED屏的首址及傳輸數(shù)據(jù)量的值分別賦給相應(yīng)的控制字后,啟動DMA 操作即可。完成所有本同名行點(diǎn)陣碼傳輸后,將刷新的數(shù)據(jù)鎖存到第二級列數(shù)據(jù)鎖存器輸出,并驅(qū)動本同名行顯示。這樣循環(huán)顯示16行同名行后就完成了一幀點(diǎn)陣顯示。

圖4 顯示程序流程圖。

2.2 點(diǎn)陣排序

由于LED 顯示模塊的電路結(jié)構(gòu)以及使用了16位并行總線和DMA 數(shù)據(jù)傳輸技術(shù),在顯示時(shí)點(diǎn)陣碼的排放順序,需要滿足如下要求:

(1) 16 位并行總線一次數(shù)據(jù)傳輸,即一次DMA寫操作傳輸兩個(gè)字節(jié)的點(diǎn)陣碼,低位和高位字節(jié)分別傳送到兩相鄰的縱向級聯(lián)模塊的同名行和同名列數(shù)據(jù)鎖存器中,因此相鄰的縱向級聯(lián)模塊的同名行和同名列點(diǎn)陣碼應(yīng)連續(xù)存放。

(2) 由于顯示模塊的第一級列數(shù)據(jù)鎖存器譯碼選通電路結(jié)構(gòu)和DMA 數(shù)據(jù)傳輸要求,對同一顯示模塊的上下兩部分的同名行點(diǎn)陣應(yīng)按列數(shù)據(jù)鎖存器的選通順序依次連續(xù)存放。

(3) 兩相鄰的縱向級聯(lián)級的一系列橫向級聯(lián)級應(yīng)按(1) 和(2) 原則進(jìn)行點(diǎn)陣碼排序。

(4) 各縱向級聯(lián)級依次按(1) 、(2) 、(3) 原則進(jìn)行點(diǎn)陣碼排序。

(5) 16行掃描顯示方式下,一個(gè)大型LED 屏分為16 行同名行,每一同名行按照( 1) 、( 2) 、(3) 、(4) 原則進(jìn)行點(diǎn)陣排序。

以一個(gè)128 ×64的點(diǎn)陣屏第一行同名行的數(shù)據(jù)排序?yàn)槔鐖D5所示,第一行同名行的點(diǎn)陣碼的存放順序應(yīng)依次為: a,b,……z,A,B,……Z,……。

圖5 128 ×64點(diǎn)陣屏第一行同名行的數(shù)據(jù)排序圖。

3 結(jié)論

使用并行總線DMA 數(shù)據(jù)傳輸技術(shù)簡化了LED顯示系統(tǒng)的軟硬件設(shè)計(jì),降低了系統(tǒng)成本,取得了很好的顯示質(zhì)量,在2211184MHz的系統(tǒng)時(shí)鐘下,512 ×256 (8m2 ) 單色點(diǎn)陣屏顯示幀頻達(dá)到250Hz,平均120ns傳送1個(gè)字節(jié),達(dá)到了使用單CPU系統(tǒng)代替多機(jī)系統(tǒng)控制LED顯示系統(tǒng)的目的。但為了使上一代的顯示驅(qū)動板仍能夠使用,點(diǎn)陣碼需要排序,顯示時(shí)只能使用頁面方式顯示,這樣在多頁動態(tài)滾屏顯示時(shí)需要大容量的存儲器。對于512 ×256單色點(diǎn)陣屏需要數(shù)十兆的容量,使用32 位ARM7TDMl內(nèi)核先進(jìn)控制器S3C44B0X和廉價(jià)的大容量SDRAM存儲器可以使該問題得到很好的解決。若使用針對DMA控制顯示設(shè)計(jì)的顯示驅(qū)動板顯示時(shí),點(diǎn)陣碼就不需要排序,一片數(shù)百KB 的SRAM就能滿足系統(tǒng)要求了。