0 引言

以往的直流電機(jī)調(diào)速系統(tǒng)通常采用單片機(jī)或DSP進(jìn)行控制,而單片機(jī)需要使用大量的外圍電路,且系統(tǒng)的可升級(jí)性差,如更換控制器,往往要對(duì)整個(gè)軟硬件進(jìn)行重新設(shè)計(jì),可重用性不高。而采用DSP作為主要控制器,如果碰到處理多任務(wù)系統(tǒng)時(shí),一片DSP不能勝任,這時(shí)就需要再擴(kuò)展一片DSP或者FPGA芯片來(lái)輔助控制,從而實(shí)行雙芯片控制模式。但這樣做,既增加了兩個(gè)處理器之間同步和通信的負(fù)擔(dān),又使系統(tǒng)實(shí)時(shí)性變壞,延長(zhǎng)系統(tǒng)開(kāi)發(fā)時(shí)間。基于以上此類(lèi)問(wèn)題,本文提出了采用Altera公司推出的NiosⅡ軟核來(lái)控制直流電機(jī)調(diào)速系統(tǒng),它的好處在于Ni-osⅡ?qū)儆谲浐颂幚砥鳎梢灾苯油ㄟ^(guò)軟件形式擴(kuò)展成雙核乃至多核,無(wú)需外加芯片;再者NiosⅡ軟核處理器和所有外圍電路可以集成到一片F(xiàn)PGA芯片上來(lái)實(shí)現(xiàn)整個(gè)直流電機(jī)控制系統(tǒng),這樣無(wú)疑大大減小了控制器體積和重量,設(shè)計(jì)人員也可以在短時(shí)間內(nèi)完成整個(gè)系統(tǒng)的制作,提高了工作效率。

本文利用Altera公司的FPGA芯片EP2C35F672C6作為系統(tǒng)控制器,采用數(shù)字PID算法對(duì)直流電機(jī)進(jìn)行PWM閉環(huán)調(diào)速控制。并且利用硬件描述語(yǔ)言(VHDL)自行設(shè)計(jì)、生成PWM模塊和測(cè)速模塊,最后通過(guò)實(shí)驗(yàn)驗(yàn)證了該系統(tǒng)的可行性。

1 系統(tǒng)硬件設(shè)計(jì)

1.1 系統(tǒng)總體設(shè)計(jì)方案

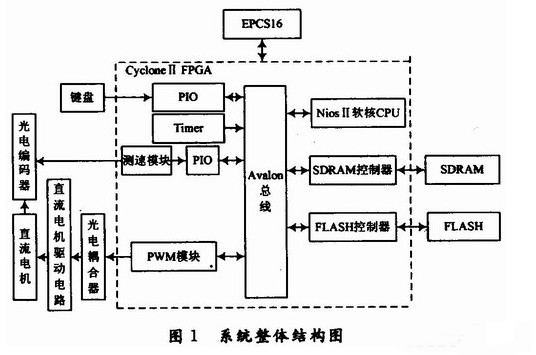

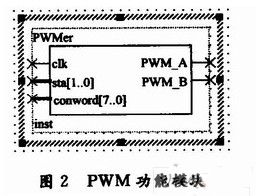

選用Altera公司的DE2開(kāi)發(fā)板作為開(kāi)發(fā)平臺(tái),采用SOPC技術(shù)通過(guò)在FPGA中植入嵌入式系統(tǒng)處理器NiosⅡ作為核心控制電路,利用FPGA中的可編程邏輯資源和IP軟核來(lái)構(gòu)成該嵌入式系統(tǒng)處理器的接口功能模塊,借助于Avalon總線,實(shí)現(xiàn)對(duì)外圍PWM模塊、測(cè)速模塊、SDRAM、鍵盤(pán)等硬件的控制,F(xiàn)PGA通過(guò)Avalon總線對(duì)輸入模塊和輸出等模塊進(jìn)行配置,整體功能框圖如圖1所示。

整個(gè)系統(tǒng)的主要工作流程如下:當(dāng)系統(tǒng)啟動(dòng)完成各單元初始化后,通過(guò)鍵盤(pán)輸入期望設(shè)定值,同時(shí)由光電編碼器采集實(shí)測(cè)轉(zhuǎn)速傳輸?shù)綔y(cè)速模塊,通過(guò)NiosⅡ處理器處理電機(jī)PID控制算法,并將計(jì)算后的數(shù)據(jù)傳輸給自定制的PWM模塊對(duì)其進(jìn)行閉環(huán)控制。最后在NiosⅡIDE上采集到實(shí)際輸出數(shù)據(jù),并通過(guò)Matlab軟件畫(huà)出控制曲線波形圖,最后對(duì)實(shí)驗(yàn)結(jié)果進(jìn)行分析。

0 引言

以往的直流電機(jī)調(diào)速系統(tǒng)通常采用單片機(jī)或DSP進(jìn)行控制,而單片機(jī)需要使用大量的外圍電路,且系統(tǒng)的可升級(jí)性差,如更換控制器,往往要對(duì)整個(gè)軟硬件進(jìn)行重新設(shè)計(jì),可重用性不高。而采用DSP作為主要控制器,如果碰到處理多任務(wù)系統(tǒng)時(shí),一片DSP不能勝任,這時(shí)就需要再擴(kuò)展一片DSP或者FPGA芯片來(lái)輔助控制,從而實(shí)行雙芯片控制模式。但這樣做,既增加了兩個(gè)處理器之間同步和通信的負(fù)擔(dān),又使系統(tǒng)實(shí)時(shí)性變壞,延長(zhǎng)系統(tǒng)開(kāi)發(fā)時(shí)間。基于以上此類(lèi)問(wèn)題,本文提出了采用Altera公司推出的NiosⅡ軟核來(lái)控制直流電機(jī)調(diào)速系統(tǒng),它的好處在于Ni-osⅡ?qū)儆谲浐颂幚砥鳎梢灾苯油ㄟ^(guò)軟件形式擴(kuò)展成雙核乃至多核,無(wú)需外加芯片;再者NiosⅡ軟核處理器和所有外圍電路可以集成到一片F(xiàn)PGA芯片上來(lái)實(shí)現(xiàn)整個(gè)直流電機(jī)控制系統(tǒng),這樣無(wú)疑大大減小了控制器體積和重量,設(shè)計(jì)人員也可以在短時(shí)間內(nèi)完成整個(gè)系統(tǒng)的制作,提高了工作效率。

本文利用Altera公司的FPGA芯片EP2C35F672C6作為系統(tǒng)控制器,采用數(shù)字PID算法對(duì)直流電機(jī)進(jìn)行PWM閉環(huán)調(diào)速控制。并且利用硬件描述語(yǔ)言(VHDL)自行設(shè)計(jì)、生成PWM模塊和測(cè)速模塊,最后通過(guò)實(shí)驗(yàn)驗(yàn)證了該系統(tǒng)的可行性。

1 系統(tǒng)硬件設(shè)計(jì)

1.1 系統(tǒng)總體設(shè)計(jì)方案

選用Altera公司的DE2開(kāi)發(fā)板作為開(kāi)發(fā)平臺(tái),采用SOPC技術(shù)通過(guò)在FPGA中植入嵌入式系統(tǒng)處理器NiosⅡ作為核心控制電路,利用FPGA中的可編程邏輯資源和IP軟核來(lái)構(gòu)成該嵌入式系統(tǒng)處理器的接口功能模塊,借助于Avalon總線,實(shí)現(xiàn)對(duì)外圍PWM模塊、測(cè)速模塊、SDRAM、鍵盤(pán)等硬件的控制,F(xiàn)PGA通過(guò)Avalon總線對(duì)輸入模塊和輸出等模塊進(jìn)行配置,整體功能框圖如圖1所示。

整個(gè)系統(tǒng)的主要工作流程如下:當(dāng)系統(tǒng)啟動(dòng)完成各單元初始化后,通過(guò)鍵盤(pán)輸入期望設(shè)定值,同時(shí)由光電編碼器采集實(shí)測(cè)轉(zhuǎn)速傳輸?shù)綔y(cè)速模塊,通過(guò)NiosⅡ處理器處理電機(jī)PID控制算法,并將計(jì)算后的數(shù)據(jù)傳輸給自定制的PWM模塊對(duì)其進(jìn)行閉環(huán)控制。最后在NiosⅡIDE上采集到實(shí)際輸出數(shù)據(jù),并通過(guò)Matlab軟件畫(huà)出控制曲線波形圖,最后對(duì)實(shí)驗(yàn)結(jié)果進(jìn)行分析。

1.2 PWM模塊

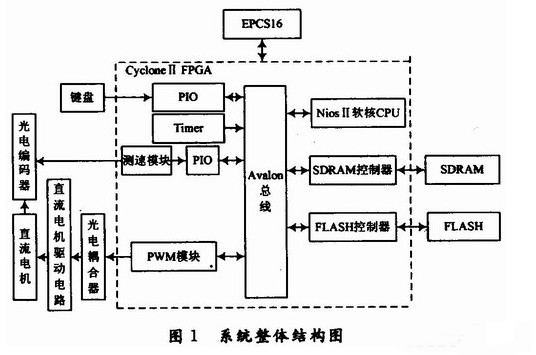

系統(tǒng)中的自定制PWM模塊是通過(guò)寫(xiě)VHDL代碼,經(jīng)過(guò)仿真、編譯、管腳分配,最后生成PWM功能模塊。它在整個(gè)系統(tǒng)中的作用是:對(duì)實(shí)測(cè)轉(zhuǎn)速通過(guò)計(jì)算進(jìn)行閉環(huán)控制。生成的PWM模塊如圖2所示。

圖2中:clk為時(shí)鐘信號(hào)端;sta用來(lái)控制直流電機(jī)正反轉(zhuǎn);conword為占空比信號(hào);PWM_A表示直流電機(jī)處于正轉(zhuǎn)狀態(tài)時(shí)的占空比輸出;PWM_B表示直流電機(jī)處于反轉(zhuǎn)時(shí)的占空比輸出。

PWM模塊的原理如下:將時(shí)鐘源50 MHz的基頻信號(hào)64分頻,作為PWM模塊的基頻信號(hào),以256個(gè)該基頻脈沖信號(hào)作為PWM輸出的一個(gè)周期,由NiosⅡ處理器給出的conword的值指定一個(gè)PWM周期內(nèi)高電平持續(xù)時(shí)間,改變conword的值即刻改變占空比輸出的值。

1.3 測(cè)速模塊

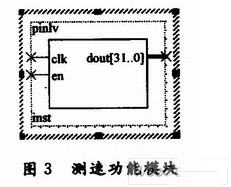

系統(tǒng)中的測(cè)速模塊生成方式如PWM模塊,它在整個(gè)系統(tǒng)中的作用如下:主要是利用基頻的周期來(lái)計(jì)算光柵信號(hào)的周期,算出直流電機(jī)的轉(zhuǎn)速,其生成的模塊如圖3所示。

圖3中:clk為時(shí)鐘信號(hào)端;en為使能信號(hào),即表示光柵有效;dout表示光櫥有效時(shí)間。

測(cè)速模塊的原理如下:給出已知頻率的基頻,用光柵作為門(mén)限,測(cè)基頻脈沖的個(gè)數(shù),由基頻的周期來(lái)計(jì)算光柵信號(hào)的周期,再算出轉(zhuǎn)速,電機(jī)控制算法即根據(jù)測(cè)速模塊測(cè)出的速度進(jìn)行算法調(diào)整,達(dá)到閉環(huán)控制的效果。

2 系統(tǒng)軟件設(shè)計(jì)

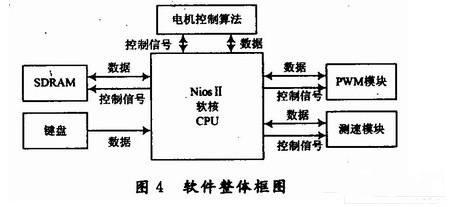

本次設(shè)計(jì)的軟件主要分為兩部分:

(1)利用QuartusⅡ7.2完成NiosⅡ系統(tǒng)的構(gòu)建:利用SOPC Builder構(gòu)建NiosⅡCPU;使用VHDL編寫(xiě)各控制模塊。

(2)利用NiosⅡIDE完成系統(tǒng)控制與控制算法編寫(xiě),主要使用C語(yǔ)言進(jìn)行控制與算法編寫(xiě);對(duì)直流電機(jī)進(jìn)行成功控制后,在NiosⅡIDE上采集輸出轉(zhuǎn)速的實(shí)測(cè)數(shù)據(jù),將其導(dǎo)入Matlab畫(huà)出控制效果圖,整體軟件框圖如圖4所示。

本次設(shè)計(jì)使用SOPC Builder組建的NiosⅡ嵌入式系統(tǒng),如圖5所示。該系統(tǒng)除了配置NiosⅡ最小系統(tǒng)的CPU核NiosII CPU,Avalon總線,使用FPGA資源例化的存儲(chǔ)器之外,還有以下外接設(shè)備的控制單元:

(1)SDRAM Controller;

(2)Common Flash Interface;

(3)JTAG UART;

(4)鎖相環(huán)PLL;

(5)Interval Timer;

(6)通用I/O接口,包括PWM模塊接口conw,msta和測(cè)速模塊接口speed,按鈕接口button。

對(duì)于SOPC Builder組建的NiosⅡ系統(tǒng),可以在QuartusⅡ軟件方便地調(diào)用,在QuartusⅡ中Block Diagram設(shè)計(jì)調(diào)用NiosⅡ系統(tǒng)的框圖如圖6所示。給該系統(tǒng)配備工作時(shí)鐘,并分配FPGA的I/O管腳,程序經(jīng)綜合,布局,仿真之后,就可將配置文件通過(guò)各種配置方法下載到FPGA上。本文使用JTAG+AS方式配置,通過(guò)USB Blaster下載電纜線將計(jì)算機(jī)USB接口與FPGA的JTAG口相連,把配置文件從計(jì)算機(jī)下載到FPGA中,這樣就完成了系統(tǒng)的軟件設(shè)計(jì)。

3 實(shí)驗(yàn)與數(shù)據(jù)分析

3.1 測(cè)試系統(tǒng)

測(cè)試系統(tǒng)由一個(gè)額定電壓為2.5 V的直流有刷電機(jī)和Altera公司的DE2開(kāi)發(fā)板組成。電機(jī)相關(guān)技術(shù)指標(biāo)為:額定電壓為2.5 V,額定功率為O.065 W,額定轉(zhuǎn)速為2 150 r/min,空載轉(zhuǎn)速為2 650 r/min。

整個(gè)測(cè)試系統(tǒng)的硬件結(jié)構(gòu)圖如圖1中所示,其工作流程在前文中有詳細(xì)介紹。

3.2 實(shí)驗(yàn)結(jié)果及分析

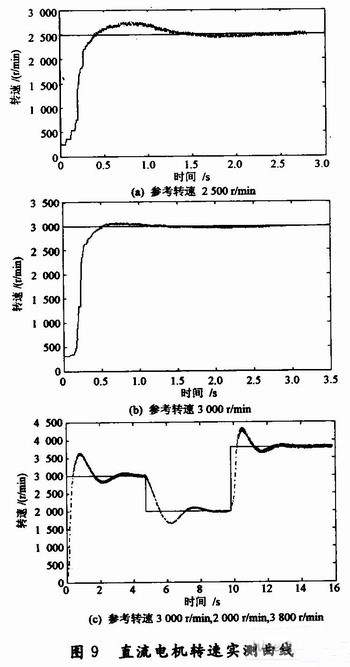

將直流電機(jī)增量式PID算法以C語(yǔ)言的形式寫(xiě)入NiosⅡIDE中,調(diào)試后將其采集到的實(shí)測(cè)數(shù)據(jù)導(dǎo)入Matlab,畫(huà)出時(shí)間與轉(zhuǎn)速之間的關(guān)系圖形如圖7~圖9所示。

(1)比例(P)控制

取采樣周期T=0.1 s,KP=0.5,實(shí)驗(yàn)結(jié)果如圖7所示。

在P控制中,比例環(huán)節(jié)的作用是對(duì)偏差作出快速響應(yīng),Kp,越大,控制能力越強(qiáng),但跟過(guò)大的Kp會(huì)增大超調(diào)量,另外比例環(huán)節(jié)可以減少穩(wěn)態(tài)誤差,但不能完全消除。從圖7中可以看出比例環(huán)節(jié)使得電機(jī)的轉(zhuǎn)速?gòu)牧闾嵘皆O(shè)定值的過(guò)程比較快,但出現(xiàn)了比較明顯的超調(diào),且存在一定的穩(wěn)態(tài)誤差。

(2)比例積分(PI)控制取采樣周期T=O.1 s,Kp=0.5,T1=2,實(shí)驗(yàn)結(jié)果如圖8所示。

在PI控制中,積分環(huán)節(jié)的作用的是消除累計(jì)下來(lái)的偏差(即穩(wěn)態(tài)誤差),在控制過(guò)程中,只要有偏差存在,積分環(huán)節(jié)的輸出就不斷增大,直到偏差為零,輸出才可能穩(wěn)定在某一值上。但積分環(huán)節(jié)會(huì)降低響應(yīng)速度,增加超調(diào)量,T1越大,積分作用越弱。從圖8中可以看出,在比例環(huán)節(jié)上加上積分環(huán)節(jié),先前的穩(wěn)態(tài)誤差得到消除,電機(jī)轉(zhuǎn)速趨于設(shè)定值,但同時(shí)也增加了另一段超調(diào)量。

(3)比例積分微分(PID)控制取采樣周期T=0.1 s,Kp=0.5,T1=2,TD=0.1,實(shí)驗(yàn)結(jié)果如圖9所示。

在PID控制中,微分作用是根據(jù)偏差的變化趨勢(shì)進(jìn)行控制的,偏差變化得越快,微分環(huán)節(jié)輸出就越大,并且能在偏差值變大前進(jìn)行修正。微分環(huán)節(jié)有利于減小超調(diào)量,克服振蕩,TD越大,微分作用越大。從圖9中可以看出,加入微分環(huán)節(jié)后,超調(diào)量明顯得到有效抑制。

從圖7~圖9中可以看出,用PID控制算法控制基于NiosⅡ的直流電機(jī)控制效果還是不錯(cuò)的,有一定的穩(wěn)定性,即便在轉(zhuǎn)速出現(xiàn)跳變時(shí),也能進(jìn)行良好的跟蹤。PID控制算法已經(jīng)相當(dāng)成熟,參數(shù)可以通過(guò)整定很容易得到,實(shí)驗(yàn)表明,此方案具有一定的可行性。

4 結(jié)語(yǔ)

提出一種直流電機(jī)的新型控制方式,即利用NiosⅡ軟核和FPGA芯片對(duì)其控制。通過(guò)實(shí)驗(yàn)驗(yàn)證,將PID增量式算法應(yīng)用到此系統(tǒng)中,能進(jìn)行良好的閉環(huán)控制。在電機(jī)控制中如遇更復(fù)雜的電機(jī),如無(wú)刷電機(jī)等,用NiosⅡ軟核進(jìn)行控制,可以將其擴(kuò)展為雙核乃至多核,一個(gè)CPU用來(lái)控制算法,另一個(gè)CPU用來(lái)控制外圍系統(tǒng),互不干擾,發(fā)揮NiosⅡ處理器的最大優(yōu)勢(shì)。