74系列邏輯器件從問世的40多年以來,雖然一直受到來自可編程器件和系統(tǒng)級芯片的激烈競爭,但依然有一定的市場需求。它們通常能以高效和高性價比的方案來處理與顯示的接口、在電路板或背板上傳送信號、處理多信號位操作、信號屏蔽、啟動芯片等類似問題。

新一代邏輯器件已經出現,其特點是工作電壓低,可以和其他低電壓的器件,例如采用領先65納米和45納米工藝的FPGA、存儲卡以及微型控制器等,直接連接。內核電壓可低至1.2V,而輸入輸出的電壓一般為3.3伏、2.5伏或1.8伏。

為了利用現有的元件種類和功能建立完整的系統(tǒng),設計師需要使用能在不同電壓下運行的邏輯器件,一般來說,使用只支持一個輸入電壓運行的器件來建造整個系統(tǒng)是不可能的。此外,成功的系統(tǒng)設計依賴于能夠有效實現不同工作電壓器件之間連接的方法。

現在,邏輯器件的設計需要注意這些,因為器件必須能夠對任何輸入的信號做出正確的判斷(是或非)。所以有必要保證不同類型和不同代的器件間的互用性,并且需要能夠支持不同的電平,例如3.3伏和5伏之間的轉換,或者更低的電壓標準間的轉換。

處理高電壓和低電壓

圖1顯示了對不同電源電壓和器件技術的閾值。為了成功的連接兩個器件,必須滿足以下條件:驅動器的VOH必須比接收器的VIH高,驅動器的VOL必須比接收器的VIL低,驅動器的輸出電壓不能超過接收器能夠承受的輸入/輸出電壓。

這些條件意味著一個擁有較高的輸入/輸出電壓的器件可以驅動一個較低電壓的器件,只要較低電壓的器件可以承受對其施加的最高電壓值。

單向電平轉換

允許超壓的器件在輸入的VCC沒有鉗位二極管,柵氧化層也較厚,使得器件可以接受比自身VCC更高的電壓。然而,這些器件也有一些限制。如果輸入信號上升或下降較慢,器件在較低電壓標準的極限值會轉換,從而擾亂輸出信號。這可能會出現問題,比如對時鐘負載周期產生微小變化。

另一方面,較低電壓輸出無法驅動較高電壓的輸入。擁有漏極開路輸出的器件可以通過使用外部的負載電阻在較高或較低電壓下驅動輸入。圖2展示了推挽電路如何驅動增加的一個漏極開路驅動器,輸出的晶體管電源通過一個負載電阻連接在驅動器件的VCC。這種結構適用于低到高或高到低的轉換。

74LVC06A/74LCX06是一個低電壓(3.3伏)16進制反向器/緩沖的例子,擁有允許過壓的輸入和漏極開路輸出。這個器件可以在需要高到低或者低到高電壓轉換時驅動數據線。

使用漏極開路器件轉換電平的一個缺點是當輸出的晶體管被啟動時,在輸出為低的條件下,持續(xù)的電流將通過負載電阻流向地。這會帶來相對較高的功率消耗。提高負載電阻值可以減小電流,但由于負載電阻和電容帶來的綜合效應,時間系數會較長。這會減慢信號邊沿,對某些高速轉換或總線應用不實際。

總線開關/FET-開關轉換器

轉換總線開關、或FET開關,是另一類可以在兩種不同的邏輯電平間連接的器件。圖3簡單展示了一個啟動信號如何被用來啟動總線開關。它將A端口和B端口相連,并且提供追蹤VCC的電壓轉換。74CBTD和CB3T邏輯器件系列包含不同配置的總線開關,例如雙路或四路設置。CB3T系列完全支持混合模式信號工作,包括5伏和3.3伏或5伏/3.3伏與2.5伏,也可以在介于2.3伏和3.6伏之間的VCC下工作。CBTD系列允許5伏和3伏之間的電平轉換。

關鍵字:電平轉換低電壓負載電阻邏輯器件

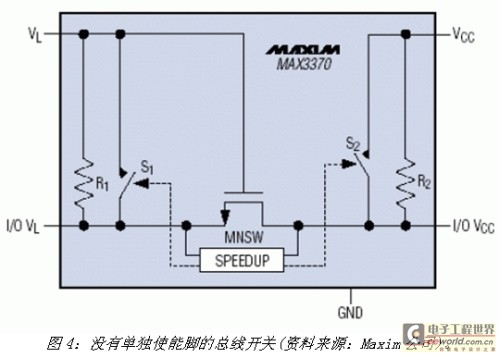

對一個字節(jié)或詞長度的總線進行轉換時,讀或寫的信號可以用來啟動開關。對較小的單線或雙線總線進行電平轉換時,如Maxim MAX3370–MAX3393系列等轉換器,其內部電路可使器件在所有電平級工作,支持由低到高或高到低的混合邏輯電平轉換,也可以進行單向和/或者雙向轉換。圖4顯示了MAX3373芯片,省去了單獨的使能腳,同時集成了一個加速開關從而將電容負載對信號速度的影響降至最低。這樣,推挽式驅動器產生的信號可以以高達20Mbps的速度傳輸數據。

然而,使用總線開關進行電平轉換也有一些缺點。如圖5所示,德州儀器的SN74CB3T3306含有兩個1-位總線開關,在3伏的VCC下工作,用來作為一個3伏的總線和5伏(TTL)總線間的連接。

將3伏總線和5伏總線連接時,5伏一方的VOH信號會箝位在大約2.8伏。盡管這對于5伏的TTL器件還是一個合理的VIH電平,但它的噪音區(qū)間較小,大約為2.8伏-2.0伏=800豪伏。此外,因為CB3T的高輸出沒有完全輸送到VCC,5伏接收器消耗的功率較多。

另外,如果一個CB3T器件被用作3伏CMOS總線和5伏CMOS邏輯元件的連接,就需要一個負載電阻,因為2.8伏不夠作為5伏CMOS邏輯元件的VIH電壓。

雙重輸入電平轉換

雙重輸入器件可以解決不同電平間邏輯連接時帶來的某些速度和消耗功率的問題。這些器件使用兩個輸入電壓,將在VCCA下工作的A方連接到VCCB下工作的B方。同時提供一個DIR輸入,使器件可以進行A到B或B到A的雙向轉換。雙重輸入器件有很多不同的位寬,并且涵蓋差不多所有現今使用的輸入電壓。

雙重輸入器件的另一個優(yōu)勢是主動驅動電流,使他們可以解決使用負載電阻時CR負載帶來的信號邊沿減緩的問題。需要時,他們也可以在較長的走線長度下使用。這些器件有很多種設置,包括多組器件,例如74AVCB320245。這種器件使用四組,每組8位,這樣,一組可以用來將3.3伏轉換為1.8伏,而另一組將1.8伏轉換為3.3伏。主要的制造商都提供74AVC系列器件,包括德州儀器、NXP、Fairchild和意法半導體。

隨著邏輯技術向更低的工作電壓發(fā)展,使用TI AUC或類似技術的新總線電平轉換器件也已經出現,可以對介于1.1伏到3.3伏間的電平進行上下轉換。此外,非74系列的電平轉換器件,例如Fairchild的FXL系列或意法半導體的STxG器件利用雙重輸入的靈活性,實現系列存儲卡,I2C端口或UART等器件的連接。FXL系列可以對介于1.0伏到3.3伏間的電平進行上下轉換。意法半導體的電平轉換器可以處理1.4伏到最高5.5伏的電平轉換,接口范圍包括從1位(ST1G)到16位(ST16G)不等。

這些新出現的系列器件一般都大量使用節(jié)能技術和超小型包裝,例如QFN無鉛或μTFBGA技術,支持便攜式和使用電池的產品,例如手機、照相機、個人媒體播放器和掌上電腦等。

無方向電平轉換

電平轉換的下一步是使轉換方向不再受處理器軟件的控制。擁有TXB01xxx和TXS01xxx系列的德州儀器公司已經通過更復雜的基于CMOS邏輯反向器和針對緩沖類轉換器的推挽結構做到這一點,另一種方法是集成負載電阻和流通晶體管做成自動探測方向的開關式轉換器。德州儀器的自動探測方向轉換器在不同的界面電平下,特別適合點對點結構。他們可以通過省下傳統(tǒng)電平轉換器需要的控制方向的信號,提高下一代處理器和配套器件的連接性。這可以降低控制軟件的復雜性,同時在核心處理器上節(jié)省珍貴的GPIO信號。這些部件有自動的可重新設置的輸入/輸出緩沖,因此每一個輸入/輸出端口同時設置為輸入和輸出。

本文小結

接下來幾代的CMOS封裝流程將在越來越低的輸入電壓下運行。設計師需要能夠使用這些低壓器件,從而利用最新的高速、低功率硅晶體,但同時必須能夠同其他的次級系統(tǒng)元件相連,例如液晶顯示屏。這需要收發(fā)器在較高電壓下運行,因此帶來對電平轉換功能的需求。

目前已有很多邏輯器件可以滿足設計師最低工作電壓的要求,低至0.8伏的邏輯電平和1.2伏的其他器件,例如微型控制器、FPGA、ASIC和ASSP,到高達3.3伏或5伏CMOS電壓下工作的電路進行連接。一如既往,需求總是在功耗、速度、尺寸和成本間衡量選擇。