0 引言

由鎖相環(huán)構(gòu)成的間接式頻率合成器在無線通信領(lǐng)域發(fā)揮著非常重要的作用。通常采用鎖相頻率合成器的輸出信號來作為無線接收機(jī)中的本振信號,以使直接頻率調(diào)制器、頻率解調(diào)器能夠從輸入信號中再生載波。

傳統(tǒng)的頻率合成一般通過混頻、倍頻、分頻、濾波等方式進(jìn)行頻率變換和組合,從而產(chǎn)生大量離散的穩(wěn)定頻率信號。這不僅使頻率合成器具有龐大的體積和重量,其輸出信號中的諧波、噪聲及寄生頻率均難以抑制,同時頻率范圍也將受到限制。而鎖相頻率合成主要是通過晶體振蕩器提供的標(biāo)準(zhǔn)頻率,在給定的頻率范圍內(nèi)產(chǎn)生與該晶體振蕩器穩(wěn)定度相同的大量離散頻率信號。 本文介紹用集成電路MAX2620和集總LC元件構(gòu)成窄帶VC0電路模塊,然后同集成鎖相頻率合成器芯片MBl504.一起構(gòu)成鎖相環(huán)式低噪聲、高穩(wěn)定性的鎖相頻率源電路的設(shè)計方法。

1 整體設(shè)計方案

圖l所示是一個鎖相環(huán)(PLL)的基本電路組成。其中REF代表參考晶體振蕩器,÷R為參考分頻器,PF[)為鑒頻鑒相器,LPF為環(huán)路濾波器,VCO為壓控振蕩器,÷N為前置分頻器。 無線接收機(jī)中的本地振蕩信號通常需要特定的頻點(diǎn),這往往需要設(shè)計一個窄帶且相位噪聲性能優(yōu)越的VCO。雖然用分立晶體管、諧振回路以及緩沖放大器也可以構(gòu)成VCO電路,但穩(wěn)定性差、受電源及分布參數(shù)影響大、調(diào)試不方便。而MAXIM公司的MAX2620是一款較寬頻率范圍(l0~1050 MHz)的集成振蕩器芯片,它具有高頻雙極工藝所特有的低閃爍噪聲、低噪聲系數(shù)和低寄生特點(diǎn)。用戶可以根據(jù)自己的需要并配以適當(dāng)?shù)恼袷幓芈罚瑥亩O(shè)計出所需中心頻率的壓控振蕩器電路。MAX2620內(nèi)部的有源器件對諧振回路的負(fù)載極輕,因而可使振蕩回路具有較高的有載Q值,以用來設(shè)計窄帶壓控振蕩器電路。

MBl504是具有吞脈沖功能的串行輸人鎖相環(huán)頻率合成芯片,該芯片內(nèi)部采用吞脈沖計數(shù)技術(shù)和鑒頻鑒相技術(shù),其T作頻率可達(dá)520 MHz,因而速度快,性能穩(wěn)定,與單片機(jī)接口簡單,可用來實(shí)現(xiàn)對接收機(jī)本振信號進(jìn)行方便地設(shè)置。

2 窄帶VCO的設(shè)計

MAXIM公司的MAX2620是一種使用極其方便的振蕩器芯片,它的內(nèi)部組成原理示意圖如圖2所示。

MAX2620提供有一個緩沖放大輸出級,能夠減少負(fù)載變化對振蕩器頻率的影響。該芯片的供電電壓范圍在+2.7~+5.25V之間。由于芯片內(nèi)部設(shè)有偏置電路以穩(wěn)定其工作點(diǎn),因而受電源波動的影響較小。MAX2620內(nèi)部所并具有的電源關(guān)斷能力可由SHDN端控制。兩個互補(bǔ)輸出(即OUT和OUT)可構(gòu)成兩個單端輸出或一個差分輸出。由于芯片采用是集電極開路輸出,輸出端需要上拉到VCC設(shè)計時可以用電感或電阻來上拉。但是對于差分輸出兩端均應(yīng)采用相同的方式。對于5012的負(fù)載,在用電感上拉時,單端輸出電平可達(dá)-6 dBm (峰一峰電壓為320 mV);而用電阻上拉時,其輸出可達(dá)-10 dBm (200 mV)。本設(shè)計中的MAX2620的兩路輸出中,一路輸出到MBl504供鑒頻鑒相使用,為使穩(wěn)定性更好,此路用電阻上拉而另一路輸出則經(jīng)過緩沖放大,作為時鐘輸出,為了使其輸出功率更大,該路用電感上拉。

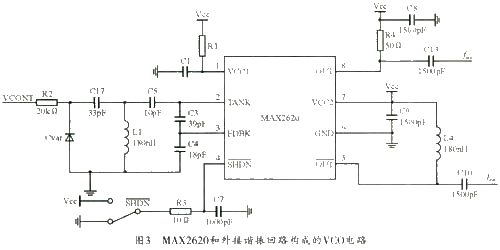

事實(shí)上,MAX2620需要外接RF皆振回路以構(gòu)成VCO電路,其電路如圖3所示。

此電路是一個典型的Colpitts電容反饋式振蕩器。諧振回路在圖3的左方,并經(jīng)過2、3腳接入,主要包括電容C3、C4、C5和C17、諧振電感U和變?nèi)荻O管Cvar,調(diào)諧電壓經(jīng)過電阻R2接入。

SHDN端用三針跳針分別接到Vcc和地,可用于控制電源的關(guān)斷,以在調(diào)試中方便的判斷諧振回路是否起振。

變?nèi)莨芸赏ㄟ^C17接入諧振回路。C17值取為33 pF。經(jīng)過C17后,諧振回路的等效Q將升高數(shù)倍。因此,即便采用廉價的Q和較低的變?nèi)莨埽部稍O(shè)計出Q較高的諧振回路。

諧振回路電感采用表面貼式諧振電感,該電感具有輻射干擾小、受分布電容影響小、調(diào)試方便等特點(diǎn)。電感值選為180 nH,當(dāng)諧振頻率范圍為80~88 MHz時,其中心頻率為84 MHz。由諧振公式 可得出諧振回路的總電容Co=19.94 pF。經(jīng)過調(diào)試,VCO路的具體元件參數(shù)如下:

可得出諧振回路的總電容Co=19.94 pF。經(jīng)過調(diào)試,VCO路的具體元件參數(shù)如下:

R2為20 kΩ,諧振電感L1為180 nH,C3為39pF,C4選18 pF,C5選10 pF,輸出端OUT上拉電感L4選180 nH,輸出端上拉電阻R4可選50 Ω。

3 MBl504與AT89C52的接口設(shè)計

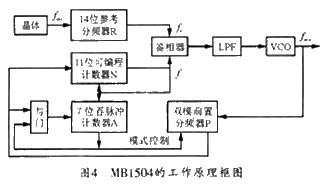

MBl504的原理框圖如圖4所示。該芯片內(nèi)含一個14位可編程參考分頻器、一個分頻比可選擇f32或64)的雙模前置分頻器和一個18位的可變分頻器(由7位的吞脈沖計數(shù)器和1l位的可編程計數(shù)器組成),另外還包含一個鑒相器、一個電荷泵和兩個移位寄存器和鎖存器(圖中未畫出)。

MBl504中雙模前置分頻器的兩種分頻比可由模式控制信號決定。當(dāng)模式控制信號為高電平時,分頻比為P+1,當(dāng)模式控制信號為低電平時,分頻比為P。雙模前置分頻器的輸出可同時驅(qū)動11位可編程計數(shù)器和7位吞脈沖計數(shù)器,它們的初值分別為N和A,可進(jìn)行減計數(shù)。在吞脈沖計數(shù)器和可編程計數(shù)器未計數(shù)到零時,模式控制為高電平,雙模前置分頻器的輸出頻率為fvco/(P+1。當(dāng)輸入A (P+1)個脈沖周期后,吞脈沖計數(shù)器計數(shù)達(dá)到零,模式控制電平將變?yōu)榈碗娖剑瑫r使吞脈沖計數(shù)器停止計數(shù)。此時,可編程計數(shù)器離預(yù)置數(shù)還有N-A的數(shù)值。由于這時模式控制電平為低,分頻比為P,因此,雙模前置分頻器的輸出頻率為fvco/P。之后,再經(jīng)過N-A個計數(shù)周期后,可編程計數(shù)器計數(shù)也達(dá)到零,此時可輸出低電平將兩個可編程分頻器重新預(yù)置為N和A,同時將模式控制恢復(fù)為高電平,并向鑒相器輸出比相脈沖。當(dāng)比相脈沖頻率廠一與參考頻率fr存在頻差時.鑒相器處于鑒頻工作方式。此時無論頻差大小,系統(tǒng)都輸出較大的電壓;而當(dāng)比相脈沖頻率f與參考頻率fr相等時,鑒相器轉(zhuǎn)為鑒相工作方式。這種鑒頻一鑒相工作方式擴(kuò)大了環(huán)路的快捕帶,縮短了頻率牽引過程,從而使環(huán)路快速進(jìn)入相位鎖定區(qū),最終實(shí)現(xiàn)快捕鎖定。

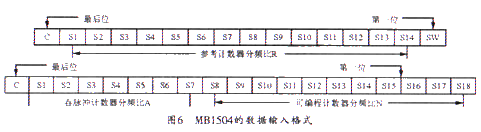

MBl504可通過9腳(Clock)、10腳(Data)和11腳(LE)分別與單片機(jī)AT89C52的P1.2、P1.1、P1.0相連,其連接電路如圖5所示。其中,CLOCK為時鐘信號輸人端,DATA為數(shù)據(jù)信號輸入端。LE為數(shù)據(jù)鎖存使能信號輸入端。信號是串行輸入的,即每輸入一個時鐘脈沖到CLOCK腳,就有一位數(shù)據(jù)從:DATA腳送入MBl504芯片內(nèi)的移位寄存器,并由LE信號控制鎖存。當(dāng)LE為高電平時,儲存在移位寄存器內(nèi)的數(shù)據(jù)被鎖存到相應(yīng)的鎖存器中。而當(dāng)C為高電平時,鎖存到15位的鎖存器的設(shè)置為14位可編程參考分頻器中的預(yù)置數(shù)R和前置分頻器的1位分頻比SW;當(dāng)C為低電平時,鎖存到18位的鎖存器中的設(shè)置則為ll位可編程計數(shù)器中的預(yù)置數(shù)N和7位吞脈沖計數(shù)器中的預(yù)置數(shù)A。圖6所示為MBl504的數(shù)據(jù)輸入格式。

根據(jù)MBl504的工作原理,鎖相環(huán)的輸出頻率fvco的計算公式為:

fvco=(PN+A) fvco/R (N>A)

式中,fosc為外接晶體振蕩器輸人參考頻率;P為前置分頻器的分頻比(由位SW決定),當(dāng)SW為高時,P為32;當(dāng)SW為低時,P為64;N為11位可編程計數(shù)器中的預(yù)置數(shù)(范圍從16~2047);A為7位吞脈沖計數(shù)器中的預(yù)置數(shù)(范圍從0~63);R為14位可編程參考分頻器中的預(yù)置數(shù)(范圍從8~16383)。

本設(shè)計中,頻率合成器的頻率范圍fvco為80~88 MHz,頻率間隔△f為2 kHz。

參考振蕩器的振蕩頻率fosc為4.096 MHz,參考頻率fr等于合成器頻率間隔△f(2kHz),所以參考分頻比R為:fosc/fr=2048,中心頻率為84MHz的分頻比(PN+A=fout/△f)為42000。這里采用的前置分頻比模式為÷32/33,即P=32,并由此可得:N=1312,A=16。這樣,改變N和A,即可改變輸出頻率,而改變N、R,則可改變輸出頻率和頻率間隔。

4 結(jié)束語

本設(shè)計的實(shí)際電路可以制作在一塊50 mm×40mm的雙層板上,電源電壓為+3.3 V。VCO的頻率覆蓋范圍為80~88 MHz,兩路輸出電平,OUT端為-l0 dBm,OUT端為-6 dBm。輸出功率大于10dBm,且信號純度很高,雜散較少。

由于幾種LC元件和MAX2620構(gòu)成的窄帶VCO具有穩(wěn)定性高、受外界分布參數(shù)影響小、調(diào)試方便、體積小、價格低廉等優(yōu)點(diǎn)。因此.由該VCO和MBl504芯片構(gòu)成的鎖相時鐘頻率源的時鐘頻率源穩(wěn)定性高、相位噪聲較低。