引言

超聲波流量計(jì)是隨著IC技術(shù)迅速發(fā)展而開始得到實(shí)際應(yīng)用的一種非接觸式儀表。它是一種利用聲學(xué)原理工作的新型流量測(cè)量?jī)x表。與傳統(tǒng)流量計(jì)(如孔板、渦輪流量計(jì)等)相比,它具有測(cè)量準(zhǔn)確度幾乎不受介質(zhì)溫度、壓力影響等優(yōu)點(diǎn),尤其是在大管徑流量測(cè)量方面,其優(yōu)越性更加明顯,因此得到了越來越廣泛的應(yīng)用。

近年來,隨著Altera公司32位軟核CPU NiosII的推出,基于FPGA的SOPC(System On a Programmable Chip)技術(shù)發(fā)展越來越快。SOPC是可編程系統(tǒng),具有靈活的設(shè)計(jì)方式,并且可裁剪,可擴(kuò)充,可升級(jí),同時(shí)具備軟硬件在線系統(tǒng)可編程的功能。SOPC兼具PLD和FPGA的優(yōu)點(diǎn),它的特點(diǎn)包括:至少包含一個(gè)嵌入式處理器內(nèi)核;具有小容量片內(nèi)高速RAM資源;有足夠的片上可編程邏輯資源;有處理器調(diào)試接口和FPGA編程接口;可能包含部分可編程模擬電路;單芯片,低功耗,微封裝。正是基于這些優(yōu)點(diǎn),基于NiosII的SOPC得到了越來越廣泛的應(yīng)用。

本文就是基于超聲波以及SOPC這兩項(xiàng)技術(shù)來設(shè)計(jì)便攜式的超聲波流量計(jì),充分發(fā)揮這兩項(xiàng)技術(shù)的優(yōu)點(diǎn),實(shí)現(xiàn)對(duì)液體、氣體的高精度測(cè)量。

1 工作原理及系統(tǒng)組成

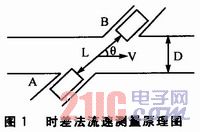

本系統(tǒng)利用時(shí)差法進(jìn)行流速測(cè)量:安裝于被測(cè)容器頂部的收發(fā)一體的超聲波換能器(A或B)通過空氣向被測(cè)物體發(fā)射一束超聲波,該聲波經(jīng)被測(cè)物體反射后,回波被換能器(B或A)接收并被轉(zhuǎn)換為電信號(hào)。原理圖如圖1所示。

這樣,在已知安裝角度θ和管徑D的條件下,測(cè)量A到B的傳播時(shí)間tAB以及從B到A的傳播時(shí)間tBA,通過計(jì)算可得

![]()

這種算法只需測(cè)出tAB與tBA就可以得到流速V,而通過對(duì)流速進(jìn)行積分運(yùn)算就可以進(jìn)一步算得流量,這就是時(shí)差法測(cè)量流速的基本原理。

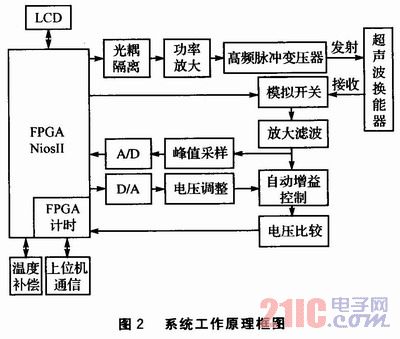

整個(gè)便攜式超聲波流量計(jì)系統(tǒng)組成如圖2所示。系統(tǒng)由脈沖發(fā)射電路、回波接收電路、信號(hào)處理電路和CPU控制電路組成。脈沖發(fā)射電路是輸出一定超聲波頻率的脈沖激勵(lì)信號(hào)經(jīng)功率放大和升壓后驅(qū)動(dòng)超聲波換能器發(fā)射超聲波;回波接收電路即是接收回波信號(hào);信號(hào)處理電路用于對(duì)回波信號(hào)進(jìn)行放大、帶通濾波、自動(dòng)增益控制、電壓比較等處理;CPU控制電路控制發(fā)射信號(hào)、控制模擬開關(guān)、捕獲計(jì)時(shí)、數(shù)據(jù)處理及與外部設(shè)備通信。

2 模擬電路部分設(shè)計(jì)

2.1 超聲波前端驅(qū)動(dòng)電路

如圖2所示,超聲波換能器驅(qū)動(dòng)電路產(chǎn)生一個(gè)具有特定頻率、脈沖寬度和輸出功率的電脈沖去激勵(lì)超聲波換能器,進(jìn)而產(chǎn)生超聲波向外發(fā)射。對(duì)于超聲波換能器,超聲波換能器驅(qū)動(dòng)電路提供的功率越大,超聲波換能器將電能轉(zhuǎn)換為聲能的效果越好,所以超聲波換能器驅(qū)動(dòng)電壓應(yīng)該越大越好,但需要注意驅(qū)動(dòng)電壓壓值不能超過換能器壓降極限。本系統(tǒng)應(yīng)用晶體管組成推挽式電路結(jié)合場(chǎng)效應(yīng)管電路來實(shí)現(xiàn)功率放大。

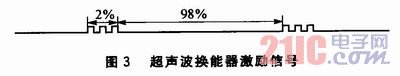

系統(tǒng)超聲波換能器驅(qū)動(dòng)信號(hào)是由微處理器產(chǎn)生的,微處理器產(chǎn)生一個(gè)200 kHz的矩形脈沖信號(hào),經(jīng)光耦隔離后進(jìn)入功率放大電路。根據(jù)換能器的特點(diǎn),該矩形脈沖信號(hào)占空比為2%。超聲波換能器激勵(lì)信號(hào)如圖3所示。

2.2 超聲波信號(hào)處理電路

超聲發(fā)射換能器發(fā)射的超聲波信號(hào),經(jīng)過管壁和流體,衰減比較大,因此超聲波接收換能器接收的信號(hào)比較微弱,通常只為幾十mV數(shù)量級(jí),這時(shí)放大器的噪聲對(duì)測(cè)量精度的影響也比較大。同時(shí),由于超聲波流量計(jì)中使用的超聲波頻率較高,所以要求運(yùn)算放大的增益帶寬積足夠高,因此該級(jí)電路采用低噪聲高速運(yùn)算放大器。本系統(tǒng)中選用MAX410作為放大器。

在超聲波流量計(jì)工作的過程中,由于振動(dòng)、流動(dòng)及工業(yè)現(xiàn)場(chǎng)的管道噪聲和變頻設(shè)備的電噪聲等電子干擾,會(huì)引起周期性的噪聲信號(hào)出現(xiàn),并導(dǎo)致在相關(guān)圖上出現(xiàn)周期性波峰。當(dāng)其疊加到流動(dòng)噪聲的相關(guān)曲線上,會(huì)使真實(shí)的渡越時(shí)間對(duì)應(yīng)的波峰不明顯,甚至被其他的波峰掩蓋,無法得到正確的測(cè)量結(jié)果。通過低噪聲高速運(yùn)算放大器對(duì)信號(hào)進(jìn)行放大后還需要對(duì)信號(hào)進(jìn)行濾波。本系統(tǒng)中的濾波電路為帶通濾波。系統(tǒng)中換能器發(fā)射接收的超聲波中心頻率為200 kHz,所以需要設(shè)計(jì)一個(gè)中心頻率為200 kHz的帶通濾波器,它可以使200 kHz的超聲波信號(hào)順利地通過,而阻止或衰減非200 kHz的超聲波信號(hào)及其他干擾信號(hào)。

另外,超聲波信號(hào)在管道中傳輸時(shí),由于各個(gè)聲道長(zhǎng)度不同,傳感器特性存在差異,氣體介質(zhì)不同以及測(cè)量時(shí)氣體流速的變化,導(dǎo)致每次測(cè)量時(shí)傳感器接收信號(hào)的幅度也不同。為了后端進(jìn)行高精度的計(jì)時(shí),需要自動(dòng)增益控制對(duì)接收信號(hào)的大小進(jìn)行調(diào)節(jié),使接收信號(hào)有一個(gè)穩(wěn)定的幅度,從而滿足系統(tǒng)測(cè)量高精度的要求。

3 數(shù)字電路設(shè)計(jì)部分

3.1 概述

本系統(tǒng)數(shù)字電路設(shè)計(jì)部分的核心是FPGA。在本系統(tǒng)中FPGA主要實(shí)現(xiàn)兩部分功能:一是實(shí)現(xiàn)高精度計(jì)時(shí),為準(zhǔn)確測(cè)量流速提供保證;二是通過構(gòu)建軟核CPUNioslI來實(shí)現(xiàn)對(duì)整個(gè)系統(tǒng)的控制。本系統(tǒng)選用Altera公司Cyclone II系列的EP2C8Q208C8N芯片。

關(guān)于計(jì)時(shí)這里不再贅述,主要就是通過MEGA WIZARD調(diào)用PLL模塊實(shí)現(xiàn)倍頻到200 MHz然后供給計(jì)數(shù)器模塊來計(jì)數(shù),計(jì)數(shù)結(jié)果通過移位寄存器來上傳給CPU,再通過CPU處理后傳給上位機(jī)。

NiosII是32位RISC嵌入式處理器,它是Altera公司的第二代FPGA嵌入式處理器,其性能超過200DMIPS,在Altera FPGA中實(shí)現(xiàn)僅需35美分。特別是,NioslI系列支持使用專用指令。專用指令是用戶增加的硬件模塊,它增加了算術(shù)邏輯單元(ALU)。用戶能為系統(tǒng)中使用的每個(gè)NiosII處理器創(chuàng)建多達(dá)256個(gè)專用指令,這使得設(shè)計(jì)者能夠細(xì)致地調(diào)整系統(tǒng)硬件以滿足性能目標(biāo)。NiosII系列支持60多個(gè)外設(shè)選項(xiàng),開發(fā)者能夠選擇合適的外設(shè),獲得最合適的處理器、外設(shè)和接口組合,而不必支付根本不使用的硅片功能。基于其嵌入式的特點(diǎn)以及其成本,NiosII特別適用于便攜式儀表方面的應(yīng)用。

3.2 SOPC的硬件構(gòu)建

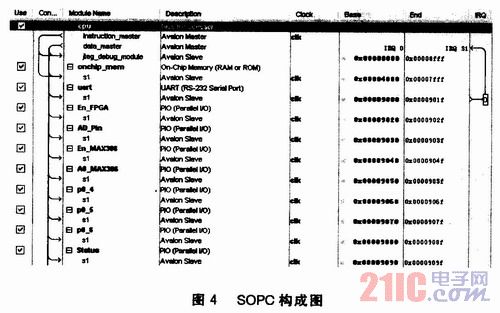

通過Quartus中的SOPC Builder來構(gòu)建SOPC系統(tǒng)。首先要添加一個(gè)CPU。為了節(jié)省片上資源,選用經(jīng)濟(jì)型的CPU,外部晶振是50 MHz。程序運(yùn)行內(nèi)存直接選用0n-Chip Memory,因?yàn)镋P2C8Q208C8N片上的RAM空間大概有20 KB左右,通過優(yōu)化,片上內(nèi)存完全能夠滿足程序的需要,這樣就不必添加外接的SDRAM芯片,減少了PCB板的面積,大大降低了成本。代碼優(yōu)化方法是通過NioslI IDE里面的System Library Proper-ties來設(shè)置:依次選中Program Never Exit,Small C Library,Reduced Device Drivers,Lightweight Device Drivers API,取消選中

Support C++并設(shè)定Optimize Size為-0s級(jí),這樣就可以有效的縮減程序代碼。

另外,為了向上位機(jī)傳遞測(cè)試數(shù)據(jù),需要添加UART。這里添加的UART只是一個(gè)協(xié)議,與上位機(jī)實(shí)現(xiàn)通信,還需要在外圍添加電平轉(zhuǎn)換芯片MAX232以實(shí)現(xiàn)與上位機(jī)的正常通信。

為保證系統(tǒng)正常運(yùn)行,添加內(nèi)部定時(shí)器實(shí)現(xiàn)看門狗功能,另外需要添加的就是一些PIO接口。能夠產(chǎn)生中斷的PIO口注意要分給一定的中斷號(hào)。CPU的Reset Vectot。地址和Exception Vector地址都設(shè)為On-Chip Memory,并讓系統(tǒng)自動(dòng)分配基地址以及中斷。點(diǎn)擊Generate生成整個(gè)SOPC,圖4即為整個(gè)SOPC的構(gòu)成圖。

3.3 用Niosll IDE編寫整個(gè)系統(tǒng)的控制程序

NiosII IDE(Integrated Development Environment,集成開發(fā)環(huán)境)提供了完整的C/C++軟件開發(fā)套件,包括編輯器、項(xiàng)目管理器和構(gòu)建工具、調(diào)試器和兼容CFI(Common Flash Interface)的Flash編程器。調(diào)試器連接多種目標(biāo)系統(tǒng),包括FPGA硬件(通過JTAG電纜)、NioslI指令集仿真器和Modelsim-Altera軟件,因而能夠提供最靈活的調(diào)試方案。

為了方便用戶編程,NiosII為用戶提供了設(shè)備驅(qū)動(dòng)程序,也就是硬件驅(qū)動(dòng)層數(shù)據(jù)庫(kù)HAL。軟件編寫人員只要利用HAL提供的各種函數(shù)就能編寫應(yīng)用程序,從而方便地與底層硬件進(jìn)行通信,而無需關(guān)心底層硬件的實(shí)現(xiàn)細(xì)節(jié)。HAL系統(tǒng)庫(kù)可在IDE創(chuàng)建一個(gè)新工程時(shí),由系統(tǒng)自動(dòng)生成。

NioslI IDE完全支持C/C++,本系統(tǒng)采用的編程語言是標(biāo)準(zhǔn)C。添加必要的頭文件,編寫各個(gè)中斷服務(wù)程序以及子程序,就可以實(shí)現(xiàn)整個(gè)超聲波流量計(jì)的控制。

仿真NiosII設(shè)計(jì)包括3種方式:“NiosII IDE Debugger+Signal Tap II+物理板”的軟硬件聯(lián)調(diào)方式,“NiosII IDE Debugger+指令集仿真器ISS”的軟件調(diào)試方式(ISS可對(duì)部分組件建模),使用Modelsim-Altera進(jìn)行的RTL級(jí)的功能仿真方式(可以調(diào)試處理器及其外設(shè)之間的交互情況)。Debug的方式可以通過IDE里面的RunDebug As進(jìn)行選擇。NiosII IDE也可以進(jìn)行設(shè)置斷點(diǎn),單步調(diào)試,觀察變量,內(nèi)存以及表達(dá)式的值等操作,在此不一一贅述。Debug之后還需要建立工程,若整個(gè)系統(tǒng)無錯(cuò),可以生成一個(gè)ELF文件,只有完整建立起來的系統(tǒng)才可以下載到FPGA的板上運(yùn)行。具體實(shí)現(xiàn)方式是通過NiosII IDE里面的Project-Build Project來建立工程,結(jié)果會(huì)提示程序代碼總共占用了多少代碼,剩余多少的RAM空間,以及錯(cuò)誤和警告提示。根據(jù)錯(cuò)誤警告提示修改代碼,直至無錯(cuò)完整地建立工程,這樣NiosIIIDE里面的工作就全部完成了。通過FPGA下載線將程序下載到FPGA板上,整個(gè)系統(tǒng)就可以完整地運(yùn)行。

4 實(shí)驗(yàn)結(jié)果及分析

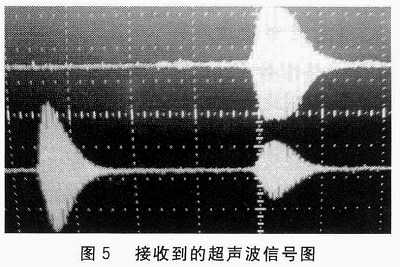

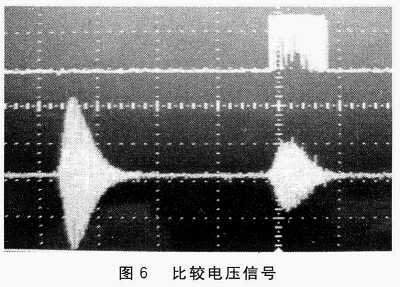

將程序正確下載到FPGA板上,硬件正確連接,接上超聲波探頭,進(jìn)行實(shí)驗(yàn)。實(shí)驗(yàn)結(jié)果表明,本系統(tǒng)可以準(zhǔn)確地實(shí)現(xiàn)對(duì)整個(gè)系統(tǒng)的控制,經(jīng)過信號(hào)處理的超聲波信號(hào)清晰穩(wěn)定,實(shí)驗(yàn)結(jié)果能夠滿足系統(tǒng)的精度要求,效果良好。圖5即為實(shí)驗(yàn)現(xiàn)場(chǎng)接收到的超聲波信號(hào)。圖6為比較電壓的信號(hào)圖。

圖5中下方是經(jīng)過濾波之后的超聲波的發(fā)射和接收信號(hào)。可以看到信號(hào)清晰穩(wěn)定。上方的信號(hào)是經(jīng)過自動(dòng)增益控制之后的超聲波回波信號(hào),通過自動(dòng)增益控制之后的接收信號(hào)可以穩(wěn)定在一定的幅度之內(nèi),保證了系統(tǒng)對(duì)高精度計(jì)時(shí)的要求。

圖6中下方也是濾波之后的超聲波發(fā)射和接收信號(hào)。上方的信號(hào)為電壓比較器所產(chǎn)生的計(jì)時(shí)停止信號(hào)。當(dāng)通過自動(dòng)增益控制之后的接收信號(hào)達(dá)到電壓比較器的參考電壓時(shí),電壓比較器便會(huì)產(chǎn)生一個(gè)計(jì)時(shí)停止信號(hào),并發(fā)送給FPGA,這樣計(jì)時(shí)停止,便準(zhǔn)確地測(cè)量了超聲波的傳播

時(shí)間。

實(shí)驗(yàn)結(jié)果表明,本系統(tǒng)可以準(zhǔn)確地實(shí)現(xiàn)對(duì)整個(gè)系統(tǒng)的控制,經(jīng)過信號(hào)處理的超聲波信號(hào)清晰穩(wěn)定,實(shí)驗(yàn)結(jié)果能夠滿足系統(tǒng)的精度要求,效果良好。