摘要:根據(jù)當(dāng)前網(wǎng)絡(luò)化測控需求,采用了ARM" title="ARM">ARM920T核的微處理器S3C2440" title="S3C2440">S3C2440,ZigBee無線SoC芯片CC2430F128相結(jié)合的硬件設(shè)計(jì)方案,設(shè)計(jì)了一種基于ARM和ZigBee的通用網(wǎng)絡(luò)化測控系統(tǒng)硬件平臺(tái),詳細(xì)闡明了系統(tǒng)各模塊的硬件設(shè)計(jì)。實(shí)際應(yīng)用表明,系統(tǒng)硬件平臺(tái)網(wǎng)絡(luò)性能好、通用性強(qiáng)且成本較低。

關(guān)鍵詞:ARM;網(wǎng)絡(luò)測控;通用平臺(tái);硬件設(shè)計(jì);ZigBee

O 引言

隨著物聯(lián)網(wǎng)概念的提出及相關(guān)技術(shù)的發(fā)展,網(wǎng)絡(luò)化測量控制已成為測控系統(tǒng)發(fā)展的必然趨勢。然而,當(dāng)前國內(nèi)外工業(yè)控制領(lǐng)域普遍使用且技術(shù)相當(dāng)成熟的PLC(Programable Logic Controller)基本都不支持網(wǎng)絡(luò),也不能簡單升級(jí)具有網(wǎng)絡(luò)功能,且模式較為單一。因而,設(shè)計(jì)與實(shí)現(xiàn)了一種網(wǎng)絡(luò)化通用測控系統(tǒng)平臺(tái),以實(shí)現(xiàn)網(wǎng)絡(luò)化測控需求且具有一般平臺(tái)的通用性能。本文主要介紹了ARM嵌入式系統(tǒng)與ZigBee無線技術(shù)相結(jié)合的通用網(wǎng)絡(luò)測控" title="通用網(wǎng)絡(luò)測控">通用網(wǎng)絡(luò)測控平臺(tái)的硬件設(shè)計(jì)。

1 系統(tǒng)硬件總體設(shè)計(jì)

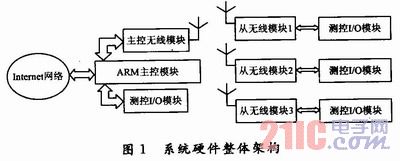

基于ARM的通用網(wǎng)絡(luò)測控系統(tǒng)硬件架構(gòu)如圖1所示,本系統(tǒng)在測控端采用基于ARM的CPU,通過網(wǎng)絡(luò)接口與Internet相連,外圍擴(kuò)展有數(shù)字量輸入/輸出模塊、模擬量輸入/輸出模塊及無線ZigBee組網(wǎng)數(shù)據(jù)傳輸模塊。硬件設(shè)計(jì)的主要研究內(nèi)容:基于ARM的嵌入式主控硬件平臺(tái)、ZigBee無線網(wǎng)絡(luò)數(shù)據(jù)傳輸模塊、測控I/0模塊硬件以及硬件系統(tǒng)的通用性指標(biāo)和網(wǎng)絡(luò)化性能的分析測試。

2 ARM主控模塊硬件

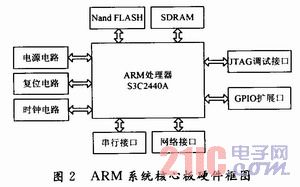

系統(tǒng)核心芯片是Samsung公司生產(chǎn)的基于ARM920T核16/32位RSIC(Reduced Instruction Set Computer,精簡指令集計(jì)算機(jī))微處理器S3C2440A,該芯片資源豐富、運(yùn)算速度快、功能強(qiáng)大,且價(jià)格相對(duì)合理。核心板系統(tǒng)框圖如圖2所示。

2.1 存儲(chǔ)器電路

FLASH存儲(chǔ)器采用Samsung半導(dǎo)體生產(chǎn)的64M×8 b的K9F1208U0M Nand FLASH存儲(chǔ)器芯片。本系統(tǒng)使用了一片該芯片構(gòu)成64MB的FLASH,系統(tǒng)的啟動(dòng)代碼Bootloader文件、內(nèi)核鏡像文件以及文件系統(tǒng)均存于此。SDRAM存儲(chǔ)器采用Hynix生產(chǎn)的4 Banks×4M×16 b的HY57V561620 CSD-RAM芯片,為了保證系統(tǒng)的運(yùn)行速度,本系統(tǒng)采用兩片該芯片并聯(lián)構(gòu)成32位數(shù)據(jù)存儲(chǔ)器。

2.2 JTAG調(diào)試接口

JTAG(Joint Test Action Group,聯(lián)合測試行動(dòng)小組)是一種國際標(biāo)準(zhǔn)測試協(xié)議(IEEE 1149.1兼容),主要用于芯片內(nèi)部測試。它在芯片內(nèi)部封裝了專門的測試電路TAP(Test Access Port,測試訪問口),通過專用的JTAG測試工具對(duì)內(nèi)部節(jié)點(diǎn)進(jìn)行測試,同時(shí)可用于在線編程。標(biāo)準(zhǔn)的JTAG接口是4線:TMS,TCK,TDI,TDO,分別為模式選擇、時(shí)鐘、數(shù)據(jù)輸入和數(shù)據(jù)輸出線。系統(tǒng)采用20針的標(biāo)準(zhǔn)接口,用于在線調(diào)試及系

統(tǒng)Bootloader的下載。

2.3 電源與系統(tǒng)時(shí)鐘電路

電源設(shè)計(jì)的可靠性關(guān)系到系統(tǒng)運(yùn)行的穩(wěn)定與否。本系統(tǒng)輸入電源為5 V,通過LM1117芯片將其穩(wěn)壓至3.3V,使用大電容抑制低頻干擾,小電容抑制高頻干擾,用于芯片接口的供電,同時(shí)采用專用電源芯片MIC5219BMM,為內(nèi)核提供低噪的1.3 V電壓,以確保系統(tǒng)供電穩(wěn)定。

系統(tǒng)時(shí)鐘主要分為主頻時(shí)鐘FCLK,AHB總線設(shè)備時(shí)鐘HCLK,APH總線設(shè)備時(shí)鐘PCLK。本系統(tǒng)采用外部12 MHz晶體振蕩器,通過S3C2440的設(shè)置模式選擇引腳OM[2:3]均為低電平的組合方式來選擇S3C2440的時(shí)鐘源為外部晶振XTIPLL。同時(shí),可通過片內(nèi)的兩個(gè)鎖相環(huán)MPLL和UPLL來得到內(nèi)核時(shí)鐘和USB時(shí)鐘。

2.4 串行接口電路

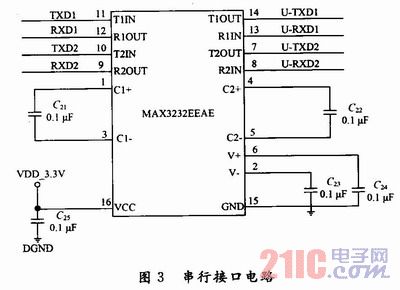

當(dāng)前,基本上各種處理器上都具備串口,本系統(tǒng)中的串口主要用于前期調(diào)試以及與主無線模塊的通信。由于CPU串口引出腳電平不是標(biāo)準(zhǔn)RS 232電平,因此在與PC機(jī)連接調(diào)試時(shí)需進(jìn)行電平轉(zhuǎn)換,而與無線模塊通信則可直連。可以在Linux內(nèi)核串口驅(qū)動(dòng)的基礎(chǔ)上修改為ZigBee的數(shù)據(jù)收發(fā)驅(qū)動(dòng),其電路如圖3所示。

2.5 網(wǎng)絡(luò)接口電路

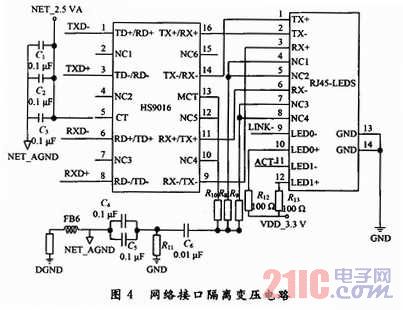

網(wǎng)絡(luò)接口電路是該系統(tǒng)中重要的硬件部分。為了保證網(wǎng)絡(luò)數(shù)據(jù)傳輸?shù)姆€(wěn)定流暢,本系統(tǒng)中采用10/100 Mb/s自適應(yīng)以太網(wǎng)MAC控制器芯片DM9000A,該芯片具有一個(gè)10/100 Mb/s自適應(yīng)的PHY和4K DWORD值的SRAM,物理協(xié)議層接口完全符合IEEE 802.3u規(guī)范,支持IEEE802.3x全雙工流量控制。主控模塊板上nGCS3接DM9000A的片選CS#,地址配置為0x18000002,LDATA[15:0]接DM9000A數(shù)據(jù)位SD[15:0]構(gòu)成16位數(shù)據(jù)總線模式。此外,采用HS9016用于I/O隔離變壓,然后連接RJ45接口。隔離電路如圖4所示。

3 測控I/O模塊硬件

3.1 數(shù)字量輸入/輸出模塊

系統(tǒng)實(shí)現(xiàn)了8路數(shù)字量的輸入,8路數(shù)字量的輸出,采用CH573對(duì)數(shù)字量輸出進(jìn)行鎖存,采用CH245對(duì)輸入量進(jìn)行選通。為了節(jié)省端口資源,數(shù)字量的輸入、輸出的8根數(shù)據(jù)線復(fù)用,通過控制CH573的鎖存信號(hào)以及CH245的片選信號(hào)來實(shí)現(xiàn)輸出量和輸入量的復(fù)用。同時(shí),采用光耦用于端口光電隔離。

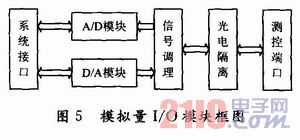

3.2 模擬量輸入/輸出模塊

系統(tǒng)A/D實(shí)現(xiàn)4路12位模擬量或2路12位差分信號(hào)模擬量采樣輸入,系統(tǒng)D/A實(shí)現(xiàn)2路12位模擬量輸出。該模塊A/D采用Microchip公司生產(chǎn)的12位模數(shù)轉(zhuǎn)換器MCP3204,采樣速率最高可達(dá)100 KSPS,且價(jià)格低廉;該模塊D/A采用TI公司的12位數(shù)模轉(zhuǎn)換器TLV5638,該芯片具有內(nèi)部基準(zhǔn),建立時(shí)間為1~3.5μs,具備2通道模擬量輸出能力。只需外加信號(hào)調(diào)理電路即可。由于上述兩款芯片均為SPI接口,可直接掛接到處理器的SPI總線接口上,通過片選CS0和CS1來控制數(shù)據(jù)傳輸?shù)那袚Q。其結(jié)構(gòu)圖如5所示。

4 ZigBee無線模塊硬件

ZigBee技術(shù)是當(dāng)前發(fā)展較為迅速且日趨成熟的一種無線通訊技術(shù),采用國際通用免費(fèi)頻段2.4 GHz,具有低功耗、低成本、低復(fù)雜度等優(yōu)點(diǎn)。ZigBee技術(shù)較易實(shí)現(xiàn)自動(dòng)組網(wǎng),網(wǎng)絡(luò)容量大,可容納多達(dá)65 000個(gè)節(jié)點(diǎn),網(wǎng)絡(luò)中的任意節(jié)點(diǎn)之間都可進(jìn)行數(shù)據(jù)通訊。網(wǎng)絡(luò)具有星狀、樹狀和網(wǎng)狀網(wǎng)絡(luò)拓?fù)浣Y(jié)構(gòu)。

本系統(tǒng)采用的是TI公司生產(chǎn)的SOC芯片CC2430,內(nèi)置增強(qiáng)型的8051內(nèi)核,接口豐富,具有8 KB SDRAM,128 KB閃存,只需加上電源電路、晶振電路、天線而無需其它外部擴(kuò)展即可配置為FFD(全功能器件)或RFD(簡化功能器件),因而硬件設(shè)計(jì)簡便,成本也相對(duì)較低,模塊采用串口與ARM系統(tǒng)通信。實(shí)物圖如圖6所示。

5 系統(tǒng)分析測試

網(wǎng)絡(luò)化在本系統(tǒng)中主要體現(xiàn)為兩個(gè)方面,一個(gè)是采用ZigBee構(gòu)成的無線網(wǎng)絡(luò),用于無線數(shù)據(jù)采集。另一個(gè)則是Internet網(wǎng)絡(luò),用于嵌入式系統(tǒng)與主控制端進(jìn)行數(shù)據(jù)交互。并且,本系統(tǒng)測控I/O模塊符合標(biāo)準(zhǔn)測控電壓電流規(guī)格定義,并采用ZigBee無線技術(shù),可實(shí)現(xiàn)簡單二次開發(fā)。經(jīng)軟件測試,該系統(tǒng)可完成不同物理量、本地或遠(yuǎn)程、無線或有線以及一定精度與實(shí)時(shí)性的網(wǎng)絡(luò)測量控制,具備一般通用平臺(tái)的性能。

6 結(jié)語

網(wǎng)絡(luò)化是測控技術(shù)發(fā)展的一個(gè)重要方向,伴隨網(wǎng)絡(luò)技術(shù)的發(fā)展,也需要一種通用的平臺(tái)統(tǒng)一各分散的測控點(diǎn)。本文基于上述考慮,提出了通用網(wǎng)絡(luò)測控系統(tǒng)設(shè)計(jì)基本思想,也闡述了較為詳盡的硬件設(shè)計(jì)方案,該系統(tǒng)通用性好、網(wǎng)絡(luò)設(shè)計(jì)合理、成本低,并且易于產(chǎn)品化。經(jīng)簡單設(shè)置或二次開發(fā),該系統(tǒng)可應(yīng)用于工業(yè)生產(chǎn)車間、智能家居,以及油田油井遙測等廣泛的行業(yè)和領(lǐng)域。