在通信系統(tǒng)" title="通信系統(tǒng)">通信系統(tǒng)的電路中,大多存在兩種以上的電源" title="電源">電源,實(shí)際工程應(yīng)用中還常有蓄電池提供后備供電的情況,對(duì)于這些電路,在電壓變化的過程中,可能會(huì)引發(fā)電路無效復(fù)位或上電失敗的故障。對(duì)此,本文提出了一種實(shí)用的解決方案。

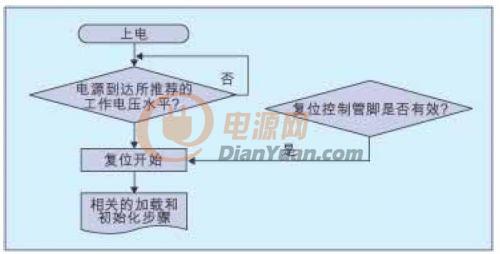

圖1: FPGA的上電加載機(jī)制。

隨著通信設(shè)備復(fù)雜程度的提高,工程應(yīng)用對(duì)設(shè)備的可靠性" title="可靠性">可靠性要求也隨之提高。各種電源配送方案在工程運(yùn)用上得到了廣泛的應(yīng)用,在有后備電池供電的應(yīng)用上,由于供電系統(tǒng)的切換,通信設(shè)備內(nèi)各部件將面臨一次上電初始化的考驗(yàn)。

電路上電問題分析

現(xiàn)在通信機(jī)房大多采用-48V直流電源,而電子元器件一般采用低電壓供電,以5V和3.3V最為常見,近幾年隨著低功耗器件的大量使用,1.5V、1.8V、2.5V電源也被采用。電路設(shè)計(jì)中往往采用DC-DC電源轉(zhuǎn)化模塊提供二次電源。在同時(shí)使用多種電源時(shí),可采用多種電源模塊,或采用一種電源模塊加多個(gè)直流電壓轉(zhuǎn)換器的方案,下面就兩種典型情況作簡(jiǎn)單分析。

1.采用多電源模塊設(shè)計(jì)的電路

這種設(shè)計(jì)一般包括1只48-5V電源模塊和1只48-3.3V電源模塊。其中5V電源模塊主要給電路內(nèi)5V器件供電;3.3V電源模塊主要給電路內(nèi)FPGA、ASIC供電,以及供給直流電壓轉(zhuǎn)換器進(jìn)行更小電壓的轉(zhuǎn)換。這里應(yīng)當(dāng)指出,如果采用線性調(diào)壓器(LDO)進(jìn)行小電壓轉(zhuǎn)換時(shí),上級(jí)電壓通常采用3.3V,因?yàn)槌S玫?.5V、1.8V、2.5V與5V的壓降很大,在進(jìn)行電壓轉(zhuǎn)換的時(shí)候?qū)p失更多功率,同時(shí)增加系統(tǒng)的散熱負(fù)擔(dān)。

對(duì)于這種設(shè)計(jì),由于不同電源模塊的指標(biāo)差異,存在上電順序的問題。如果5V達(dá)到穩(wěn)定的時(shí)間比3.3V早,那么將可能造成如下問題:a. 5V器件已經(jīng)運(yùn)行正常,而3.3V的FPGA、ASIC還未加載或初始化完畢。如果電路內(nèi)MCU單元為5V供電,那么MCU初始化FPGA和ASIC失敗,電路工作將不正常,這種情況理論上可以通過在MCU程序代碼里添加空轉(zhuǎn)等待語句,但是實(shí)際上仍然存在問題,見下面的分析。

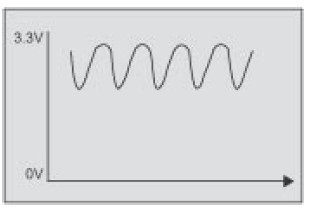

b. FPGA加載失敗。圖1顯示了一般可編程邏輯器件的上電加載機(jī)制。圖2顯示了48-3.3V的某品牌電源模塊在用蓄電池加電時(shí),其電壓在上升過程中與達(dá)到穩(wěn)定狀態(tài)前出現(xiàn)的較為嚴(yán)重的波動(dòng),測(cè)試其他電壓,也發(fā)現(xiàn)類似情況。

從圖1、圖2可以分析到,F(xiàn)PGA在上電過程中需要自檢電壓,一旦所有要求的電壓值大于某個(gè)范圍就開始加載,而此時(shí)如果電壓波動(dòng)較大,那么FPGA可能會(huì)加載失敗,因?yàn)楫?dāng)波動(dòng)的電壓處于波峰時(shí)FPGA快速檢查電壓并可能通過,在FPGA加載正進(jìn)行到下面某一步時(shí),電壓值突然下降直至波谷,那么FPGA的后續(xù)加載操作將異常。當(dāng)然,現(xiàn)在不少FPGA在上電自檢的時(shí)候都有個(gè)監(jiān)測(cè)電壓是否穩(wěn)定的過程,加載失敗的情況基本上很少,不過大部分的FPGA對(duì)電壓都有嚴(yán)格的要求。

圖2:電源紋波示例。

c.與b類似,很多ASIC專用芯片、CPLD在上電初始化的時(shí)候都需要有穩(wěn)定的電壓,這里不再累述,可以參閱相關(guān)芯片資料。

2.采用單電源模塊設(shè)計(jì)的電路

目前在系統(tǒng)設(shè)計(jì)中,為了兼容各種電壓也常采用48-5V單電源模塊和加直流電壓轉(zhuǎn)換器的方案。其實(shí)采用單電源模塊的設(shè)計(jì)同樣面臨上面提到的問題。單電源模塊也存在上電順序先后的問題。因?yàn)殡娫茨K直接輸出5V,其他電壓值通過直流電壓轉(zhuǎn)換器轉(zhuǎn)換,因此小于5V的電壓上電肯定晚于5V。

在蓄電池供電的情況下,由于蓄電池的本身特性,在上電的時(shí)候其電壓是緩慢上升的,由于現(xiàn)在DC-DC模塊的設(shè)計(jì)差異,某些模塊在慢上電的過程中出現(xiàn)的電壓擺動(dòng)仍然會(huì)影響FPGA和ASIC的初始化。

解決方法

對(duì)應(yīng)可能出現(xiàn)的問題,可以找到相應(yīng)的解決方法。在前文分析的第一種情況(采用多電源模塊)下,對(duì)應(yīng)a,可以復(fù)位MCU;對(duì)應(yīng)b,可以復(fù)位FPGA;對(duì)應(yīng)c,可以復(fù)位相關(guān)芯片。對(duì)于第2種情況(采用單電源模塊),復(fù)位相應(yīng)的芯片也可以解決問題。所以最直接有效的方法就是復(fù)位。

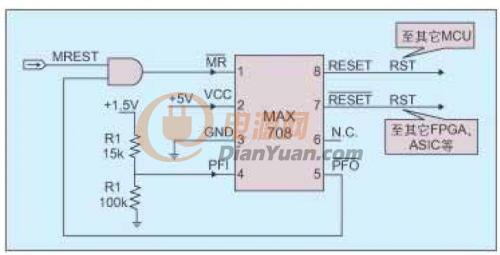

當(dāng)然我們不可能等到故障出現(xiàn)的時(shí)候再去手動(dòng)復(fù)位,這里可以考慮使用Maxim公司的MAX708芯片來完成自動(dòng)復(fù)位的功能。

MAX708是一種微處理器電源監(jiān)控芯片,可同時(shí)輸出高電平有效和低電平有效的復(fù)位信號(hào)。復(fù)位信號(hào)可由VCC 電壓、手動(dòng)復(fù)位輸入或由獨(dú)立的比較器觸發(fā)。獨(dú)立的比較器可用于監(jiān)視第二個(gè)電源信號(hào)。在電路設(shè)計(jì)中,MCU單元一般由51單片機(jī)構(gòu)成,單片機(jī)的復(fù)位信號(hào)是高有效。一般FPGA和ASIC的復(fù)位信號(hào)都是低有效。由于MAX708可同時(shí)輸出高電平有效和低電平有效的復(fù)位信號(hào),因此可以利用MAX708的這個(gè)特點(diǎn)來解決電路內(nèi)MCU、FPGA、ASIC的上電復(fù)位問題。

如圖3所示,當(dāng)PFI端子上的電壓值小于1.25V時(shí),PFO端子將輸出低電平(平時(shí)為高)。由于PFI端子的這個(gè)特性,可以用它來監(jiān)控電路上的1.5V電壓。在通信設(shè)備里,電路上一般含有5V、3.3V、2.5V、1.8V、1.5V的電壓值,1.5V應(yīng)該屬于末級(jí)電壓,就是說通過直流電壓轉(zhuǎn)換器最后轉(zhuǎn)壓出來的,我們監(jiān)控了最小電壓(1.5V),自然也就不必理會(huì)它的上級(jí)電壓了。

圖3:利用MAX708實(shí)現(xiàn)上電復(fù)位應(yīng)用。

這里PFI上的電壓值大概為1.3V,當(dāng)然電壓值越接近1.25V,電壓監(jiān)控的靈敏度越高。可以用公式{(Vsupply-VPFI)/R1}=(VPFI/R2)計(jì)算出需要的電阻比值。這里Vsupply為1.5V,VPFI為1.3V。

可以想象,電路上電過程中,1.5V的末級(jí)電壓如果沒有達(dá)到要求,復(fù)位信號(hào)將一直存在,包括給MCU的RST復(fù)位信號(hào),和給其它芯片的低電平有效的復(fù)位信號(hào)。圖3中的MREST為手動(dòng)添加的復(fù)位信號(hào)。

需要指出的是,MAX708本身可以監(jiān)控VCC電壓(這里為5V),這對(duì)電路采用多電源模塊的設(shè)計(jì)是很有用的。因?yàn)閮蓚€(gè)電源模塊相互獨(dú)立,5V和1.5V可能不是源于同一個(gè)電源模塊,所以在監(jiān)控1.5V的同時(shí)也需要監(jiān)控5V電壓。

當(dāng)然,由于MAX708芯片本身的限制,它無法監(jiān)控小于1.25V的電壓。但是在電信級(jí)設(shè)備中,功耗問題并不很迫切,所以這樣小的電壓基本上應(yīng)用很少。

本文小結(jié)

電源波動(dòng)造成的電路上電失敗故障,只是涉及電源可靠性的一個(gè)方面。這里舉的一個(gè)實(shí)際應(yīng)用的例子可能并不適合于各種情況,其目的只是在于提醒設(shè)計(jì)人員在有關(guān)電源設(shè)計(jì)中可能存在的隱患。現(xiàn)在,F(xiàn)PGA和ASIC在降低功耗的同時(shí),也具有越來越多的驅(qū)動(dòng)電壓,某些器件還特別對(duì)各種電壓的上電順序有嚴(yán)格的要求。硬件工程師在應(yīng)用這些器件進(jìn)行系統(tǒng)功能設(shè)計(jì)的同時(shí),也將越來越多的面臨如何提高電源可靠性方面的挑戰(zhàn)。