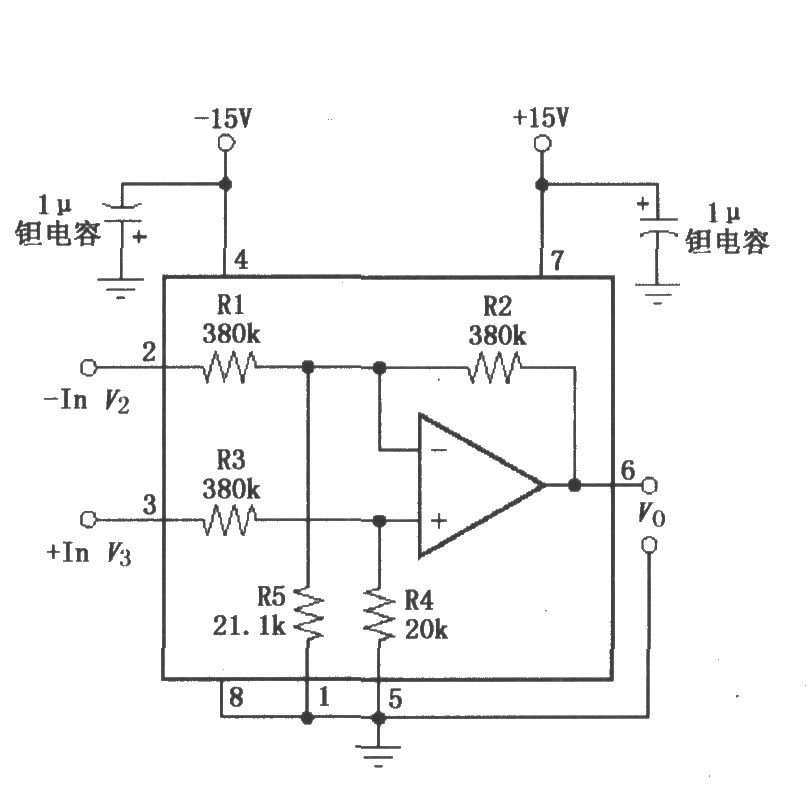

如圖所示為INA117的基本電源和信號連接電路。在噪聲環(huán)境或高阻電源應用時,芯片電源端要用電容濾波,且應盡可能靠近芯片電源腳放置。輸出電壓等于2腳與3腳之間的差分電壓,即Vo=V3-V2,由此共模電壓被抑制。芯片內(nèi)部電路連接補償腳(8腳),用以消除反饋電阻R2與IC襯底之間寄生分布電容。通常8腳接地或通過0.1μF接到交流地(如V )。INA117的共模抑制比是依靠輸入電阻網(wǎng)絡的匹配來實現(xiàn)的。為了保持高CMR,應該使用低阻信號源驅動兩個輸入端。 當有一個75Ω電阻串聯(lián)在2腳或3腳時,將使CMR從86dB降低到72dB。同樣,當有一個電阻串聯(lián)在基準腳 1腳或5腳時,也造成CMR下降。例如,有一個4Ω電阻串聯(lián)在1腳或5腳也將使CMR從86dB降低到72dB。

如圖所示為INA117的基本電源和信號連接電路。在噪聲環(huán)境或高阻電源應用時,芯片電源端要用電容濾波,且應盡可能靠近芯片電源腳放置。輸出電壓等于2腳與3腳之間的差分電壓,即Vo=V3-V2,由此共模電壓被抑制。芯片內(nèi)部電路連接補償腳(8腳),用以消除反饋電阻R2與IC襯底之間寄生分布電容。通常8腳接地或通過0.1μF接到交流地(如V )。INA117的共模抑制比是依靠輸入電阻網(wǎng)絡的匹配來實現(xiàn)的。為了保持高CMR,應該使用低阻信號源驅動兩個輸入端。 當有一個75Ω電阻串聯(lián)在2腳或3腳時,將使CMR從86dB降低到72dB。同樣,當有一個電阻串聯(lián)在基準腳 1腳或5腳時,也造成CMR下降。例如,有一個4Ω電阻串聯(lián)在1腳或5腳也將使CMR從86dB降低到72dB。