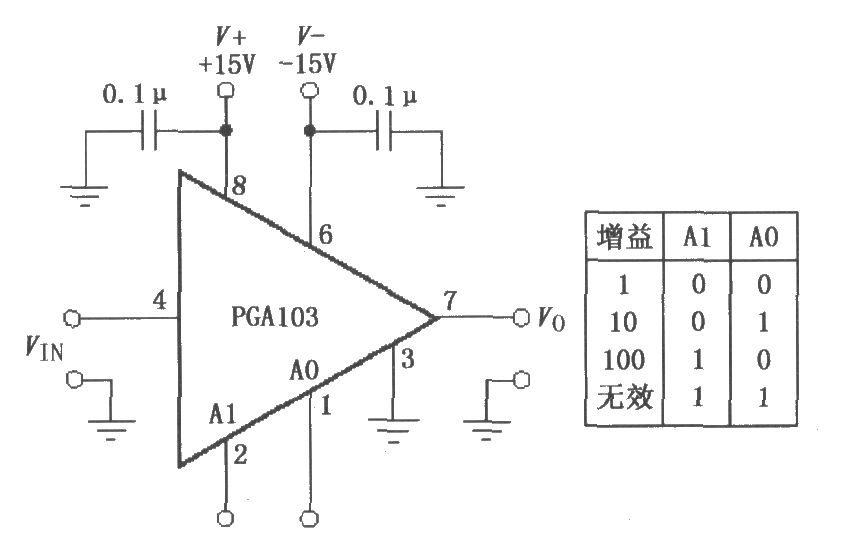

如圖所示為PGA103電源和信號(hào)的基本連接電路,Vo=GVIN。信號(hào)VIN由④腳輸入,經(jīng)過放大后從⑦腳輸出。輸入和輸出都以地(③腳)為參考,③腳的接地電阻必須是低阻,以確保良好的增益精確度。例如,在增益G=100時(shí),若串聯(lián)接地電阻為0.1Ω,將造成增益精確度下降0.2%。數(shù)字輸入端可以直接接CMOS或TTL器件,數(shù)字輸入端A0、A1的不同編碼組合可以選擇增益1、10、100。當(dāng)A0=A1=1時(shí)為無效輸入,此時(shí)雖不會(huì)損壞器件,但是輸出為不確定狀態(tài)。當(dāng)編碼組合正確時(shí),輸出端立即恢復(fù)有效編碼選擇。

邏輯“0”指電壓為-5.6~0.8V,邏輯“1”為1.2V~V 。數(shù)字輸入端沒有鎖存,所以當(dāng)數(shù)字邏輯輸入發(fā)生變化時(shí),輸出端立即選擇相應(yīng)的增益。邏輯轉(zhuǎn)換時(shí)間約為0.5μs,這個(gè)響應(yīng)增益變化的時(shí)間等于轉(zhuǎn)換時(shí)間加上選擇增益后放大器輸出電壓的建立時(shí)間。在許多應(yīng)用場合,通過在PGA103輸入端外加鎖存器來鎖存增益控制信號(hào),隔離敏感的模擬電路與高速數(shù)據(jù)總線,以滿足模擬電路與快速數(shù)據(jù)總線連接的需求。

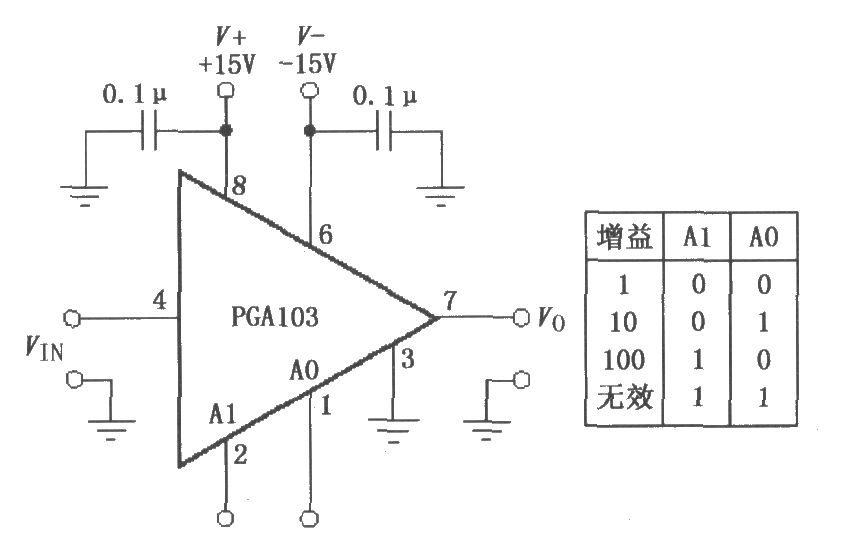

如圖所示為PGA103電源和信號(hào)的基本連接電路,Vo=GVIN。信號(hào)VIN由④腳輸入,經(jīng)過放大后從⑦腳輸出。輸入和輸出都以地(③腳)為參考,③腳的接地電阻必須是低阻,以確保良好的增益精確度。例如,在增益G=100時(shí),若串聯(lián)接地電阻為0.1Ω,將造成增益精確度下降0.2%。數(shù)字輸入端可以直接接CMOS或TTL器件,數(shù)字輸入端A0、A1的不同編碼組合可以選擇增益1、10、100。當(dāng)A0=A1=1時(shí)為無效輸入,此時(shí)雖不會(huì)損壞器件,但是輸出為不確定狀態(tài)。當(dāng)編碼組合正確時(shí),輸出端立即恢復(fù)有效編碼選擇。

邏輯“0”指電壓為-5.6~0.8V,邏輯“1”為1.2V~V 。數(shù)字輸入端沒有鎖存,所以當(dāng)數(shù)字邏輯輸入發(fā)生變化時(shí),輸出端立即選擇相應(yīng)的增益。邏輯轉(zhuǎn)換時(shí)間約為0.5μs,這個(gè)響應(yīng)增益變化的時(shí)間等于轉(zhuǎn)換時(shí)間加上選擇增益后放大器輸出電壓的建立時(shí)間。在許多應(yīng)用場合,通過在PGA103輸入端外加鎖存器來鎖存增益控制信號(hào),隔離敏感的模擬電路與高速數(shù)據(jù)總線,以滿足模擬電路與快速數(shù)據(jù)總線連接的需求。

如圖所示為PGA103電源和信號(hào)的基本連接電路,Vo=GVIN。信號(hào)VIN由④腳輸入,經(jīng)過放大后從⑦腳輸出。輸入和輸出都以地(③腳)為參考,③腳的接地電阻必須是低阻,以確保良好的增益精確度。例如,在增益G=100時(shí),若串聯(lián)接地電阻為0.1Ω,將造成增益精確度下降0.2%。數(shù)字輸入端可以直接接CMOS或TTL器件,數(shù)字輸入端A0、A1的不同編碼組合可以選擇增益1、10、100。當(dāng)A0=A1=1時(shí)為無效輸入,此時(shí)雖不會(huì)損壞器件,但是輸出為不確定狀態(tài)。當(dāng)編碼組合正確時(shí),輸出端立即恢復(fù)有效編碼選擇。

邏輯“0”指電壓為-5.6~0.8V,邏輯“1”為1.2V~V 。數(shù)字輸入端沒有鎖存,所以當(dāng)數(shù)字邏輯輸入發(fā)生變化時(shí),輸出端立即選擇相應(yīng)的增益。邏輯轉(zhuǎn)換時(shí)間約為0.5μs,這個(gè)響應(yīng)增益變化的時(shí)間等于轉(zhuǎn)換時(shí)間加上選擇增益后放大器輸出電壓的建立時(shí)間。在許多應(yīng)用場合,通過在PGA103輸入端外加鎖存器來鎖存增益控制信號(hào),隔離敏感的模擬電路與高速數(shù)據(jù)總線,以滿足模擬電路與快速數(shù)據(jù)總線連接的需求。