重構控制器硬件系統(tǒng)組成

本文介紹一種基于“ARM處理器+FPGA”架構的重構控制器,重構控制器中的FPGA能夠根據(jù)ARM處理器傳送來的命令,對目標可編程器件JTAG接口進行控制,并模擬JTAG接口中TAP狀態(tài)機產(chǎn)生激勵信號(TMS、TDI、TCK序列),向目標可編程器件的JTAG接口提供所需的激勵,使目標可編程器件內(nèi)的TAP狀態(tài)機進行狀態(tài)轉(zhuǎn)換,將指令和數(shù)據(jù)掃描到FPGA內(nèi)部邊界掃描電路指令寄存器和數(shù)據(jù)寄存器中。完成一次目標可編程器件配置,實現(xiàn)用戶此時所要求功能,在下一時段,可根據(jù)用戶新的要求,調(diào)用重構控制器內(nèi)部存儲器中不同方案在系統(tǒng)重新配置目標可編程器件,實現(xiàn)硬件的時分復用,靈活快速的改變系統(tǒng)功能,節(jié)省邏輯資源,滿足大規(guī)模應用需求。

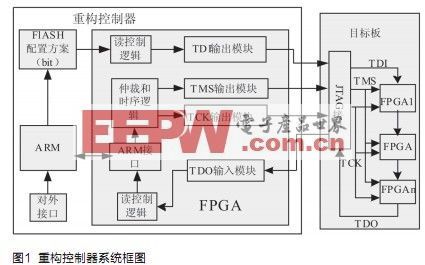

其主要功能是控制按照用戶不同需求調(diào)用不同的方案配置目標可編程器件。它主要包括ARM處理器、FPGA、Flash存儲器,各功能部件主要功能如下:

(1) ARM處理器,其主要功能是控制模擬JTAG接口的FPGA讀取Flash存儲器中的重構方案,實現(xiàn)在系統(tǒng)配置;

(2) FPGA協(xié)處理器選用Xilinx公司SPARTEN3AN系列,是基于非易失性存儲的FPGA,自身帶有PROM,它作為外部總線和ARM控制器之間的雙端口,主要功能是模擬JTAG接口實現(xiàn)TAP控制器時序,完成配置方案數(shù)據(jù)的并串轉(zhuǎn)換并輸出至外部總線;

(3)FLASH存儲器容量為32M×16bit,用于處理器的上電引導、存放多種重構配置方案。由于要求的存儲容量較大,采用SPANSION公司[1]S29GL512P(32M×16bit)的存儲空間,訪問速度110ns,可以達到25ns快速頁存取和相應的90ns隨機存取時間;

(4) 測試線TCK 、TMS 、TDI 和TDO,是重構控制器向目標可編程器件提供所需的JTAG TAP 激勵,分別控制目標多個FPGA的重構配置和反饋重構信息。

系統(tǒng)實現(xiàn)

重構控制器

本文設計的重構控制器采用ARM微處理器作為主控制器,以FPGA芯片作為協(xié)處理器配合主控制器工作。用戶事先根據(jù)需求設計出不同的配置方案,并存儲在重構控制器內(nèi)部的存儲器中,上電后,重構控制器就可以按需求將不同設計方案分時定位到目標可編程器件內(nèi),同時保持其他部分電路功能正常,實現(xiàn)在系統(tǒng)靈活配置,提高系統(tǒng)工作效率。

重構控制器框圖如圖1所示。ARM執(zhí)行的初始化工作包括程序更新加載運行,F(xiàn)PGA參數(shù)設定等(見圖2)。FPGA初始化包括設定內(nèi)部命令寄存器和邏輯狀態(tài)的初始值、內(nèi)部緩沖區(qū)數(shù)據(jù)清零等。ARM處理器一方面通過ARM總線讀取外部Flash中的配置方案,將其存儲到TDI模塊的緩存中;另一方面重構控制器中模擬TAP控制器的FPGA,通過執(zhí)行ARM處理器發(fā)出的配置指令,模擬產(chǎn)生TCK 、TMS 、TDI 和TDO信號,作為目標可編程器件的JTAG接口激勵,與目標可編程器件的JTAG口串聯(lián)成菊花鏈,對目標可編程器件進行在系統(tǒng)編程。

重構控制器模塊

ARM接口模塊

如圖1所示,ARM接口模塊主要作為FPGA和ARM處理器之間的接口,完成ARM的命令控制和參數(shù)傳遞。當系統(tǒng)上電后,ARM處理器將預先設定好的各種配置信息傳送至ARM接口模塊,完成對FPGA及各外圍模塊進行配置。系統(tǒng)正常運行時,該模塊處于閑置狀態(tài)。直到ARM處理器請求進行新的配置時,ARM接口模塊再次傳遞新的配置信息,完成目標板重新配置。

仲裁與時序控制模塊

仲裁與時序控制模塊主要完成對重構控制器內(nèi)部各模塊的仲裁與時序控制。協(xié)調(diào)各模塊之間的數(shù)據(jù)流向。其具體的功能包括提供內(nèi)部各模塊所需的時鐘信號,并進行相應的時序控制;以及對內(nèi)部數(shù)據(jù)流的切換控制。

TCK,TMS,TDI,TDO產(chǎn)生模塊

TCK: JTAG配置時鐘輸入,所有基于JTAG的操作都必須同步于JTAG時鐘信號TCK。關鍵時序關系是:TMS和TDI采樣于TCK的上升邊沿,一個新的 TDO值將于TCK下降邊沿后出現(xiàn),因此一般情況下JTAG的時鐘不會太高。

TMS:模式選擇,控制JTAG狀態(tài)轉(zhuǎn)移,同步時鐘TCK上升沿時刻TMS的狀態(tài)決定狀態(tài)轉(zhuǎn)移過程。

TDI :配置數(shù)據(jù)輸入,配置數(shù)據(jù)在TCK的上升沿采樣進入數(shù)據(jù)移位寄存器(SDR);

TDO:配置數(shù)據(jù)輸出,在TCK的下降沿從移位寄存器移出,輸出數(shù)據(jù)與輸入到TDI的數(shù)據(jù)應不出現(xiàn)倒置。

目標板

目標板上被重構的FPGA由支持重構的Xilinx公司的VIRTEX-4" title="VIRTEX-4">VIRTEX-4系列FPGA來實現(xiàn),以菊花鏈方式串聯(lián),支持JTAG邊界掃描模式配置。

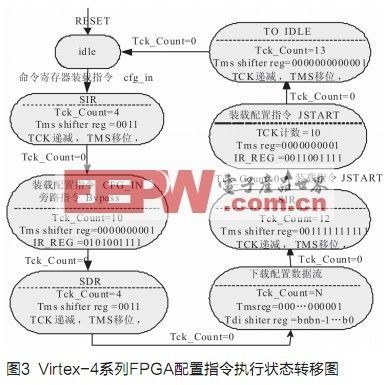

JTAG邊界掃描配置的FPGA實現(xiàn)

TAP控制器是16個狀態(tài)的有限狀態(tài)機,主要為JTAG接口提供控制邏輯。主要有四大狀態(tài):復位(RESET),空閑(idle),數(shù)據(jù)寄存器移位(SDR)和指令寄存器移位(SIR)狀態(tài), 在TCK,TMS的控制下,根據(jù)輸入的配置指令實現(xiàn)狀態(tài)的轉(zhuǎn)移。Xlinx公司Virtex4系列 FPGA器件的邊界掃描指令集中有三條專用于配置的邊界掃描指令:CFG_IN、BYPASS和JSTART(10個bit位)。其中CFG_IN的代碼:0101001111;BYPASS的代碼:1111111111;JSTART的代碼:0011001111。執(zhí)行CFG_IN指令可以訪問器件內(nèi)部的配置總線,通過串行移入配置文件中的命令和數(shù)據(jù)執(zhí)行對內(nèi)部配置寄存器的讀寫,從而完成對FPGA的配置。BYPASS指令在對多個目標器件配置時可以旁路不需要重配置的器件。JSTART指令使用TCK時鐘觸發(fā)啟動時序,使FPGA完成從配置狀態(tài)到操作狀態(tài)的轉(zhuǎn)換,激活FPGA。圖3為可重構控制器模擬TAP狀態(tài)機配置指令執(zhí)行的狀態(tài)轉(zhuǎn)移圖。

系統(tǒng)仿真

仿真在Active-HDL7.1軟件下運行,所有仿真是基于對單器件配置的過程。

圖4為JTAG邊界掃描方式核心控制TAP狀態(tài)機仿真波形 ,本文把整個下載模擬過程設計為三步,分別為TAP_Reset、TAP_CFG、TAP_JStart,ARM分別給三步提供一個啟動命令,三個步驟分時按順序由自己獨立的狀態(tài)機實現(xiàn),由圖可以看出狀態(tài)銜接正確。

圖5為各狀態(tài)機個狀態(tài)下接口輸出波形,TCK、TMS、TDI時序和輸出值滿足JTAG掃描方式配置Virtex-4系列FPGA接口激勵要求。

本系統(tǒng)ARM工作時鐘為50MHz,TCK輸出為25MHz,為便于觀察,TAP_CFG部分狀態(tài)機中SDR狀態(tài)項實際由配置方案文件bit位數(shù)決定,仿真圖有所壓縮。

如果目標板FPGA是Virtex-4 XC4VLX25" title="XC4VLX25">XC4VLX25,其配置方案文件為995KB,整個配置過程大約所需時間327ms。

結語

本文介紹的重構控制器具有相對通用性,適用于對同一類FPGA芯片實現(xiàn)可編程器件在系統(tǒng)配置,使得硬件信息(可編程器件的配置信息)也可以象軟件程序一樣被動態(tài)調(diào)用或修改,從而動態(tài)的改變電路的結構和功能,對電路中出現(xiàn)的錯誤和故障進行實時動態(tài)重構,達到高可靠性的目的,有效節(jié)省邏輯資源,通過設計和仿真驗證了此方法的可行性。