視頻采集系統(tǒng)在工業(yè)領(lǐng)域應(yīng)用廣泛,隨著多媒體技術(shù)的快速發(fā)展,對視頻采集、處理和傳輸性能的要求也不斷提高,如高采集速度、低功耗、抗干擾性、實時性及擴展性等。這里提出了以Virtex-5為核心,由ADV7188為視頻解碼器,PCIExpress為傳輸總線組成的集視頻采集、壓縮、傳輸于一體的多功能視頻處理系統(tǒng)。該系統(tǒng)能夠?qū)崿F(xiàn)實時海量傳輸多路數(shù)字視頻。Virtex-6支持的PCI Express的×1通道的傳輸率已達3.2Gb/s。

由于該系統(tǒng)設(shè)計體積小、功耗低且滿足工況要求,可應(yīng)用于公共場合、工廠和井下作業(yè)等需多點遠距離監(jiān)控環(huán)境較惡劣場所。

1 PCI Express總線簡介

PCI Express是一種主流的串行標(biāo)準(zhǔn),它是2002年問世的第三代I/O互聯(lián)技術(shù),為從PCI到PCIX提供了一條升級路徑。PCI Express是PC產(chǎn)業(yè)的標(biāo)準(zhǔn)互聯(lián)技術(shù),具有可升級能力,可擴展的功能集,很強的市場適應(yīng)能力和低成本等特性。其高速串行標(biāo)準(zhǔn)能以每條通道2.5 Gb/s的線速進行雙向通信,分層數(shù)據(jù)包的架構(gòu)有助于模塊化設(shè)計。通過更簡單的升級就能實現(xiàn)帶寬增強(高達80 GB)——1、2、4、8、16和32條通道。PCI Express的先進功能,比如可靠性、電源管理和熱插拔,借助虛擬通道、業(yè)務(wù)等級和服務(wù)質(zhì)量(QoS)等特性支持下一代三維/多媒體業(yè)務(wù)。

2 系統(tǒng)硬件設(shè)計

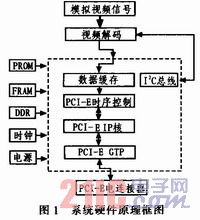

該系統(tǒng)設(shè)計采用視頻解碼器+FPGA,其功能是接收PAL等制式模擬視頻信號,轉(zhuǎn)換為滿足ITU-R BU.656格式的數(shù)字信號,將多路視頻打包,經(jīng)PCI Express總線傳輸?shù)接嬎銠C。

這里采用ADV7188來采集PAL制式的視頻信號,Videx-5的I2C總線控制器通過I2C總線來對其進行配置和控制。選用Virtex-5系列中的XC5-VFX30T,此器件具有強大的處理能力和豐富的外部設(shè)備接口,能滿足各種不同應(yīng)用環(huán)境的控制與圖像輸出需要。Virtex-5器件具有視頻處理IP核,可以按照使用要求配置,同時具有PCI Express、PPC440等IP核,PPC440在667MHz的時鐘主頻下,數(shù)字處理能力可達到1600DMI/s,內(nèi)部具有256 KB的SRAM。Virtex-5具有2條I2C接口,多達8條(32 bit)具有主控器的外設(shè)總線接口,支持外部、內(nèi)部和內(nèi)存間的DMA方式,2條

10/100/100 Mb/s半或全雙工以太網(wǎng)接口,圖1為該系統(tǒng)設(shè)計硬件原理框圖。

3 主要組成部分的原理實現(xiàn)

3.1 視頻采集處理電路

3.1.1 視頻解碼器選型

在選擇視頻解碼器時,主要考慮功能、性能、尺寸、性價比及低功耗等方面,故選擇了ADV7188型視頻解碼器件。該器件具有以下特性:

可以自動檢測到NTSC-M/J/4.43,PAL-M/N/B/G/H/I/D和SECAM制式信號的輸入;單一時鐘28.636 36 MHz;4路模擬視頻12位AD采集;5線自適應(yīng)梳狀濾波;

降低數(shù)字噪聲;集成有自適應(yīng)白電平峰值的自動增益控制器;具有鎖定較弱的、噪聲和不穩(wěn)定視頻源的設(shè)計;12路模擬輸入通道;輸入視頻信號幅度,為0.5~1.5 V;在沒有輸入視頻信號情況下可以自行產(chǎn)生行場同步信號;亮度帶寬邊緣增強是可編程的;色調(diào)、對比度、亮度、飽和度可編程;YCbCr以20/16/10/8位4:2:2形式輸出;支持工業(yè)標(biāo)準(zhǔn)的I2C接口;電源為+3.3 V,1.8 V;下電模式;采用80引腳,無鉛的LQFP封裝;工作溫度為-40~+85℃。

3.1.2 視頻采集電路工作原理

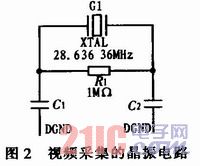

視頻采集電路是以為ADV7188為核心,采集多路的PAL、NTSC或SECAM制式模擬視頻信號,具有增強較弱的模擬視頻信號,可進行降噪處理和提高數(shù)字視頻信號質(zhì)量的功能。AD7188的詳細電路可參見ADV7188的器件手冊。由于ADV7188對電源要求較高,該系統(tǒng)設(shè)計對電源進行隔離、去耦、低頻濾波等處理。為了廣泛應(yīng)用,這里采用頻率為28.636 36 MHz的石英晶體諧振器,頻差為±20 ppm。圖2為視頻平裝的晶振電路。

根據(jù)PCB布線,Cstray通常為2~3pF,ADV7188器件管腳到電源地的電容值Cpg為4 pF,石英晶體諧振器的負(fù)載電容Cload為15 pF。由C1= C2=2(Cload-Cstray)-Cpg可計算出C1和C2的電容值為24 pF,按照E12系列的優(yōu)選值,選取電容值為22pF。

設(shè)計中利用ADV7188的下電模式,當(dāng)此片沒有模擬視頻輸入或不需工作時,將其下電,其功耗將由工作時的0.6 W降到1 mW左右,能極大地減少系統(tǒng)待機功耗。

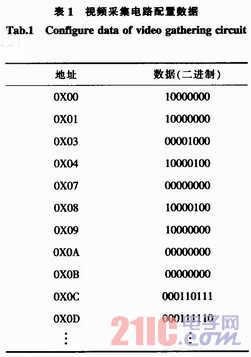

3.1.3 視頻采集電路的配置

在FPGA內(nèi)設(shè)計I2C總線控制器,配置為和視頻解碼器I2C接口時鐘一致的接口總線。通過FPGA上電配置,達到對FPGA內(nèi)的FIFO初始化,初始化數(shù)據(jù)為視頻采集電路的配置數(shù)據(jù),配置數(shù)據(jù)見表1。

3.2 FPGA

3.2.1 FPGA器件選型

FPGA型號的選擇主要基于以下方面考慮:具有PCIExpress總線;通道不低于x8;具有嵌入式微處理器;合適的I/O管腳數(shù)和資源,支持所需的電平標(biāo)準(zhǔn);具有較低的功耗;合適的性價比。

因此,選擇Xilinx公司的Virtex-5系列的XC5VFX3-0T,封裝為FF665 PCI Express總線;具有PowerPC440嵌入微處理器。配置芯片選用容量為1 GB的CF卡。

3.2.2 FPGA的性能和資源

1)時鐘資源32條全局時鐘總線,對整個器件上的所有資源進行時鐘控制,且可以驅(qū)動邏輯信號;

2)時鐘管理技術(shù) 時鐘去歪斜、頻率合成、相移和動態(tài)重配置等功能;

3)鎖相環(huán)作為廣譜頻率的頻率合成器,并且與CMT的DCM配合作為外部或內(nèi)部時鐘的抖動濾波器;

4)BLOCK RAM 2 448 Kb,可配置為RAM、雙口RAM和FIFO等,且其內(nèi)容能夠初始化;

5)可配置邏輯塊 實現(xiàn)組合邏輯和時序邏輯的主要資源;

6)SelectIO資源 可支持種類繁多的標(biāo)準(zhǔn)接口。包括輸出強度和斜率的可編程控制以及實現(xiàn)數(shù)控阻抗的片上終端;

7)SelectIO邏輯資源 包括組合輸入/輸出、三態(tài)輸出控制、寄存輸入/輸出、寄存三態(tài)輸出控制、DDR輸入/輸出和DDR輸出三態(tài)控制;

8)高級SelectIO邏輯資源 輸入串并轉(zhuǎn)換和輸出并串轉(zhuǎn)換;

9)DSP邏輯片 64個550 MHz DSP48E slice,每個DP48E包括1個28x18的乘法器、1個加法器和1個累加器。利用Xilinx ISE的FPGA Edit也可觀察FPGA的內(nèi)部結(jié)構(gòu)。

3.3 數(shù)據(jù)緩存

由于PCI Express的總線波特率為2.5 Gbps,遠大于1路采集后的數(shù)字視頻信號。當(dāng)視頻數(shù)據(jù)經(jīng)并行總線傳入FPGA內(nèi),通過配置為異步輸入輸出的FIFO進行數(shù)據(jù)緩存,提高總線使用效率。如果PCI Express總線為×1通道,PAL制式視頻轉(zhuǎn)換為常用的8位4:2:0的YUV格式數(shù)字視頻,按照PCIExpress總線傳輸有效數(shù)據(jù)1.62 Gb/s計算,理論上可以傳輸36路。

3.4 FCI Express接口實現(xiàn)

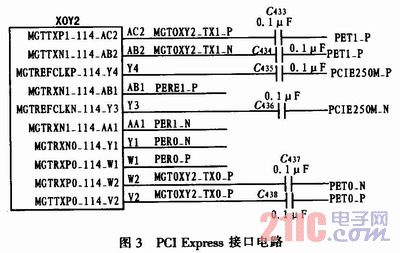

利用具有PCI Express的FPGA來設(shè)計,選用Xilinx公司的Virtex-5 LXT系列的FPGA,利用其內(nèi)的PCI Express IP核進行設(shè)計,完成功能如下:用戶接口的本地鏈路成幀接口;64位數(shù)據(jù)總線寬度與3位提醒總線;包化接口,帶用于標(biāo)記包的幀起始(SOF)和幀結(jié)束(EOF);傳輸和接收方向用戶接口的包中斷特性;幀錯誤檢測支持;多通道配置支持:×1、×2、×4和×8;這里通道配置為×1;每通道1.62 Gb/s或更高的吞吐量;利用集成端點模塊中的自動協(xié)商功能,可以在某些通道不能工作時使設(shè)計使用較低的帶寬;物理層中使用的8B/10B解碼和解碼。此方案雖開發(fā)難度大、周期長,但具有外電路圍簡單,硬件成本低,設(shè)計靈活、集成度高且易升級等特點。其接口電路如圖3所示。

3.5 時鐘

本設(shè)計需要4個時鐘信號,其中視頻解碼信號的時鐘要求最高,時鐘精度必須在±50 ppm以內(nèi),其次為PCI Express總線工作的時鐘頻率。在FPGA內(nèi)對時鐘信號進行了DCM和PLL處理,完成了對時鐘信號的去歪斜、相移和頻率合成等功能。

3.6 Flash和DDRSDRAM

為使設(shè)計具有靈活性、擴展性和升級性,預(yù)留了Flash和SDRAM來存儲程序和運行程序,滿足智能性和易于以太網(wǎng)遠程控制等要求。

3.7 以太網(wǎng)接口電路

通過FPGA+PHY+變壓器組成以太網(wǎng)接口電路,可以用此接口加載程序,也可用此接口和互聯(lián)網(wǎng)連接。利用XILINX公司的FPGA開發(fā)軟件ISE,通過FPGA內(nèi)IP核按照TriMode Ethemet MAC進行。

3.8 DMA傳輸

本設(shè)計采用DMA方式進行數(shù)據(jù)內(nèi)部傳輸。數(shù)字視頻信號經(jīng)并行總線傳入FPGA內(nèi),通過FIFO進行數(shù)據(jù)緩存,經(jīng)DMA方式,通過PCI Express傳給計算機。

3.9 FPGA配置方案

Virtex-5的配置方案采用System ACE(System Advandced Configuration Eviroment)中的System ACE CF(CompactFlash)。System ACE使用CF存儲卡保存數(shù)據(jù),通過System ACE控制器把數(shù)據(jù)配置到FPGA中。System ACE CF使用容量為1 GB的CompaetFlash卡,System ACE CF是預(yù)制的配置方案,不需編寫任何程序,只需簡單的調(diào)試即可。此方案把舊的、用于調(diào)試的版本和新版本都裝入到同一塊CF卡中,縮短了研發(fā)周期,便于維修排故,同時把應(yīng)用軟件、產(chǎn)品附帶的說明書等保存到此CF卡中,系統(tǒng)升級可更換CF卡、在系統(tǒng)編程和通過Intemet進行遠程升級。

3.10 電源的設(shè)計

板上需要電源有+3.3、+2.5、+1.8和+1.2 V共5種。其中+3.3 V電源為外部輸入,約20 W;+1.8 V提供給FPGA和ADV7188的二次電源,其他為提供給FPGA的二次電源。+3.3V電源為電源層,提供給FPGA的+2.5V、+1.8 V和+1.2V為電源層分割。提供給ADV7188的+1.8V電源電流按照0.5A設(shè)計,實際典型值為100 mA。去耦電容和對應(yīng)的元器件同層放置,減少過孔的影響。

3.11 PCB設(shè)計

PCB布線遵循信號完整性的設(shè)計要求。PCB共10層,首先設(shè)計電源層和地層,其中電源層2層,地平面4層,對稱分布。除以太網(wǎng)變壓器外其他所有工作電源的地為一個地,保證地平面的完整性。

由于PCI Express總線為2.5Gb/s,對Virtex-5引腳分配時,使PCI Express的引腳在其內(nèi)的布線盡可能的短。在PCB的布局時使Virtex-5靠近PCI Express總線接口的電連接器,差分線對的實際長度不大于30 mm。PCB布線時要嚴(yán)格控制差分線對的長度差,為了避免信號往返的延遲不超過其上升時間,導(dǎo)致過沖和振鈴發(fā)生,PCB布線根據(jù)PCI Express信號的特性,定義差分對長度差不超過1 mm,實際布線結(jié)果不超過0.2 mm。PCB上的差分阻抗為(100±10)Ω,符合PCIExpress規(guī)范單端阻抗為(50±10)Ω的要求。

3.12 操作系統(tǒng)

本設(shè)計中的FPGA具有PPC440核,采用實時多任務(wù)操作系統(tǒng)(Vxworks),根據(jù)實際使用要求,從Vxworks系統(tǒng)內(nèi)核(wind)的任務(wù)管理、通信機制、系統(tǒng)配置、系統(tǒng)接口幾個方面進行設(shè)計,保證系統(tǒng)的安全性和可靠性。本設(shè)計已具備成熟的Vxworks操作系統(tǒng)。

3.13 FPGA的調(diào)試

FPGA的開發(fā)包括過程管理與設(shè)計輸入、仿真、綜合、約束、實現(xiàn)、布局布線與配置調(diào)試,其中FPGA的調(diào)試占用設(shè)計周期的80%左右。ISE附帶的高級組件,包括在線調(diào)試(ChipScope Pro)、平面布局規(guī)劃器(PlanAhead)、時序分析器(Timing Analyzer)、布局規(guī)劃器(FloorAhead)、底層編輯器(FPGA Editor)、和功耗分析器(Xpower),以及第三方軟件ModelSim,有效地使用相應(yīng)工具,加速了設(shè)計進程,避免重新設(shè)計,有效提高設(shè)計生產(chǎn)力,并顯著提高設(shè)計性能,降低功耗后將降低系統(tǒng)的整體成本。

4 采集、傳輸和驗證

視頻信號發(fā)生器產(chǎn)生的一種模擬視頻信號如圖4所示。通過模擬視頻信號的采集、總線傳輸過程,計算機顯示器顯示的數(shù)字視頻如圖5所示,和監(jiān)視器顯示的模擬視頻圖像相同,肉眼無法區(qū)分其差別,滿足使用要求。采集模擬視頻的多種標(biāo)準(zhǔn)檢測畫面,顯示正常無畸變,證實本設(shè)計的視頻采集和數(shù)據(jù)傳輸達到了期望的結(jié)果。

5 結(jié)束語

隨著多媒體在工業(yè)和商業(yè)等方面的廣泛使用,對視頻信號的采集、數(shù)據(jù)傳輸速度、集成度和可靠性等方面提出了更高的要求。本文設(shè)計的基于PCI Express的視頻采集系統(tǒng),適用于采集較弱或受干擾的視頻信號,集成度高,適合海量視頻數(shù)據(jù)傳輸,解決了傳輸?shù)钠款i問題。