摘要:為了實(shí)現(xiàn)對(duì)武器系統(tǒng)模擬信號(hào)的采集和數(shù)據(jù)分析,根據(jù)PC/104總線的數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)思想,數(shù)據(jù)采集卡以A/D轉(zhuǎn)換器、CPLD和FIFO相結(jié)合來實(shí)現(xiàn)信號(hào)的連續(xù)采集與數(shù)據(jù)傳輸?shù)目刂啤/D轉(zhuǎn)換器實(shí)現(xiàn)信號(hào)的采樣保持和模數(shù)轉(zhuǎn)換,CPLD實(shí)現(xiàn)數(shù)據(jù)采集和存儲(chǔ)過程的控制。實(shí)驗(yàn)結(jié)果表明,該數(shù)據(jù)采集卡操作簡單、實(shí)時(shí)性強(qiáng)、性能穩(wěn)定,可實(shí)現(xiàn)對(duì)被測信號(hào)高速連續(xù)的數(shù)據(jù)采集。

關(guān)鍵詞:數(shù)據(jù)采集;復(fù)雜可編程邏輯器件;FIFO;時(shí)序控制;邏輯控制

O 引言

測試設(shè)備是武器系統(tǒng)中最主要的子系統(tǒng)之一,它的工作正常與否將直接影響到整個(gè)武器系統(tǒng)的作戰(zhàn)性能。在對(duì)武器系統(tǒng)進(jìn)行測試的過程中,需要對(duì)一系列的電壓、電流等模擬量信號(hào)進(jìn)行快速、實(shí)時(shí)的數(shù)據(jù)采集和分析,檢查這些模擬量的指標(biāo)是否符合要求,可以對(duì)武器系統(tǒng)是否發(fā)生故障做出診斷,保證武器系統(tǒng)的正常工作。根據(jù)現(xiàn)代戰(zhàn)爭對(duì)武器系統(tǒng)的作戰(zhàn)需求,提高快速機(jī)動(dòng)保障能力,研制出體積小、結(jié)構(gòu)緊湊、便攜式的測試設(shè)備就成為主要的目標(biāo)。

本文設(shè)計(jì)了一種基于PC/104總線的高速數(shù)據(jù)采集系統(tǒng),其目的在于替代示波器在武器系統(tǒng)測試中的作用。常規(guī)采集方案主要有兩種:

(1)由單片機(jī)直接控制的采集方案,這是最簡單最常用的控制方案。由于每次采樣都要有單片機(jī)的參與,需占用單片機(jī)的時(shí)間,影響其數(shù)據(jù)處理,而且對(duì)于多通道、多個(gè)A/D轉(zhuǎn)換器的控制,因所需處理的信息更多,則更加不方便。

(2)由DMA控制的采集方案。此方案硬件電路復(fù)雜,若與單片機(jī)配合使用,需要單片機(jī)具有總線掛起功能,否則還需要進(jìn)行總線切換,影響數(shù)據(jù)的及時(shí)處理。

綜合以上兩種方案的優(yōu)缺點(diǎn),本數(shù)據(jù)采集卡自動(dòng)采樣硬件電路主要采用可編程邏輯器件CPLD和先進(jìn)先出FIFO(First In First Out)技術(shù)設(shè)計(jì)而成,可以很好地實(shí)現(xiàn)高速數(shù)據(jù)采集。

1 數(shù)據(jù)采集卡總體方案設(shè)計(jì)

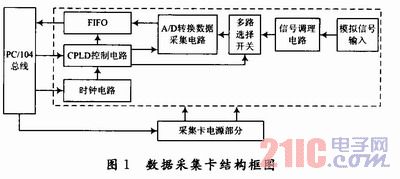

數(shù)據(jù)采集卡是由信號(hào)調(diào)理電路、帶采樣保持器的A/D模數(shù)轉(zhuǎn)換器、多路模擬開關(guān)、FIFO數(shù)據(jù)緩存、CPLD芯片及時(shí)鐘電路等部分組成,具有高精度、高可靠性、高抗干擾能力等特點(diǎn)。總體結(jié)構(gòu)設(shè)計(jì)原理如圖1所示。

2 芯片介紹

該數(shù)據(jù)采集卡采用的芯片主要有:AD9283模/數(shù)轉(zhuǎn)換器、AD508A多路選擇開關(guān)、EPM7128SCL84-6CPLD和CY7C4261 FIFO緩存器。下面對(duì)以上所用芯片做一簡要介紹。

2.1 AD9283模/數(shù)轉(zhuǎn)換器簡介

本數(shù)據(jù)采集卡選用了ANALOG DEVICE公司生產(chǎn)的高速8位模/數(shù)轉(zhuǎn)換器AD9283。它采用先進(jìn)CMOS制作工藝,提供20腳表面貼裝封裝形式。片內(nèi)集成高性能采樣和保持放大器,輸入信號(hào)可采用單輸入或差分輸入;處理輸入電壓峰峰值在0~1 V之間的模擬信號(hào);采用單+3 V模擬電源和單+3 V數(shù)字電源;片內(nèi)提供+1.2~+1.3 V的參考電壓;最高抽樣速率可達(dá)100 MSPS;具有高速并行輸出接口。

2.2 EPM7128SCL84-6 CPLD芯片簡介

本數(shù)據(jù)采集卡選用一片Altera公司生產(chǎn)的EPM7128SLC84-6CPLD作為核心處理芯片,它具有高阻抗、電可擦除等特點(diǎn),可用門單元為2 500個(gè),有64個(gè)用戶可用I/O引腳,工作電壓為+5 V,管腳間最大延遲為5 ns,采用PLCC-84封裝,通過JTAG接口可實(shí)現(xiàn)在線編程。

2.3 CY7C4261 FIFO緩存器簡介

本數(shù)據(jù)采集卡選用的FIFO器件是CYPRESS公司生產(chǎn)的高速、低功耗、先入先出存儲(chǔ)器芯片CY7CA261。它的容量為16K×9位,讀寫周期為10 ns,支持異步和同步讀寫操作,寫數(shù)據(jù)和讀數(shù)據(jù)分別具有時(shí)鐘和使能信號(hào),具有“空、滿、可編程幾乎空、可編程幾乎滿”四個(gè)狀態(tài)標(biāo)志位,沒有絕對(duì)地址的概念,只有讀指針和寫指針的相對(duì)位置,只要標(biāo)志不為0,就可以進(jìn)行寫操作,只要標(biāo)志不為0,就可以進(jìn)行讀操作,讀寫操作可以同時(shí)進(jìn)行。

3 數(shù)據(jù)采集卡電路設(shè)計(jì)

3.1 信號(hào)調(diào)理電路

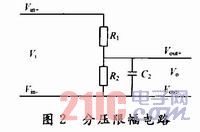

被測信號(hào)在進(jìn)入A/D轉(zhuǎn)換器之前,都必須進(jìn)行適當(dāng)?shù)奶幚恚怪螦/D轉(zhuǎn)換器的量程要求。對(duì)大信號(hào)需經(jīng)過適當(dāng)?shù)乃p,而小信號(hào)則需要放大。本數(shù)據(jù)采集卡采用的A/D轉(zhuǎn)換器的輸入電壓峰峰值在0~1 V之間,而被測信號(hào)幅度都大于此值,所以信號(hào)在進(jìn)入A/D轉(zhuǎn)換器之前需對(duì)其進(jìn)行衰減處理。具體的分壓限幅電路如圖2所示。

3.2 A/D轉(zhuǎn)換與FIFO緩存電路

由于AD9283數(shù)據(jù)最大采集頻率為100 MHz,所以其最大數(shù)據(jù)存儲(chǔ)頻率至少應(yīng)為100 MHz,而CY7C4261的最大存儲(chǔ)速率為100 MHz,能實(shí)現(xiàn)系統(tǒng)要求,系統(tǒng)中CY7C4261的寫時(shí)鐘與A/D轉(zhuǎn)換采用同一個(gè)時(shí)鐘進(jìn)行控制。在測試過程中,有些待測信號(hào)周期較大,而本數(shù)據(jù)采集板的采樣頻率為100 MHz,為了在數(shù)據(jù)采集過程中不丟數(shù)據(jù),需要連續(xù)采集大量數(shù)據(jù)。一片CY7C4261的存儲(chǔ)容量不夠,需要兩片輪流存儲(chǔ)。AD9283與CY7C4261的接口電路連接如圖3所示。

![]()

4 CPLD在數(shù)據(jù)采集卡中的應(yīng)用

CPLD作為整個(gè)數(shù)據(jù)采集過程的控制核心,負(fù)責(zé)地址譯碼、多路開關(guān)選通、A/D轉(zhuǎn)換啟動(dòng)、將轉(zhuǎn)換結(jié)果寫入FIFO以及兩片F(xiàn)IFO之間的切換等一系列操作。它的三個(gè)功能模塊分別為:地址譯碼模塊、多路開關(guān)控制模塊、A/D采樣及FIFO控制模塊。

4.1 地址譯碼模塊

該模塊實(shí)現(xiàn)了CPLD內(nèi)部與PC/104總線的接口單元。本數(shù)據(jù)采集卡是作為PC/104的標(biāo)準(zhǔn)外設(shè)進(jìn)行工作的。PC/104規(guī)定,外設(shè)的操作地址為A[9:0],在系統(tǒng)軟件設(shè)計(jì)中要防止地址沖突。PC/104中使用A0~A9地址位來表示I/O端口地址,即可有1 024個(gè)口地址,前512個(gè)供系統(tǒng)板使用,后512個(gè)供擴(kuò)充插槽使用,當(dāng)A9=O時(shí)表示系統(tǒng)板上的口地址;當(dāng)A9=1時(shí)表示擴(kuò)充插槽接口卡上的口地址。因此本數(shù)據(jù)采集板的基地址由A[9:4]來確定,偏移地址由地址線的A[3:O]確定,選擇該地址就意味著相應(yīng)的操作,CPLD對(duì)地址進(jìn)行譯碼后就產(chǎn)生相應(yīng)的控制。在Qu-artusⅡ上設(shè)計(jì)的地址譯碼模塊原理圖程序如圖4所示。

地址譯碼的工作過程為:在撥碼開關(guān)上手工設(shè)基地址,在CPLD內(nèi)部劃出一片74LS688地址比較器,比較CPU發(fā)出的基地址與手工設(shè)定的基地址是否一致,若不一致,則地址譯碼電路不工作,進(jìn)而整個(gè)數(shù)據(jù)采集板都不工作;若一致,則74LS688輸出低電平,使得偏移地址譯碼電路中的4-16譯碼器74LS154正常工作,在IOR,IOW信號(hào)的作用下產(chǎn)生各種控制信號(hào),使數(shù)據(jù)采集板正常工作。

4.2 多路開關(guān)控制模塊

該模塊實(shí)現(xiàn)了對(duì)八選一多路選擇開關(guān)ADG508A的選通控制。通過控制使能引腳EN以及CH0~CH2引腳,可對(duì)多路開關(guān)的輸入通道進(jìn)行可編程選擇。PC/104CPU通過地址譯碼選中CSWE[2],并寫入數(shù)據(jù)D0~D7,就可以選擇不同的通道導(dǎo)通。在QuartusⅡ上設(shè)計(jì)的多路開關(guān)控制模塊原理圖程序如圖5所示。

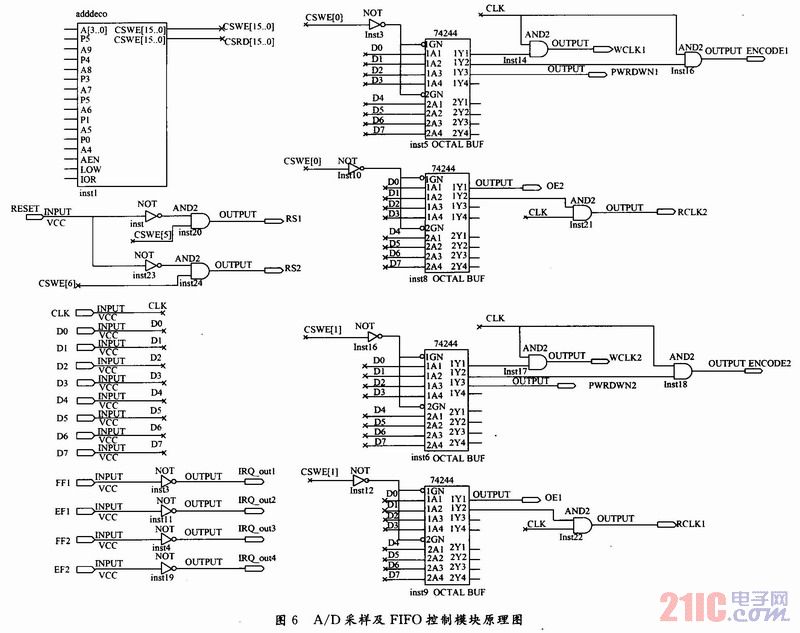

4.3 A/D采樣及FIFO控制模塊

該模塊主要負(fù)責(zé)A/D芯片的轉(zhuǎn)換時(shí)序,實(shí)現(xiàn)對(duì)A/D采樣的合理控制,同時(shí)將轉(zhuǎn)換數(shù)據(jù)存入FIFO中,并且控制著兩片F(xiàn)IFO的輪流存儲(chǔ),實(shí)現(xiàn)大量數(shù)據(jù)的采集。PC/104CPU通過地址譯碼選中CSWE[O],寫入數(shù)據(jù)D0~D7,將與門inst15打開,輸出端ENCODE1輸出100 MHz的時(shí)鐘信號(hào),PWRDWN1端輸出為低電平,啟動(dòng)A/D轉(zhuǎn)換,同時(shí),與門inst14被打開,WCLK1端輸出100 MHz時(shí)鐘,將轉(zhuǎn)換后的數(shù)據(jù)存入FIFO(1)中。選中CSRD[0],寫人數(shù)據(jù)D0~D7,將與門inst21打開,OE2端輸出低電平,使CY7C4261(2)輸出使能,RCLK2端輸出100 MHz的時(shí)鐘信號(hào),將數(shù)據(jù)讀出。當(dāng)FIFO(1)存儲(chǔ)滿時(shí),CPLD控制由FIFO(2)來進(jìn)行存儲(chǔ),同時(shí)將FIFO(1)中的數(shù)據(jù)讀出;當(dāng)FIFO(2)存儲(chǔ)滿時(shí),轉(zhuǎn)由FIFO(1)進(jìn)行存儲(chǔ),同時(shí)將FIFO(2)中數(shù)據(jù)讀出。如此反復(fù),直至預(yù)定的延時(shí)時(shí)間止,實(shí)現(xiàn)了兩片F(xiàn)IFO的輪流存儲(chǔ)和讀取,進(jìn)而達(dá)到了采集大量數(shù)據(jù)的目的。另外,在每次采樣及向FIFO中存儲(chǔ)數(shù)據(jù)之前,都要求選通CSWE[5]或CSWE[6]將FIFO芯片復(fù)位,使其讀指針和寫指針都指向第一個(gè)物理存儲(chǔ)地址。在QuartusⅡ上設(shè)計(jì)的A/D采樣及FIFO控制模塊原理圖程序如圖6所示。

CPLD硬件控制邏輯設(shè)計(jì)的關(guān)鍵是分析各個(gè)器件的工作時(shí)序和采樣保持時(shí)間,A/D轉(zhuǎn)換時(shí)間以及數(shù)據(jù)存入FIFO的時(shí)間等。在設(shè)計(jì)的時(shí)序處理進(jìn)程中,要根據(jù)CPLD的工作頻率計(jì)算各個(gè)等待周期,等器件準(zhǔn)備好以后才能進(jìn)行下一個(gè)處理。

5 結(jié)語

采用CPLD和FIFO器件設(shè)計(jì)了一種基于PC/104總線的高速數(shù)據(jù)采集卡,它可以作為PC/104總線標(biāo)準(zhǔn)模件使用。該采集板上的大部分控制邏輯被集成到CPLD芯片中,大大減少了擴(kuò)展卡上的器件數(shù)量,同時(shí)降低了系統(tǒng)成本,提高了系統(tǒng)的可靠性。該數(shù)據(jù)采集板非常適合搭建高密度、小體積的便攜式測試設(shè)備,可廣泛應(yīng)用于武器控制系統(tǒng)的測試等多種場合,對(duì)控制系統(tǒng)的模擬量信號(hào)進(jìn)行快速、實(shí)時(shí)的數(shù)據(jù)采集和分析。