電路功能與優(yōu)勢

本電路利用ADF4002頻率合成器產(chǎn)生極低抖動編碼(采樣)時鐘,以控制模數(shù)轉(zhuǎn)換器AD9215的采樣。編碼時鐘上的抖動會降低總信噪比(SNR),二者的關(guān)系如下式所示:

其中f為滿量程模擬輸入頻率,tj為均方根抖動。公式1中的“SNR”是僅由時鐘抖動決定的SNR,與ADC的分辨率無關(guān)。

電路描述

ADF4002由低噪聲數(shù)字鑒頻鑒相器(PFD)、精密電荷泵、可編程參考分頻器和可編程N分頻器組成。14位參考計數(shù)器(R計數(shù)器)允許PFD輸入端的REFIN頻率為可選值。如果頻率合成器與一個外部環(huán)路濾波器和電壓控制振蕩器(VCO)一起使用,則可以實現(xiàn)完整的鎖相環(huán)(PLL)。

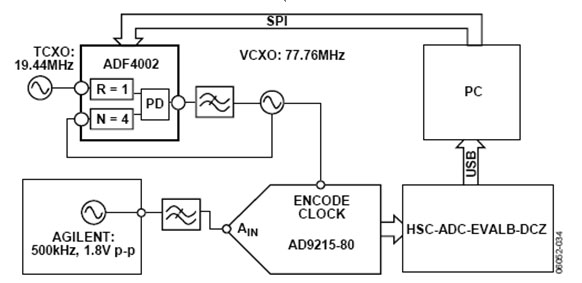

圖1顯示ADF4002與VCXO共同為高速模數(shù)轉(zhuǎn)換器提供編碼時鐘。本應(yīng)用中的轉(zhuǎn)換器為一款10位轉(zhuǎn)換器AD9215-80,它可接受最高80 MHz的編碼時鐘。為實現(xiàn)穩(wěn)定的低抖動時鐘,采用77.76 MHz窄帶VCXO。本例假設(shè)參考時鐘為19.44 MHz,為了將ADF4002的相位噪聲貢獻(xiàn)降至最低,采用最小的倍增系數(shù)4。因此,R分頻器編程設(shè)置為1,N分頻器編程設(shè)置為4。ADF4002的電荷泵輸出(引腳2)驅(qū)動環(huán)路濾波器,環(huán)路濾波器的帶寬經(jīng)過優(yōu)化,以提供最佳的均方根抖動,它是決定ADC信噪比的關(guān)鍵因素。如果帶寬過窄,在相對于載波頻率的頻偏較小處,VCXO噪聲占主導(dǎo)地位。如果帶寬過寬,ADF4002噪聲將在VCXO噪聲低于ADF4002噪聲情況下的頻偏處占主導(dǎo)地位。因此,環(huán)路濾波器的最佳帶寬對應(yīng)VCXO噪聲與ADF4002帶內(nèi)噪聲的交點。

圖1. ADF4002用作高速ADC的編碼(采樣)時鐘

可以使用ADIsimPLL™設(shè)計工具(3.0版)來設(shè)計環(huán)路濾波器,該工具可從analog.com/pll免費下載。測量所得的均方根抖動小于1.2 ps,假設(shè)輸入信號為20 MHz,利用上述公式1可得出SNR理論值(僅由抖動決定)為76.4 dB。該值比ADC的額定SNR (59 dB)高出17.4 dB,導(dǎo)致總SNR僅降低0.1 dB。如果均方根抖動提高至6 ps,則20 MHz時由抖動決定的相應(yīng)SNR為62.4 dB,導(dǎo)致總SNR為57.4 dB。

為進(jìn)行精確測量,需要低噪聲、低失真模擬輸入源。利用優(yōu)質(zhì)信號發(fā)生器及后置調(diào)諧至目標(biāo)頻率的帶通濾波器即可實現(xiàn)。雖然圖1所示采用500 kHz信號源,但是應(yīng)能夠測試更高頻率的信號源。每種附加頻率均需要一個獨立的帶通濾波器。

圖1所示設(shè)置使用ADF4002、AD9215和HSC-ADC-EVALB-DCZ,用戶可以快速有效地確定轉(zhuǎn)換器和編碼時鐘是否合適。SPI接口用來控制ADF4002,USB接口幫助控制AD9215-80的操作。控制器板將FFT信息送回PC,如果PC使用ADI公司的ADC Analyzer™軟件,則會提供來自ADC的所有轉(zhuǎn)換結(jié)果。為了達(dá)到所需的性能,整個系統(tǒng)必須使用出色的布局、接地和去耦技術(shù)。

常見變化

基于PLL的時鐘產(chǎn)生電路,如圖1所示,經(jīng)常用于從高噪聲系統(tǒng)時鐘產(chǎn)生干凈的低抖動時鐘。ADI公司提供許多不同的頻率合成和時鐘產(chǎn)生產(chǎn)品,均適合類似的應(yīng)用。欲了解更多信息,請參考analog.com/clock-timing。

進(jìn)一步閱讀

ADIsimPLL Phase-Locked Loop Circuit Design Software.

HSC-ADC-EVALB-DCZ High Speed ADC Data Capture Kit.

Kester, Walt. 2005. The Data Conversion Handbook. Analog Devices. Chapters 6 and 7.

Kester, Walt. 2006. High Speed System Applications. Analog Devices. Chapter 2, “Optimizing Data Converter Interfaces,”

Kester, Walt. 2006. High Speed System Applications. Analog Devices. Chapter 3, “DACs, DDSs, PLLs, and Clock Distribution.”

MT-101 Tutorial, Decoupling Techniques. Analog Devices.

MT-031 Tutorial, Grounding Data Converters and Solving the Mystery of AGND and DGND. Analog Devices.

數(shù)據(jù)手冊和評估板

AD9215 Data Sheet.

ADF4002 Data Sheet.

HSC-ADC-EVALB-DCZ Evaluation Board.

修訂歷史

5/09—Rev. 0 to Rev. A

Updated Format ................................................................ Universal

10/08—Revision 0: Initial Version