電路功能與優(yōu)勢

本文所述電路如圖1所示,可提供一種消除不確定失調(diào)誤差的校準(zhǔn)方法。在工業(yè)過程控制和儀器儀表應(yīng)用中使用高精度、高分辨率DAC時,低失調(diào)通常是一個關(guān)鍵特性。該電路利用 AD5360的內(nèi)置特性,并配合外部比較器和運算放大器,確定DAC輸出電壓是高于還是低于接地參考信號。當(dāng)失調(diào)量已知時,用戶可以調(diào)整發(fā)送至DAC的代碼來消除失調(diào)。

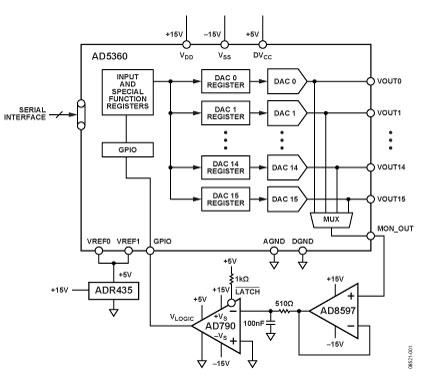

圖1. AD5360 DAC的自校準(zhǔn)電路可將失調(diào)電壓降至1 mV以下(原理示意圖,未顯示去耦和所有連接)

電路描述

AD5360是一款16通道、16位數(shù)模轉(zhuǎn)換器。采用5 V基準(zhǔn)電壓源時,標(biāo)稱輸出范圍為±10 V。AD5360內(nèi)置兩個偏移DAC。各偏移DAC均與一組(8個)DAC相連,用來調(diào)整輸出范圍的中間電平點。例如,可通過設(shè)置偏移DAC將輸出范圍從±10 V變?yōu)?minus;8 V至+12 V,或應(yīng)用要求的其它值。

AD5360經(jīng)過工廠調(diào)整,具有極低失調(diào)。執(zhí)行工廠調(diào)整時,偏移DAC的值為默認(rèn)值,而且已經(jīng)有效消除其所引起的失調(diào)誤差。但是,當(dāng)偏移DAC的值變?yōu)榉悄J(rèn)值時,其失調(diào)誤差會影響主DAC的失調(diào)誤差。

本文所述電路可以測量并通過校準(zhǔn)消除這些情況下主DAC的失調(diào)誤差。該電路需用一個通用I/O引腳和一個片內(nèi)監(jiān)控多路復(fù)用器。GPIO(通用I/O)引腳設(shè)置為輸入;通過讀取GPIO內(nèi)部寄存器,可以確定GPIO引腳的邏輯狀態(tài)。模擬多路復(fù)用器是可編程的,可將16路DAC輸出中的任一輸出與單一引腳(MON_OUT)相連。多路復(fù)用器具有低而有限的導(dǎo)通電阻RON ,因此從MON_OUT汲取的任何電流均會在RON 上產(chǎn)生壓降,從而引起輸出誤差。為了避免這種現(xiàn)象,需用一個低噪聲放大器AD8597來緩沖MON_OUT。該放大器后接低通濾波器,可降低高速精密比較器AD790 所接受的噪聲量,以免發(fā)生誤觸發(fā)。

AD790可以采用±15 V電源供電,從而與AD5360兼容。采用±15 V電源供電時,AD790還需要一個額外的+5 VVLOGIC電源。此外,AD790的最大差分輸入電壓為15 V;因此,它能夠耐受AD5360的輸出電壓,而無需衰減。圖1中,如果通道失調(diào)為正,則比較器輸出為低電平,表示必須降低輸出電壓以消除失調(diào)。

如果通道失調(diào)為負,則比較器輸出為高電平,表示必須提高輸出電壓以消除失調(diào)。為校準(zhǔn)DAC,DAC通道需載入數(shù)字值,該值應(yīng)恰好提供與SIGGND相等的電壓(即0 V)。本例中,假設(shè)DAC通道具有負失調(diào)。讀取GPIO寄存器顯示,比較器輸出為低電平,表示輸入必須遞增,直到輸出反轉(zhuǎn)為止。隨著寫入DAC輸入寄存器的代碼逐步增大,讀取GPIO寄存器,直到比較器輸出跳變?yōu)楦唠娖健D790的最大遲滯帶為0.65 mV;因此,再次減小DAC碼可以更精確地確定DAC失調(diào)。

當(dāng)比較器輸出重新跳變?yōu)榈碗娖綍r,SIGGND位于這兩個碼之間的某個位置。由于電路所用器件存在誤差,比較器跳變點之間通常有三四個碼的跨度。用這種方法無法準(zhǔn)確確定哪個碼可提供最低失調(diào)輸出,但是,如果選取的碼為兩個跳變點碼的平均值,則相對于SIGGND的DAC通道失調(diào)一般小于1 mV。

為了使本文所討論的電路達到理想的性能,必須采用出色的布局、接地和去耦技術(shù)(請參考教程MT-031和教程MT-101)。至少應(yīng)采用四層PCB:一層為接地層,一層為電源層,另兩層為信號層。

常見變化

AD5362是AD5360的8通道版本。AD5361和AD5363分別是AD5360和AD5362的14位版本。AD8599是AD8597的雙通道版本。

本文所述電路可以使用上述任一款A(yù)D536x器件。需要時,也可以改用其它基準(zhǔn)電壓源以提供不同的輸出范圍。

adi">>>>>進入ADI資源中心,下載電子版以及更多資料<<<