將具有信號處理功能的FPGA與現(xiàn)實(shí)世界相連接,需要使用模數(shù)轉(zhuǎn)換器(ADC)或數(shù)模轉(zhuǎn)換器(DAC)

一旦執(zhí)行特定任務(wù),F(xiàn)PGA系統(tǒng)必須與現(xiàn)實(shí)世界相連接,而所有工程師都知道現(xiàn)實(shí)世界是以模擬信號而非數(shù)字信號運(yùn)轉(zhuǎn)的。這意味著需要在模擬信號域與數(shù)字信號域之間進(jìn)行轉(zhuǎn)換。針對手頭工作選擇恰當(dāng)?shù)腇PGA時,用戶面臨著林林總總的選擇,在為系統(tǒng)選擇正確的ADC或DAC時也是如此,玲瑯滿目。

選擇時首先要確定轉(zhuǎn)換信號所需的采樣頻率。這個參數(shù)不僅將影響轉(zhuǎn)換器的選擇,同時也會影響對FPGA的選擇,這樣才能確保器件能夠滿足所需的處理速度及邏輯封裝要求。轉(zhuǎn)換器的采樣頻率至少為信號采樣頻率的2倍。因此,如果信號的采樣頻率為50MHz,則轉(zhuǎn)換器采樣頻率至少應(yīng)為100MHz。否則,已轉(zhuǎn)換的信號將引起自身混疊,導(dǎo)致信號無法正確表示。但混疊并不總是一件壞事情;事實(shí)上,如果轉(zhuǎn)換器的帶寬足夠高,那么用戶可以利用混疊將信號混疊至可用的帶寬。

ADC與DAC的關(guān)鍵參數(shù)

我們可采用多種不同方法來構(gòu)建模數(shù)轉(zhuǎn)換器(ADC)。最常見的方法包括閃存、斜坡(Ramp)以及逐次逼近等。

1,閃存轉(zhuǎn)換器以速度快著稱,其使用一系列可擴(kuò)展的模擬比較器對輸入電壓和參考電壓進(jìn)行比較;ADC利用這些比較器的輸出來確定數(shù)字代碼。

2,斜坡轉(zhuǎn)換器可利用連接至DAC且可自由運(yùn)行的計數(shù)器,對DAC輸出/輸入電壓進(jìn)行比較。當(dāng)二者相等時,保持計數(shù)不變。

3,逐次逼近轉(zhuǎn)換器(SAR)是斜坡轉(zhuǎn)換器的另一種形式,其可利用DAC和比較器來處理模擬輸入信號。但SAR轉(zhuǎn)換器并非執(zhí)行累計計數(shù),而是通過判斷計數(shù)的模擬表示是否高于或低于輸入信號,并采用試錯法(trial-and-error)來確定數(shù)字代碼。

此外,數(shù)模轉(zhuǎn)換器(DAC)也可以采用若干種方法來實(shí)現(xiàn),最常見的方法包括二進(jìn)制加權(quán)、R-2R梯形網(wǎng)絡(luò)、脈寬調(diào)制。

4,二進(jìn)制加權(quán)是速度最快的DAC架構(gòu)之一。這些器件可將各邏輯比特的不同轉(zhuǎn)換結(jié)果進(jìn)行匯總。例如,電阻DAC將根據(jù)電流代碼來導(dǎo)通或切斷這些電阻。

5,R-2R梯形轉(zhuǎn)換器采用阻值為R-2R的級聯(lián)電阻結(jié)構(gòu)。由于可以輕松生成并匹配高精度電阻,因而這類DAC的精度比二進(jìn)制加權(quán)轉(zhuǎn)換器更高。

6,脈寬調(diào)制(PWM)是最簡單的DAC結(jié)構(gòu)類型,可通過簡單的低通模擬濾波器傳遞脈寬調(diào)制波形。這些器件通常應(yīng)用于電機(jī)控制領(lǐng)域,但它們也可作為Σ-Δ轉(zhuǎn)換器的基礎(chǔ)。

眾多專家級器件(specialist device)的制造商已成功開發(fā)其自有的內(nèi)部轉(zhuǎn)換架構(gòu),可根據(jù)用途盡可能提供適用于特定領(lǐng)域的最佳性能。每種器件在轉(zhuǎn)換速度、精度以及分辨率方面都各具優(yōu)劣勢。在選擇FPGA時,您需要考慮I/O數(shù)量、所支持的I/O標(biāo)準(zhǔn)、時鐘管理、邏輯資源和存儲器,以及其它與器件類型相關(guān)的具體參數(shù):最高采樣頻率、信噪比(SNR)、無雜散動態(tài)范圍(SFDR)以及有效位數(shù)(ENOB)等。

采樣頻率非常簡單,是ADC能夠數(shù)字化輸入信號的最高速率。SNR表示信號與噪聲電平的比值,與輸入信號無關(guān)。用戶可以利用以下公式來確定SNR的理論值:

其中N表示分辨率。該方程適用于滿量程正弦波。

在系統(tǒng)測試過程中,用戶可首先對輸出執(zhí)行快速傅里葉變換(FFT),然后測量輸入信號與本底噪聲的比值,這樣即可確定實(shí)際的SNR值。

與此同時,SFDR表示輸入信號與下一個最高峰值(通常為基諧波)的比值。通常SFDR用dBc來表示,會隨著輸入信號功率的降低而相應(yīng)減小。

從轉(zhuǎn)換器的測量結(jié)果可以看出,用戶可利用下列式子來計算有效位數(shù):

當(dāng)進(jìn)行這項(xiàng)測試時,應(yīng)注意選擇合適的FFT點(diǎn)數(shù),從而確保不會由于一時疏忽而錯誤計算本底噪聲。FFT點(diǎn)數(shù)不恰當(dāng)將導(dǎo)致錯誤的計算結(jié)果。FFT本底噪聲可通過下列式子計算得出:

用戶應(yīng)通過單音測試(通常為簡單的正弦波)執(zhí)行這些步驟,可降低輸出頻譜的復(fù)雜性。為了確保獲取最佳結(jié)果,需要確保對輸出信號執(zhí)行相干采樣。如果在數(shù)據(jù)窗口中包括幾個周期,則執(zhí)行相干采樣。公式如下:

頻譜

另一方面,用戶在實(shí)現(xiàn)系統(tǒng)時還必須了解奈奎斯特準(zhǔn)則,以確保正確地轉(zhuǎn)換或量化信號。這意味著用戶對所關(guān)注信號執(zhí)行采樣時,采樣頻率至少為該信號最高頻率的2倍,才能確保正確進(jìn)行轉(zhuǎn)換。如果未按此標(biāo)準(zhǔn)執(zhí)行采樣,則將發(fā)生混疊;而如果沒有正確理解混疊,則可能導(dǎo)致性能欠佳。

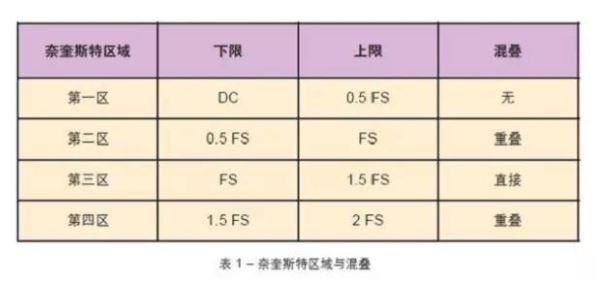

此外,因?yàn)檫@個原因,ADC需要利用抗混疊濾波器來阻止信號或噪聲混疊至量化的信號中。但是,頻譜混疊對于工程師來說非常有用,在ADC具有寬泛輸入帶寬的情況下尤為如此。經(jīng)過周密安排考慮之后,混疊使用戶無需借助下變頻器即可直接轉(zhuǎn)換信號。出于這種考慮,我們將頻譜劃分為幾個區(qū)域。

利用表1中給出的信息,如果轉(zhuǎn)換器擁有足夠高的帶寬,則可將信號從一個奈奎斯特頻帶混疊至另一個頻帶。

通信選擇

正如所有的外部器件一樣,ADC與DAC也配套提供了數(shù)個并行或串行接口選項(xiàng)。通常情況下,較高速器件用并行接口,較低速器件用串行接口。但是,可以根據(jù)您的應(yīng)用選擇采用特殊的接口方式。例如,采用串行接口比采用并行接口可以更輕松地檢測出固定比特(stuck-atbit)。實(shí)際上,高速接口可提供多條輸出總線(I和Q)或采用雙數(shù)據(jù)速率(DDR)輸出模式;有些器件甚至可能同時提供這兩個選項(xiàng)。提供多條總線或采用DDR輸出模式使用戶能夠保持?jǐn)?shù)據(jù)速率,同時降低接口所需的運(yùn)行頻率。例如,如果接口的采樣頻率為600MHz,則其輸出頻率為300MHz(為采樣頻率的一半)。

如果時鐘頻率為75MHz(1/4采樣頻率)并且有兩條可通過DDR對器件進(jìn)行采樣的數(shù)據(jù)總線,則可非常輕松地執(zhí)行恢復(fù)操作。這類ADC對輸入時序要求較為寬松。眾多高速轉(zhuǎn)換器均可利用其I/O中的LVDS信號,因?yàn)檩^低的電壓擺幅和低電流可降低由其它信號標(biāo)準(zhǔn)所引發(fā)的耦合性,如LVCMOS等。這種耦合問題會影響轉(zhuǎn)換器的混合信號性能。

DAC濾波

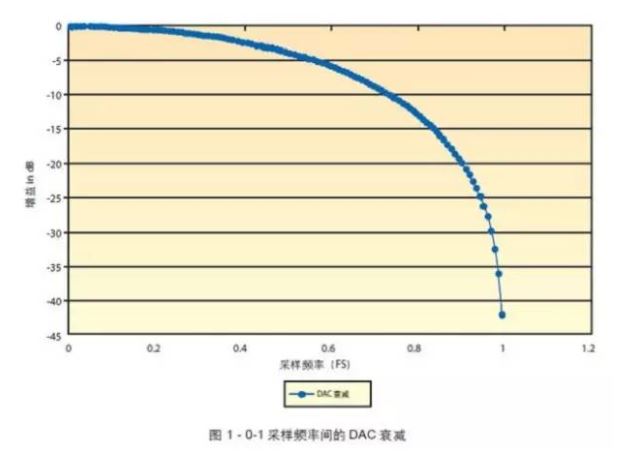

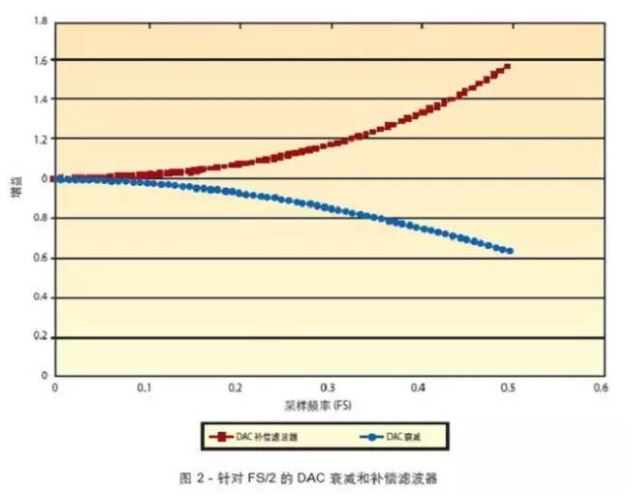

大多數(shù)DAC一直將模擬輸出保持到下一個采樣周期,這將對輸出頻率域產(chǎn)生良好的效果。用戶將注意到這兩個圖像均存在于整個輸出頻譜中,由于在0.5FS時正弦效應(yīng)將接近4dB(3.92dB),所有奈奎斯特區(qū)域中的輸出信號都出現(xiàn)衰減(如圖1所示)。這兩大問題均可利用濾波器來解決。

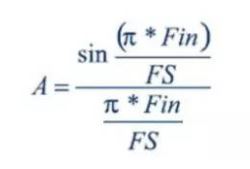

用戶可以像實(shí)現(xiàn)FIR濾波器一樣輕松實(shí)現(xiàn)正弦校正濾波器。開發(fā)該濾波器最簡單的方法就是利用下列方程式來繪制正弦衰減特性。

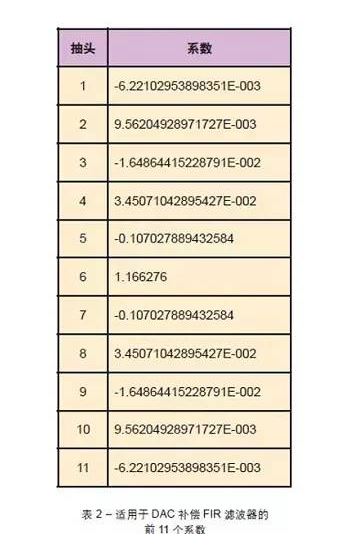

先創(chuàng)建校正因子,該因子是所計算出衰減系數(shù)的倒數(shù),然后再執(zhí)行逆傅里葉變換,以獲取所需要設(shè)計濾波器的系數(shù)。通常情況下,用戶需要采用幾個抽頭才能實(shí)現(xiàn)該濾波器。表2給出了濾波器的前11個系數(shù),同時圖2還給出了針對衰減的補(bǔ)償。

在系統(tǒng)測試

眾多這類系統(tǒng)都將利用轉(zhuǎn)換器實(shí)現(xiàn)終端應(yīng)用的具體性能特征,如CDMA或GSM等。為實(shí)現(xiàn)該項(xiàng)性能而進(jìn)行的測試需要在測試系統(tǒng)(任意波形生成器、邏輯分析儀、模式生成器、頻譜分析儀等)方面進(jìn)行大量的投入。但是,F(xiàn)PGA高度的可重編程靈活性使用戶能將特定的測試程序插入至器件中,這樣既可以捕獲并分析ADC的輸出也可以提供DAC激勵,從而減少對更多額外測試設(shè)備的需要。

轉(zhuǎn)換101

由于FPGA通常需要與ADC和DAC接口相連,因而對于任何FPGA工程師來說,基本了解這些器件參數(shù)的重要性非常關(guān)鍵。如果用戶計劃在設(shè)計驗(yàn)證與調(diào)試過程中利用FPGA的可重編程靈活性來測試轉(zhuǎn)換器的性能,這一點(diǎn)尤其有用。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<