自動(dòng)收發(fā)轉(zhuǎn)換的RS-485接口電路及測(cè)試電路

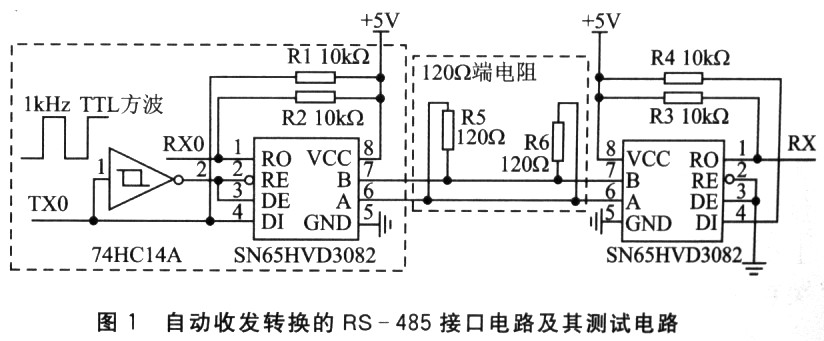

摘要: 圖l所示的虛線框中為接口電路,通過(guò)對(duì)真值表進(jìn)行分析,其發(fā)送和接收過(guò)程為:當(dāng)發(fā)送端DI=O時(shí),DE/RE=1發(fā)送O電平,接收端RO=O;當(dāng)發(fā)送端DI=1時(shí),DE/RE=0,VA=VB=2.5V,接收端由于上拉電阻的作用RO=1。

Abstract:

Key words :

圖l所示的虛線框中為接口電路,通過(guò)對(duì)真值表進(jìn)行分析,其發(fā)送和接收過(guò)程為:

當(dāng)發(fā)送端DI=O時(shí),DE/RE=1發(fā)送O電平,接收端RO=O;當(dāng)發(fā)送端DI=1時(shí),DE/RE=0,VA=VB=2.5V,接收端由于上拉電阻的作用RO=1。

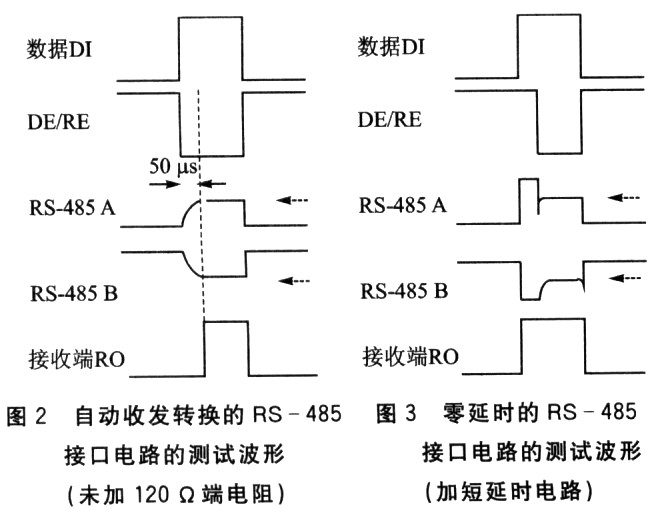

在此接口電路的TXo端加入1kHz的TTL方波對(duì)電路進(jìn)行測(cè)試。未加入120Ω端電阻時(shí),接口芯片的485-A和485-B腳都有約50μs的電壓變化過(guò)程,如圖2所示。接收端Ro波形的上升沿有明顯的延遲約30~40μs(和數(shù)據(jù)發(fā)送端DI比較),造成很大的傳輸誤差;加入120Ω端電阻時(shí),延遲明顯縮小,約3μs。

此電路在發(fā)送高電平時(shí),發(fā)送器處于高阻狀態(tài),總線上所有接口處于接收狀態(tài),總線是空閑的,允許其他接口發(fā)送數(shù)據(jù),因此容易引入總線沖突。特別是連續(xù)發(fā)送商電平比特時(shí),發(fā)送器處于高阻狀態(tài)的時(shí)間越長(zhǎng),引入總線沖突的幾率就越大。

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。