摘要:多通道頻率檢測(cè)是當(dāng)前數(shù)字接收機(jī)的一種常用的頻率測(cè)量方案,該方法可以較好地解決頻率截獲概率與頻率分辨力的矛盾,并在復(fù)雜的電磁環(huán)境中具有處理多個(gè)同時(shí)到達(dá)信號(hào)的能力。文中給出了基于FPGA來(lái)實(shí)現(xiàn)多信道頻率測(cè)量的具體方案。該方案能夠充分發(fā)揮FPGA硬件資源豐富的特點(diǎn),并且易于實(shí)現(xiàn)并行處理,可大幅度提高系統(tǒng)的處理速度。

關(guān)鍵詞:多通道;頻率檢測(cè);信道化;FPGA

0 引言

在數(shù)字接收機(jī)的各種參數(shù)中,頻率是最重要的參數(shù)之一,它能反映接收機(jī)的功能和用途、以及頻譜寬度等重要指標(biāo)。傳統(tǒng)的順序測(cè)頻技術(shù)一般通過(guò)對(duì)接收機(jī)頻帶的掃描,對(duì)頻域進(jìn)行連續(xù)取樣。該方法原理簡(jiǎn)單,技術(shù)成熟,但是,其頻率截獲概率與分辨力的矛盾難以解決,無(wú)法實(shí)現(xiàn)全概率信號(hào)截獲。而多信道化的頻率檢測(cè)技術(shù)屬于瞬時(shí)測(cè)頻,其架構(gòu)是采用多個(gè)頻率窗口(多個(gè)信道彼此銜接相鄰)來(lái)覆蓋接收機(jī)的整個(gè)頻段,這樣,當(dāng)信號(hào)進(jìn)入任一個(gè)窗口時(shí),該窗口的頻率值即可被檢測(cè)出。因此,該方法可解決頻率截獲概率與頻率分辨力的矛盾,同時(shí)也為實(shí)現(xiàn)全概率頻率捕獲提供了一種參考方案。

1 多信道模型

當(dāng)一個(gè)實(shí)信號(hào)經(jīng)過(guò)A/D采樣之后,再進(jìn)行正交下變頻處理,即可得到I、Q兩路相位正交信號(hào),它們所構(gòu)成的是一個(gè)復(fù)信號(hào)。該復(fù)信號(hào)的信道化示意圖如圖1所示。

圖1所示的信道是一種相互交疊的信道,它們涵蓋了整個(gè)零中頻信號(hào)的頻率范圍。一般情況下,多信道往往采用數(shù)字濾波器組來(lái)實(shí)現(xiàn),但該方法需要設(shè)計(jì)M(M為信道數(shù))個(gè)中心頻率不同,而其它性質(zhì)完全相同的帶通濾波器。這種結(jié)構(gòu)設(shè)計(jì)過(guò)于復(fù)雜,同時(shí)還加大了后續(xù)信號(hào)處理的運(yùn)算速度,對(duì)實(shí)時(shí)處理極為不利。而數(shù)字濾波器組的低通型實(shí)現(xiàn)方法則是先將每個(gè)通道乘以一變換因子,就相當(dāng)于將實(shí)際信號(hào)搬移到零中頻,然后再通過(guò)LPF得到該頻率信號(hào)。該方法可對(duì)帶通信號(hào)的頻段進(jìn)行信道化分離,但是帶來(lái)的新問(wèn)題是當(dāng)LPF用FIR濾波器實(shí)現(xiàn)M個(gè)濾波運(yùn)算時(shí),將占用較大的硬件資源,而且系統(tǒng)工作效率較低。目前,該結(jié)構(gòu)已被高效DFT多相濾波器組結(jié)構(gòu)所代替。

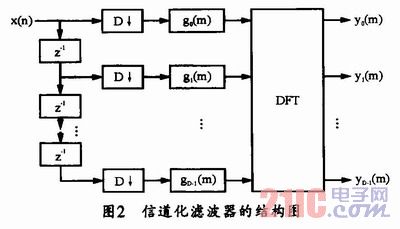

圖2所示是一種具有普遍性的基于DFT多相濾波器組的信道化高效結(jié)構(gòu),從圖2中可以看出,在濾波之前,先對(duì)數(shù)據(jù)進(jìn)行D倍抽取可降低濾波過(guò)程的運(yùn)算量,gn(m)是低通原型濾波器hLP(n)的多相分量,其階數(shù)可減小到原來(lái)的1/D,因而DFT可以用FFT實(shí)現(xiàn)。事實(shí)上,在此結(jié)構(gòu)中,系統(tǒng)的復(fù)雜度和數(shù)據(jù)速率大大降低,實(shí)時(shí)處理能力得到了提高。

2 濾波器的設(shè)計(jì)及仿真

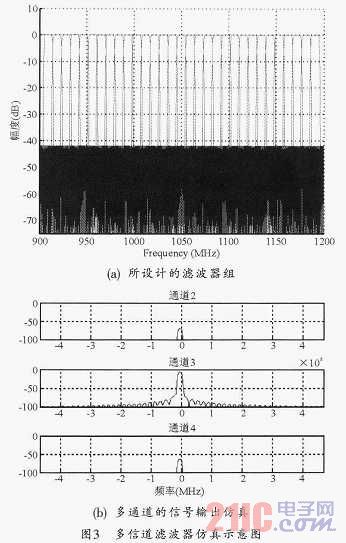

低通型濾波器結(jié)構(gòu)中的每個(gè)通道都是由原型低通濾波器乘以旋轉(zhuǎn)因子形成的。根據(jù)要求,圖3所示是由256階原型低通濾波器形成的濾波器組及其信號(hào)輸出仿真波形。該信號(hào)的有效帶寬為300MHz,共分為32通道,每通道帶寬為9.375MHz。如給此濾波器組送入頻率?=28.1MHz

的單頻信號(hào),那么,通過(guò)理論計(jì)算可知,信號(hào)應(yīng)在第3號(hào)通道有輸出。圖3 (b)所示就是第2、3、4通道的輸出仿真結(jié)果,可以看出,僅第3個(gè)通道有比較強(qiáng)的信號(hào)輸出,這與理論上的計(jì)算結(jié)果是一致的。

3 實(shí)現(xiàn)方案

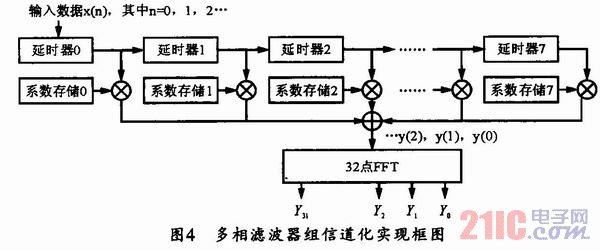

本設(shè)計(jì)選用的FPGA芯片是Xilinx公司的Virtex-4SX55,該芯片時(shí)鐘資源豐富,算術(shù)運(yùn)算單元和專用存儲(chǔ)模塊以及可配置邏輯的使用都很靈活,非常適合當(dāng)前信號(hào)處理系統(tǒng)的功能實(shí)現(xiàn)。因此,根據(jù)圖2所示的結(jié)構(gòu),就可以得到一種基于DFT多相濾波器組的信道化解決方案,其具體實(shí)現(xiàn)結(jié)構(gòu)如圖4所示。

圖4所示結(jié)構(gòu)由延時(shí)器、系數(shù)存儲(chǔ)器、乘加器和FFT組成。其中延遲器可實(shí)現(xiàn)對(duì)輸入數(shù)據(jù)32個(gè)周期的延時(shí),存儲(chǔ)器用于存儲(chǔ)濾波器系數(shù)。下面對(duì)該結(jié)構(gòu)中幾個(gè)主要組成模塊的實(shí)現(xiàn)及仿真結(jié)果進(jìn)行介紹。

3.1 延時(shí)器的實(shí)現(xiàn)

本延時(shí)器采用FPGA提供的專用存取模塊FIFO來(lái)實(shí)現(xiàn)32周期延時(shí),其架構(gòu)體系如圖5所示。圖中,每個(gè)延遲單元即是一個(gè)FIFO模塊,F(xiàn)IFO的數(shù)據(jù)輸出特點(diǎn)為先入先出。在本設(shè)計(jì)中,第一級(jí)延遲器的輸出數(shù)據(jù)將作為下一個(gè)延遲器的輸入數(shù)據(jù),就相當(dāng)于第一級(jí)FIFO的數(shù)據(jù)按先進(jìn)先出的順序依次向第二級(jí)FIFO壓入,相鄰兩級(jí)的將滿標(biāo)志與讀使能信號(hào)進(jìn)行握手協(xié)議,從而實(shí)現(xiàn)數(shù)據(jù)的延遲輸出。這樣,設(shè)計(jì)8個(gè)同樣結(jié)構(gòu)的FIFO并進(jìn)行串行級(jí)聯(lián),即可滿足該結(jié)構(gòu)的設(shè)計(jì)要求。

3.2 系數(shù)存儲(chǔ)模塊

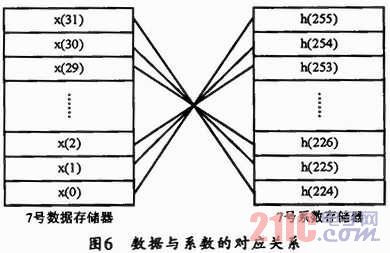

對(duì)于256階原型低通濾波器,可以將h(0),h(1),…,h(255)這256個(gè)系數(shù)分成八組,每組32個(gè),分別存儲(chǔ)到八個(gè)存儲(chǔ)器當(dāng)中,存儲(chǔ)器0存儲(chǔ)的系數(shù)為:h(0),h(1),…,h(31);存儲(chǔ)器1存儲(chǔ)的系數(shù)為:h(32),h(33),…,h(63);以此類推。存儲(chǔ)器可使用邏輯(LUT)實(shí)現(xiàn),也可使用專用存儲(chǔ)模塊Block RAM來(lái)實(shí)現(xiàn)。FIFO中的目標(biāo)數(shù)據(jù)和存儲(chǔ)器中系數(shù)做乘法運(yùn)算時(shí),兩者的對(duì)應(yīng)關(guān)系如圖6所示(以7號(hào)存儲(chǔ)器為例)。

當(dāng)8個(gè)數(shù)據(jù)存儲(chǔ)器的最后一個(gè)單元數(shù)據(jù)被讀出時(shí),8個(gè)系數(shù)存儲(chǔ)器的0號(hào)地址單元的系數(shù)也將同時(shí)被讀出,然后分別作乘累加,最后作為y(0)輸出。同理,當(dāng)8個(gè)數(shù)據(jù)存儲(chǔ)器的第二個(gè)數(shù)據(jù)被讀出時(shí),8個(gè)系數(shù)存儲(chǔ)器的1號(hào)地址單元的系數(shù)也同時(shí)被讀出,然后分別作乘累加,最后的結(jié)果作為y(1)輸出,以此類推,得出全部y(2)~y(31)的輸出。最后將y(0)~y(31)作為FFT的輸入數(shù)據(jù)進(jìn)行32點(diǎn)FFT運(yùn)算。

3.3 FFT的實(shí)現(xiàn)

設(shè)計(jì)中的FFT變換可通過(guò)調(diào)用Xilinx的IP核來(lái)實(shí)現(xiàn)。FFT采用流水型結(jié)構(gòu),該結(jié)構(gòu)能夠?qū)B續(xù)數(shù)據(jù)流進(jìn)行處理,只是結(jié)果上有若干周期的延遲。FFT核的輸入輸出的引腳關(guān)系如圖7所示。

3.4 仿真結(jié)果

FPGA的設(shè)計(jì)軟件可采用ALDEC公司的Active_HDL8.2,并可用Testbench文件對(duì)所設(shè)計(jì)模塊進(jìn)行仿真。Testbench文件讀取時(shí),可由Matlab

產(chǎn)生的信號(hào)數(shù)據(jù)作為FPGA仿真的激勵(lì)信號(hào),信號(hào)形式采用28.1MHz的單頻信號(hào):

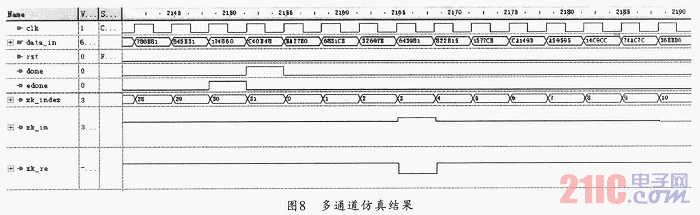

將信號(hào)數(shù)據(jù)送入圖4所構(gòu)建的系統(tǒng)后,即可在ALDEC下得到圖8所示的仿真波形。

由圖8可以看到,該仿真結(jié)果在第3號(hào)通道上有信號(hào)輸出,這與圖3中用Matlab仿真的結(jié)果一致,從而驗(yàn)證該模塊設(shè)計(jì)的正確性。

4 結(jié)束語(yǔ)

本文針對(duì)多信道頻率檢測(cè)技術(shù)進(jìn)行了研究,并在傳統(tǒng)檢測(cè)方法的基礎(chǔ)上,結(jié)合FPGA的特點(diǎn),構(gòu)建了一種基于DFT多相濾波器組信道化的高效結(jié)構(gòu)。該結(jié)構(gòu)可解決頻率截獲概率與頻率分辨力的矛盾,同時(shí)也為實(shí)現(xiàn)全概率頻率捕獲提供一種參考方案。經(jīng)過(guò)仿真及測(cè)試驗(yàn)證,該方案能滿足檢測(cè)指標(biāo)要求,從而為多信道頻率檢測(cè)技術(shù)提供一種設(shè)計(jì)參考。