在新設(shè)計及開發(fā)項目的開始,正確選擇有源與無源器件及完善的電路設(shè)計技術(shù),將有利于以最低的成本獲得EMC認證,減少產(chǎn)品因屏蔽和濾波所帶來的額外的成本、體積和重量。 這些技術(shù)也可以提高數(shù)字信號的完整性及模擬信號信噪比,可以減少重復(fù)使用硬件及軟件至少一次,這也將有助于新產(chǎn)品達到其功能技術(shù)要求,盡早投入市場。這些EMC技術(shù)應(yīng)視為公司竟?fàn)巸?yōu)勢的一部分,有助于使企業(yè)獲得最大的商業(yè)利益。

1.1數(shù)字器件與EMC電路設(shè)計

1.1.1器件的選擇

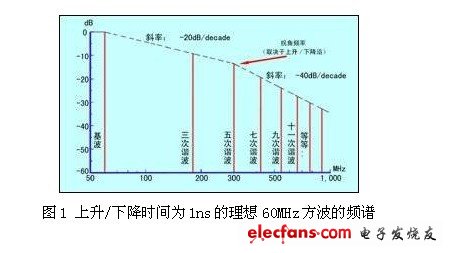

大部分數(shù)字IC生產(chǎn)商都至少能生產(chǎn)某一系列輻射較低的器件,同時也能生產(chǎn)幾種抗ESD的I/O芯片,有些廠商供應(yīng)EMC性能良好的VLSI(有些EMC微處理器比普通產(chǎn)品的輻射低40dB);大多數(shù)數(shù)字電路采用方波信號同步,這將產(chǎn)生高次諧波分量,如圖1示。時鐘速率越高,邊沿越陡,頻率和諧波的發(fā)射能力也越高。 因此,在滿足產(chǎn)品技術(shù)指標(biāo)的前提下,盡量選擇低速時鐘。在HC能用時絕不要使用AC,CMOS4000能行就不要用HC。要選擇集成度高并有EMC特性的集成電路,比如:

* 電源及地的引腳較近

* 多個電源及地線引腳

* 輸出電壓波動性小

* 可控開關(guān)速率

* 與傳輸線匹配的I/O電路

* 差動信號傳輸

* 地線反射較低

* 對ESD及其他干擾現(xiàn)象的抗擾性

* 輸入電容小

* 輸出級驅(qū)動能力不超過實際應(yīng)用的要求

* 電源瞬態(tài)電流低(有時也稱穿透電流)

這些參數(shù)的最大、最小值應(yīng)由其生產(chǎn)商一一指明。由不同廠家生產(chǎn)的具有相同型號及指標(biāo)的器件可能有顯著不同的EMC特性,這一點對于確保陸續(xù)生產(chǎn)的產(chǎn)品具有穩(wěn)定的電磁兼容符合性是很重要的。

高技術(shù)集成電路的生產(chǎn)商可以提供詳盡的EMC設(shè)計說明,比如Intel的奔騰MMX芯片就是這樣。設(shè)計人員要了解這些并嚴(yán)格按要求去做。詳盡的EMC設(shè)計建議表明:生產(chǎn)商關(guān)心的是用戶的真正需求,這在選擇器件時是必須考慮的因素。在早期設(shè)計階段,如果IC的EMC特性不清楚,可以通過一簡單功能電路(至少時鐘電路要工作)進行各種EMC測試,同時要盡量在高速數(shù)據(jù)傳輸狀態(tài)完成操作。發(fā)射測試可方便地在一標(biāo)準(zhǔn)測試臺上進行,將近場磁場探頭連接到頻譜分析儀(或?qū)拵静ㄆ?上,有些器件明顯地比其他一些器件噪聲小得多,測試抗擾度時可采用同樣的探頭,并連到信號發(fā)生器的輸出端(連續(xù)射頻或瞬態(tài))。但如果探頭是儀器專配的(不只是簡單的短路環(huán)或?qū)Ь€),首先要檢查其功率承受能力是否滿足要求。測試時近場探頭需貼近器件或PCB板,為了定位“關(guān)鍵探測點”和最大化探頭方向 , 應(yīng)首先在整個區(qū)域進行水平及垂直掃描(使探頭在各個方向相互垂直),然后在信號最強的區(qū)域集中進行掃描。

1.1.2 不宜采用IC 座

IC座對EMC 很不利,建議直接在PCB上焊接表貼芯片,具有較短引線和體積較小的IC芯片則更好, BGA及類似芯片封裝的IC在目前是最好的選擇。安裝在座(更糟的是,插座本身有電池)上的可編程只讀存儲器(PROM)的發(fā)射及敏感特性經(jīng)常會使一個本來良好的設(shè)計變壞。因此,應(yīng)該采用直接焊接到電路板上的表貼可編程儲存器

帶有ZIF座和在處理器(能方便升級)上用彈簧安裝散熱片的母板,需要額外的濾波和屏蔽,即使如此,選擇內(nèi)部引線最短的表貼ZIF 座也是有好處的。

1.1.3電路技術(shù)

* 對輸入和按鍵采用電平檢測(而非邊沿檢測)

* 使用前沿速率盡可能慢且平滑的數(shù)字信號(不超過失真極限)

* 在PCB樣板上,允許對信號邊沿速度或帶寬進行控制(例如,在驅(qū)動端使用軟鐵氧體磁珠或串聯(lián)電阻)

* 降低負載電容,以使靠近輸出端的集電極開路驅(qū)動器便于上拉,電阻值盡量大 * 處理器散熱片與芯片之間通過導(dǎo)熱材料隔離,并在處理器周圍多點射頻接地。

* 電源的高質(zhì)量射頻旁路(解耦)在每個電源管腳都是重要的。

* 高質(zhì)量電源監(jiān)視電路需對電源中斷、跌落、浪涌和瞬態(tài)干擾有抵抗能力

* 需要一只高質(zhì)量的看門狗

* 決不能在看門狗或電源監(jiān)視電路上使用可編程器件

* 電源監(jiān)視電路及看門狗也需適當(dāng)?shù)碾娐泛蛙浖夹g(shù),以使它們可以適應(yīng)大多數(shù)的不測情況,這取決于產(chǎn)品的臨界狀態(tài)

* 當(dāng)邏輯信號沿的上升/下降時間比信號在PCB走線中傳輸一個來回的時間短時,應(yīng)采用傳輸線技術(shù):

a 、經(jīng)驗:信號在每毫米軌線長度中傳輸一個來回的時間等于36皮秒

b 、為了獲得最佳EMC特性,對于比a中經(jīng)驗提示短得多的軌線,使用傳輸線技術(shù)

有些數(shù)字IC產(chǎn)生高電平輻射,常將其配套的小金屬盒焊接到PCB地線而取得屏蔽效果 。PCB上的屏蔽成本低,但在需散熱和通風(fēng)良好的器件上并不適用。

時鐘電路通常是最主要的發(fā)射源,其PCB軌線是最關(guān)鍵的一點,要作好元件的布局,從而使時鐘走線最短,同時保證時鐘線在PCB的一面但不通過過孔。當(dāng)一個時鐘必須經(jīng)過一段長長的路徑到達許多負載時,可在負載旁邊安裝一時鐘緩沖器,這樣,長軌線(導(dǎo)線)中的電流就小很多了。這里,相對的失真并非重要。長軌線中的時鐘沿應(yīng)盡量圓滑,甚至可用正弦波,然后由負載旁的時鐘緩沖器加以整形。

1.1.4擴展頻譜時鐘

所謂的“擴展頻譜時鐘”是一項能夠減小輻射測量值的新技術(shù),但這并非真正減小了瞬時發(fā)射功率,因此,對一些快速反應(yīng)設(shè)備仍可能產(chǎn)生同樣的干擾。這種技術(shù)對時鐘頻率進行1% ~ 2% 的調(diào)制,從而擴散諧波分量,這樣在CISPR16或FCC發(fā)射測試中的峰值較低。所測的發(fā)射減小量取決于帶寬和測試接收機的積分時間常數(shù),因此這有一點投機之嫌,但該項技術(shù)已被FCC所接受,并在美國和歐洲廣泛應(yīng)用。調(diào)制度要控制在音頻范圍內(nèi),這樣才不會使時鐘信號失真,圖2是一時鐘諧波發(fā)射改善的例子。擴展頻譜時鐘不能應(yīng)用于要求嚴(yán)格的時間通信網(wǎng)絡(luò)中,比如以太網(wǎng)、光纖、FDD、ATM、SONET和ADSL。

絕大多數(shù)來自數(shù)字電路發(fā)射的問題是由于同步時鐘信號。非同步邏輯(比如AMULET微處理器,正由steve Furbe教授領(lǐng)導(dǎo)的課題組在UMIST研制)將大大地降低發(fā)射量,同時也可獲得真正的擴頻效果,而不只是集中在時鐘諧波上產(chǎn)生發(fā)射。

1.2模擬器件和電路設(shè)計

1.2.1 選擇模擬器件

從EMC的角度選擇模擬器件不象選擇數(shù)字器件那樣直接,雖然同樣希望發(fā)射、轉(zhuǎn)換速率、電壓波動、輸出驅(qū)動能力要盡量小,但對大多數(shù)有源模擬器件,抗擾度是一個很重要的因素,所以確定明確的EMC訂購特征相當(dāng)困難。

來自不同廠商的同一型號及指標(biāo)的運算放大器,可以有明顯不同的EMC性能,因此確保后續(xù)產(chǎn)品性能參數(shù)的一致性是十分重要的。敏感模擬器件的廠商提供EMC或電路設(shè)計上的信噪處理技巧或PCB布局,這表明他們關(guān)心用戶的需求,這有助于用戶在購買時權(quán)衡利弊。

1.2.2 防止解調(diào)問題

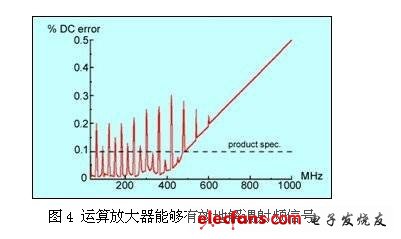

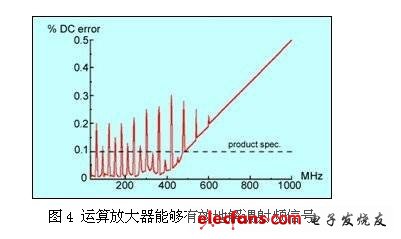

大多數(shù)模擬設(shè)備的抗擾度問題是由射頻解調(diào)引起的。運放每個管腳都對射頻干擾十分敏感,這與所使用的反饋線路無關(guān)(見圖3),所有半導(dǎo)體對射頻都有解調(diào)作用,但在模擬電路上的問題更嚴(yán)重。即使低速運放也能解調(diào)移動電話頻率及其以上頻率的信號,圖4表明了實際產(chǎn)品的測試結(jié)果。為了防止解調(diào),模擬電路處于干擾環(huán)境中時需保持線性和穩(wěn)定,尤其是反饋回路,更需在寬頻帶范圍內(nèi)處于線性及穩(wěn)定狀態(tài),這就常常需要對容性負載進行緩沖,同時用一個小串聯(lián)電阻(約為500)和一個大約5PF的積分反饋電容串聯(lián)。

進行穩(wěn)定度及線性測試時,在輸入端注入小的但上升沿極陡 (<1ns) 的方波信號(也可以通過電容饋送到輸出端和電源端),方波的基頻必須在電路預(yù)期的頻帶內(nèi),電路輸出應(yīng)用100MHz(至少)的示波器和探針進行過沖擊和振鈴檢查,對音頻或儀表電路也應(yīng)如此,對更高速模擬電路,要選取頻帶更寬的示波器,同時注意使用探頭的技巧

超過信號高度50%的過沖擊表明電路不穩(wěn)定,對過沖擊應(yīng)予以有效的衰減,信號的任何長久的振鈴(超過兩個周期)或突發(fā)振蕩表明其穩(wěn)定度不好。

以上測試應(yīng)在輸入及輸出端均無濾波器的情況下進行,也可以用掃頻代替方波,頻譜分析儀代替示波器(更易看出共振頻率)

1.2.3其它模擬電路技術(shù)

獲得一穩(wěn)定且線性的電路后,其所有聯(lián)線可能還需濾波,同一產(chǎn)品中的數(shù)字電路部分總會把噪聲感應(yīng)到內(nèi)部連線上,外部連線則承受外界的電磁環(huán)境的騷擾。濾波器將在后面介紹。

決不要試圖采用有源電路來濾波和抑制射頻帶寬以達到EMC要求,只能使用無源濾波器(最好是RC型)。在運放電路中,只有在其開環(huán)增益遠大于閉環(huán)增益時的頻率范圍內(nèi),積分反饋法才有效,但在更高頻率,它不能控制頻率響應(yīng)。

應(yīng)避免采用輸入、輸出阻抗高的電路,比較器必須具有遲滯特性(正反饋),以防止因為噪聲和干擾而使輸出產(chǎn)生誤動作,還可防止靠近切換點處的振蕩 。不要使用比實際需要快得多的輸出轉(zhuǎn)換比較器,保持dv/dt在較低狀態(tài)。

對高頻模擬信號(例如射頻信號),傳輸線技術(shù)是必需的,取決于其長度和通信的最高頻率,甚至對低頻信號,如果對內(nèi)部聯(lián)接用傳輸線技術(shù),其抗擾度也將有所改善。有些模擬集成電路內(nèi)的電路對高場強極為敏感,這時可用小金屬殼將其屏蔽起來(如果散熱允許),并將屏蔽盒焊接到PCB地線面上

與數(shù)字電路相同,模擬器件也需要為電源提供高質(zhì)量的射頻旁路(去耦),但同時也需低頻電源旁路,因為模擬器件的電源噪聲抑制率(PSRR)對1kHz以上頻率是很微弱的,對每個運放、比較器或數(shù)據(jù)轉(zhuǎn)換器的每個模擬電源引腳的RC或LC濾波都是必要的,這些電源濾波器轉(zhuǎn)折頻率和過渡帶斜率應(yīng)補償器件PSRR的轉(zhuǎn)折頻率和斜率,以在所關(guān)心的頻帶內(nèi)獲得期望的PSRR

一般的EMC設(shè)計指南中都很少涉及射頻設(shè)計,這是因為射頻設(shè)計者一般都很熟悉大多數(shù)連續(xù)的EMC現(xiàn)象,然而需要注意的是,本振和IF頻率一般都有較大的泄漏 ,所以需要著重屏蔽和濾波。