0 引言

近幾年來,隨著混合微電子技術的快速發(fā)展及其應用領域的不斷擴大,,使其在通信行業(yè)和計算機系統有了快速的發(fā)展和廣泛的應用,。隨之電子和通信業(yè)界對于現代電子元器件(例如大規(guī)模集成電路)、電路小型化,、高速度,、低電源電壓、低功耗和提高性價比等方面的要求越來越高,。傳統的雙極技術雖然具有高速,、電流驅動能力強和模擬精度高等優(yōu)點,但其功耗和集成度卻不能適應現代VLSI技術發(fā)展的需要,。而一直作為硅鍺(SiGe)集成電路主要技術平臺的MOS器件及其電路雖在高集成度,、低功耗、強抗干擾能力等方面有著雙極電路無法比擬的優(yōu)勢,,但在高速,、大電流驅動場合卻無能為力。由此可見,,無論是單一的CMOS,,還是單一的雙極技術都無法滿足VLSI系統多方面性能的要求,因此只有融合CMOS和單一的雙極技術這兩種優(yōu)勢構造BiCMOS器件及其電路,,才是VLSI發(fā)展的必然產物,。由于最先提出BiCMOS器件的構造思路時,,雙極和CMOS技術在工藝和設備上差異很大,組合難度和成本都高,,同時因應用上的需求并不十分迫切,,所以BiCMOS技術的發(fā)展比較緩慢。

1 電路圖設計

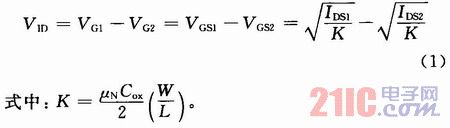

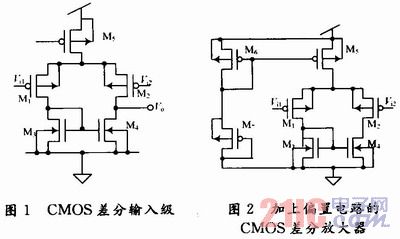

本文基于MCNC 0.5 μm CMOS工藝線設計了BiCMOS器件,,其集成運算放大器由輸入級、中間級,、輸出級和偏置電路4部分組成,。輸入級由CMOS差分輸入對即兩個PMOS和NMOS組成;中間級為CMOS共源放大器,;輸出級為甲乙類互補輸出,。圖1為CMOS差分輸入級,可作為集成運算放大器的輸入級,。NMOS管M1和M2作為差分對輸入管,,它的負載是由NMOS管M3和M4組成的鏡像電流源;M5管用來為差分放大器提供工作電流,。M1管和M2管完全對稱,,其工作電流IDS1和IDS2由電流源Io提供。輸出電流IDS1和IDS2的大小取決于輸入電壓的差值VG1-VG2,。IDS1和IDS2之和恒等于工作電流源Io,。假設M1和M2管都工作在飽和區(qū),那么如果M1和M2管都制作在孤立的P阱里,,就沒有襯偏效應,,此時VTN1=VTN2=VT。忽略MOS管溝道長度的調制效應,,差分對管的輸入差值電壓VID可表示為:

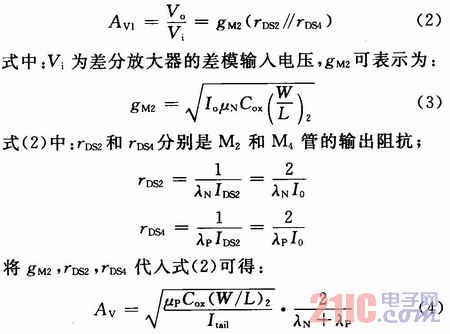

M2管和M4管構成CMOS放大器,,兩個管子都工作在飽和區(qū),其電壓增益等于M2管的跨導gM2和M2,,M4兩管的輸出阻抗并聯的乘積,,即:

式(4)表明,CMOS差分放大器具有較高的增益,。該增益隨電流的減少而增大,;隨MOS管寬長比的增加而增高;隨兩只管子溝長高調制系數λ的減少而增加,,所以設計時,,應盡可能增加溝道長度,減小λ值,,以此來提高CMOS的增益,。偏置電路用來提供各級直流偏置電流,,它由各種電流源電路組成。圖2為加上偏置電路的CMOS差分放大器,。

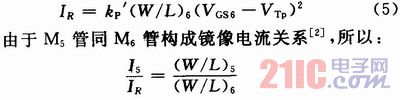

圖2中,,M5管為恒流源,用于為差分放大器提供工作電流,;M6和M7管為恒流源偏置電路,,用于為M5提供工作電流。其中,,基準電流為,;

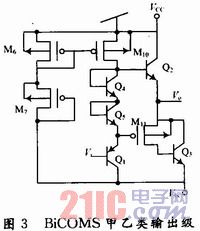

圖3為輸出級的最終結果,其中M6,,M7,,M10為偏置,Q4,,Q5用來減小交越失真,,Q1為輸出級的緩沖級。

2 電路仿真

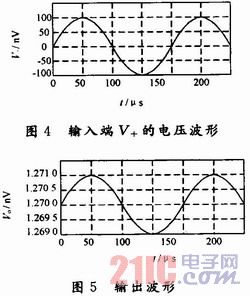

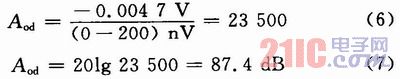

Aod是在標稱電源電壓和規(guī)定負載下,,運算放大器工作在線性區(qū),,低頻無外部反饋時的電壓增益,Aod的值越大越好,。圖4為輸入端V+的電壓波形,。由圖可見V+的峰峰值為200 nV,輸入端V-的電壓為0,。圖5為輸出波形(在Q3的集電極輸出),。

由圖5可見,輸出電壓的峰峰值為:

![]()

因此開環(huán)差模電壓增益為:

可以測量出共模電壓增益:

滿足設計要求,。

3 版圖設計

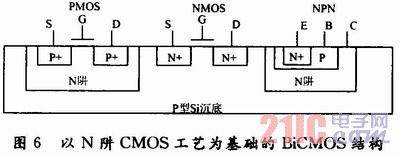

采用的是以CMOS工藝為基礎的BiCMOS兼容工藝,。首先以外延雙阱CMOS工藝為基礎,在N阱內增加了N+埋層和集電極接觸深N+注入,,用以減少BJT器件的集電極串聯電阻阻值,,以及降低飽和管壓降;其次用P+區(qū)(或N+區(qū))注入,,制作基區(qū),;再者發(fā)射區(qū)采取多晶硅摻雜形式,并與MOS器件的柵區(qū)摻雜形式一致,,制作多晶硅BJT器件,。由此可見,這種高速BiCMOS制造工藝原則上不需要增加其他的重要工序。

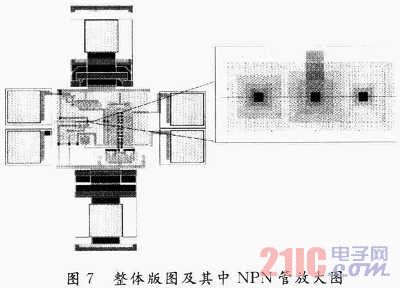

由于基準電路不易調整,,在設計版圖時將基準部分外接,。基于0.5μm CMOS工藝的運算放大器版圖如圖7所示,。

4 結語

該運算放大器結合了CMOS工藝低功耗,、高集成度和高抗干擾能力的優(yōu)點,雙極型器件的高跨導,,負載電容對其速度的影響不靈敏,,從而具有驅動能力強的優(yōu)點。該BiCMOS器件在現有CMOS工藝平臺上制造,。該放大器以CMOS器件為主要單元電路,,在驅動大電容負載之處加入雙極器件的運算放大器電路,然后在Tanner Por軟件平臺上完成電路圖的繪制,、仿真,并在MCNC 0.5μm CMOS工藝線上完成該電路的版圖設計,,經實用,,運算放大器的參數均達到了設計要求。