某機(jī)載數(shù)據(jù)傳輸設(shè)備(以下簡(jiǎn)稱:機(jī)載數(shù)傳設(shè)備)主要用來(lái)完成空-空、空-地?cái)?shù)據(jù)信息的傳輸,與HF或U/VHF頻段電臺(tái)配合使用,將專用計(jì)算機(jī)發(fā)來(lái)的待傳信息,經(jīng)過(guò)差錯(cuò)控制編碼后,經(jīng)電臺(tái)調(diào)制、發(fā)射;對(duì)電臺(tái)接收機(jī)送來(lái)的數(shù)據(jù),進(jìn)行校正、糾錯(cuò)和譯碼,還原成原始信息,傳輸給專用計(jì)算機(jī)(CUB)處理。要想實(shí)現(xiàn)對(duì)機(jī)載數(shù)傳設(shè)備的自動(dòng)檢測(cè),最重要的是要模擬實(shí)現(xiàn)機(jī)載數(shù)傳設(shè)備與機(jī)載專用計(jì)算機(jī)的通信協(xié)議。本系統(tǒng)就是為了滿足某部隊(duì)大修廠的急需,設(shè)計(jì)實(shí)現(xiàn)了某機(jī)載數(shù)傳設(shè)備與機(jī)載專用計(jì)算機(jī)之間的ARINC429通信協(xié)議。

1 系統(tǒng)硬件原理

本系統(tǒng)利用Altera公司的FPGA芯片(EP2C8QPF208),設(shè)計(jì)了該機(jī)載數(shù)傳設(shè)備在機(jī)載環(huán)境中同機(jī)載計(jì)算機(jī)之間的ARINC429通信協(xié)議模塊,實(shí)現(xiàn)一發(fā)一收。在FPGA上利用SoPC技術(shù),PC機(jī)通過(guò)與基于NiosⅡ的UART通信,由ARINC429通信協(xié)議模塊實(shí)現(xiàn)RS 232通信協(xié)議與ARINC429通信協(xié)議的相互轉(zhuǎn)換,從而模擬機(jī)載計(jì)算機(jī)提供測(cè)試激勵(lì),完成與設(shè)備的信息交換。

2 ARINC429通信協(xié)議介紹

ARINC429是一種在航空電子綜合系統(tǒng)中廣泛使用的數(shù)字式傳輸總線規(guī)范,該通信協(xié)議是雙極性歸零碼的一種,在一個(gè)ARINC429字中包含32位,ARINC429數(shù)據(jù)傳輸是以電脈沖形式發(fā)送的。一個(gè)電脈沖就是1位。一個(gè)數(shù)據(jù)字傳輸1個(gè)參數(shù),如速度、溫度等。兩個(gè)數(shù)據(jù)字之間有4位間隔,這個(gè)間隔也作為字同步用,跟在這一間隔后面發(fā)送的第1位,表示另一個(gè)新的數(shù)據(jù)字的開(kāi)始。每個(gè)數(shù)據(jù)字的32位數(shù)據(jù)是以雙極歸零碼的形式發(fā)送出去的。數(shù)據(jù)的發(fā)送是先發(fā)送高位再發(fā)送低位。

3 基于FPGA的ARINC429發(fā)送模塊的實(shí)現(xiàn)

在FPGA上利用SoPC技術(shù)實(shí)現(xiàn)與PC機(jī)的串口RS 232通信,然后在FPGA上實(shí)現(xiàn)將PC機(jī)通過(guò)RS 232傳過(guò)來(lái)的激勵(lì)信息先緩存,再轉(zhuǎn)換成ARINC 429的協(xié)議信息并以一定時(shí)鐘速率發(fā)給設(shè)備。

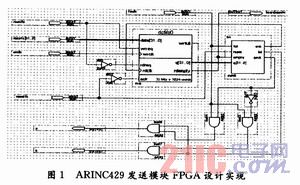

ARINC429發(fā)送模塊在QuartusⅡ8.0開(kāi)發(fā)環(huán)境中設(shè)計(jì)實(shí)現(xiàn)如圖1所示。

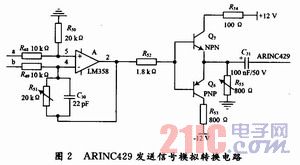

ARINC429發(fā)送模塊設(shè)計(jì)實(shí)現(xiàn)原理為:在FPGA中由NiosⅡ處理器通過(guò)UART串口接收PC機(jī)發(fā)過(guò)來(lái)的原始ARINC429信息字。在接收過(guò)程中,將這些字先緩存在FIFO發(fā)送緩存器dcfifo0中。等完全接收控制、數(shù)據(jù)信息后,再經(jīng)由bc模塊將緩存中待發(fā)送的控制、數(shù)據(jù)信息,通過(guò)設(shè)計(jì)的狀態(tài)機(jī)按ARINC429信號(hào)時(shí)序串行發(fā)送。并在與非門電路的配合下模擬發(fā)送ARINC 429信號(hào)對(duì)應(yīng)的兩路差分TTL信號(hào)a,b。最后通過(guò)在FPGA外部設(shè)計(jì)的模擬電路(如圖2)將兩路差分TTL信號(hào)a,b轉(zhuǎn)換成ARINC429信號(hào)。

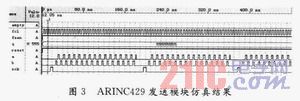

在QuartusⅡ8.O中編譯并仿真發(fā)送模塊,仿真結(jié)果如圖3所示。

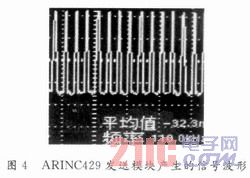

在示波器最終測(cè)得ARINC429發(fā)送模塊產(chǎn)生的信號(hào)波形,如圖4所示。

4 基于FPGA的ARINC429接收模塊的實(shí)現(xiàn)

該模塊實(shí)現(xiàn)了將數(shù)傳設(shè)備發(fā)過(guò)來(lái)的ARINC429信息先通過(guò)光耦電路分解成兩路差分信號(hào),即將ARINC429電平轉(zhuǎn)換成兩路差分FTL電平信號(hào)a,b,然后在FPGA上緩存接收,等接收完畢后,再經(jīng)由串口RS 232發(fā)給PC機(jī)進(jìn)行數(shù)據(jù)處理以進(jìn)行設(shè)備檢測(cè)。

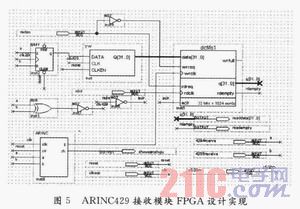

ARINC429接收模塊在QuartusⅡ8.O開(kāi)發(fā)環(huán)境中設(shè)計(jì)實(shí)現(xiàn),如圖5所示。

各個(gè)模塊的具體設(shè)計(jì)如下:

(1)RS觸發(fā)器SRFF可直接在SoPC Builder中調(diào)用,32位移位寄存器由32個(gè)D觸發(fā)器級(jí)聯(lián)產(chǎn)生。

(2)接收FIFO緩存器dcfifo1的定制過(guò)程與發(fā)送緩存器的定制過(guò)程相同,并且根據(jù)FPGA資源利用情況也設(shè)置dcfifo1為2 KB。

(3)ARINC模塊為字間隔、幀結(jié)束檢測(cè)模塊。該模塊在QuartusⅡ8.0開(kāi)發(fā)環(huán)境中利用VHDL語(yǔ)言進(jìn)行設(shè)計(jì),程序核心代碼如下:

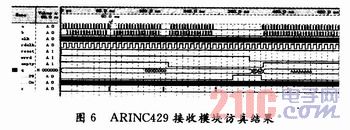

在QuartusⅡ8.O中編譯并仿真發(fā)送模塊,仿真結(jié)果如圖6所示。

5 結(jié)語(yǔ)

該設(shè)計(jì)充分利用了FPGA硬件可編程性,實(shí)現(xiàn)了ARINC429通信協(xié)議軟件算法硬件化,大大提升了ARINC429數(shù)據(jù)發(fā)送與接收的實(shí)時(shí)性和可靠性,從而實(shí)現(xiàn)了該數(shù)傳設(shè)備自動(dòng)檢測(cè)系統(tǒng)檢測(cè)速度快、集成度高、可靠性強(qiáng)的特點(diǎn)。