0 引言

2009年1月國內(nèi)3G牌照正式發(fā)放,隨著3G時代的到來,各大通信運(yùn)營商對3G移動通信網(wǎng)絡(luò)展開了大規(guī)模建設(shè),投入巨大,而基站是3G網(wǎng)絡(luò)建設(shè)中,數(shù)量最多及成本最高的設(shè)備。移動通信領(lǐng)域日趨激烈的競爭,使得通信運(yùn)營商比以往更加關(guān)注建網(wǎng)成本,而分布式基站具備低成本、高性能、快速運(yùn)營等特性,能夠大大節(jié)省運(yùn)營商的建網(wǎng)與運(yùn)維成本。因此分布式基站成為當(dāng)前3G網(wǎng)絡(luò)建設(shè)的最主要選擇。

分布式基站核心理念,是把傳統(tǒng)宏基站基帶處理單元(BBU" title="BBU">BBU)和射頻拉遠(yuǎn)單元(RRU" title="RRU">RRU)分離,二者通過光纖" title="光纖">光纖相連。網(wǎng)絡(luò)部署時,將BBU、核心網(wǎng)、無線網(wǎng)絡(luò)控制設(shè)備集中在機(jī)房內(nèi),與規(guī)劃站點(diǎn)上部署的RRU通過光纖連接,完成網(wǎng)絡(luò)覆蓋。

為了有效處理分布式基站BBU與RRU間的光纖連接,無線通信行業(yè)形成兩個聯(lián)盟,分別制定了兩種接口標(biāo)準(zhǔn):2002年諾基亞、LG、三星等宣布成立OBSAI(開放式基站結(jié)構(gòu)同盟);2003年愛立信、華為、NEC、北電和西門子等聯(lián)合成立CPRI" title="CPRI">CPRI (通用公共無線接口組織)。本文主要介紹基于CPRI協(xié)議的光纖通訊。

1 CPRI協(xié)議概述

CPRI協(xié)議定義了兩個協(xié)議層。兩個協(xié)議層為物理層(L1)和數(shù)據(jù)鏈路層(L2)。在物理層中,將上層接入點(diǎn)的傳輸數(shù)據(jù)進(jìn)行復(fù)/分接,并采用8B/10B編解碼,通過光模塊串行收發(fā)數(shù)據(jù)。數(shù)據(jù)鏈路層定義了一個同步的幀結(jié)構(gòu),包含基本幀和超幀(由256個基本幀組成),數(shù)據(jù)在L2層中,通過CPRI固定的幀結(jié)構(gòu)形式進(jìn)行相應(yīng)的成幀和解幀處理。

基帶處理單元(BBU)和射頻拉遠(yuǎn)單元(RRU)之間可以通過一條或多條CPRI數(shù)據(jù)鏈路來連接,每條CPRI數(shù)據(jù)鏈路支持614.4Mbps、1228.8M-bps和2457.6Mbps三種比特率高速串行傳輸。當(dāng)前工業(yè)界,通過將四條并行CPRI數(shù)據(jù)鏈路進(jìn)行相應(yīng)串行化處理,可實(shí)現(xiàn)BBU與RRU之間通過光纖以近10Gbps(即4X2457.6 Mbps)速率超高速傳輸。

2 硬件方案

采用FPGA" title="FPGA">FPGA來設(shè)計實(shí)現(xiàn)基于CPRI協(xié)議的光纖通訊,可以有多種方案來實(shí)現(xiàn),下面介紹兩種方案。

方案一:采用集成了RocketIO模塊的FPGA。RocketlO收發(fā)器是在Xilinx公司Virtex2 Pro以上系列FPGA芯片中,集成的功能可配置千兆位級串行收發(fā)器。可通過調(diào)用Xilinx公司的COREGenerator生成的IPCore來使用RocketIO收發(fā)器。該模塊的功能包括8B/10B編解碼,串并轉(zhuǎn)換,時鐘與數(shù)據(jù)流的綁定以及時鐘恢復(fù)等。使用此方案優(yōu)點(diǎn)是,可以使電路板尺寸較小、結(jié)構(gòu)緊湊,可方便設(shè)置參數(shù);缺點(diǎn)是,一般集成了RocketIO的FPGA芯片價格均較高,必然帶來開發(fā)成本的提高,同時開發(fā)周期相對也較長。

方案二:FPGA與SCAN25100相結(jié)合。SCAN25100是美國國家半導(dǎo)體專門為新一代基站結(jié)構(gòu)推出的串行/解串器,其集成了高精度延遲校準(zhǔn)測量(DCM)電路及獨(dú)立的發(fā)送和接收系統(tǒng)鎖相環(huán)路,還具備先進(jìn)的高速混合信號和時鐘管理以及信號調(diào)節(jié)等功能。同時芯片具備8B/10B編解碼、高速串并轉(zhuǎn)換、鎖定檢測、CPRI信號和幀丟失檢測等功能。可根據(jù)這款芯片來構(gòu)建多天線技術(shù)分布式基站光纖互連解決方案。此方案開發(fā)成本較低,調(diào)試簡單方便,性能穩(wěn)定。

2.1 方案整體設(shè)計

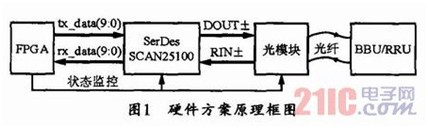

本文主要針對方案二進(jìn)行介紹與討論。該方案設(shè)計,由FPGA完成CPRI協(xié)議的成幀、解幀、同步、傳輸數(shù)據(jù)復(fù),分接等操作,以及與SCAN 25100相關(guān)接口設(shè)計,同時負(fù)責(zé)對SCAN25100與光模塊控制與狀態(tài)監(jiān)控。SCAN25100負(fù)責(zé)實(shí)現(xiàn)8B/10B編解碼和高速串并轉(zhuǎn)換功能。

FPGA與SCAN25100之間通過使用并行數(shù)據(jù)線傳輸,SCAN25100的并行數(shù)據(jù)線支持8位和10位兩種模式,這里選擇用FPGA將SCAN25100配置成10位模式。SCAN25100完成8B/10B編解碼和高速串并轉(zhuǎn)換,與光模塊通過差分串行數(shù)據(jù)線相連。最后由光模塊完成光、電信號轉(zhuǎn)換,通過光纖與外部設(shè)備進(jìn)行數(shù)據(jù)傳輸,實(shí)現(xiàn)光纖通訊數(shù)據(jù)收發(fā)。其方案原理框圖如圖1所示。

2.2 時鐘方案

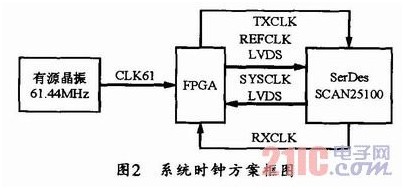

采用輸出頻率為61.44MHz的有源晶振為FPGA提供系統(tǒng)基準(zhǔn)時鐘(CLK61),系統(tǒng)所需的其他頻率時鐘,均可使用FPGA內(nèi)置的時鐘管理模塊,對CLK61進(jìn)行分頻、倍頻及移相而得。SCAN25100有四個時鐘端口,與FPGA相連。系統(tǒng)時鐘方案如圖2所示。

SCAN25100芯片內(nèi)置振蕩器能夠產(chǎn)生一個30.72MHz時鐘SYSCLK輸出,提供給FPGA作參考時鐘。當(dāng)系統(tǒng)作為REC端時,F(xiàn)PGA需要提供一個30.72MHz時鐘REFCLK,給SCAN25100作為參考時鐘。REFCLK和SYSCLK均使用LVDS差分電平,在FPGA內(nèi)部使用緩沖器IBUFGDS來將輸入差分時鐘信號轉(zhuǎn)為單端時鐘,而使用OBUFDS將單端時鐘轉(zhuǎn)為差分時鐘輸出。

TXCLK為FPGA輸出給SCAN25100,用于采集輸出數(shù)據(jù)tx_data(9:0)的時鐘。RXCLK為SCAN25100輸出給FPGA,用于采集輸入數(shù)據(jù)rx_data(9:0)的時鐘。TXCLK和RXCLK配置使用INCMOS18電平,均為雙邊沿采集數(shù)據(jù),其時鐘頻率由用戶根據(jù)需求配置SCAN25100串行接口(DOUT和RIN)的傳輸速率決定。SPMODE(1:0)的配置值決定傳輸速率,對應(yīng)關(guān)系見表1。

2.3 PCB布板設(shè)計

PCB布板設(shè)計要特別注意信號完整性問題,尤其當(dāng)系統(tǒng)設(shè)定速率為2457.6Mbps高速傳輸時。圖3所示為系統(tǒng)速率設(shè)定為2457.6Mbps,未注意信號完整性問題的PCB布板設(shè)計下,TXCLK時鐘信號眼圖,可以看到時鐘信號質(zhì)量較差。而SCAN25100對TXCLK信號質(zhì)量要求較高,如占空比要求為45%~55%范圍。經(jīng)測試,在此設(shè)計下,當(dāng)系統(tǒng)工作于614.4Mbps或1228.8Mbps時,系統(tǒng)能正常傳輸數(shù)據(jù),但當(dāng)系統(tǒng)速率轉(zhuǎn)換為2457.6Mbps,此時TXCLK/RXCLK雙邊沿對DDR(Double Data Rate)數(shù)據(jù)出現(xiàn)了錯誤采集,SCAN25100與光模塊之間的差分串行數(shù)據(jù)線傳輸也變得不穩(wěn)定。因此系統(tǒng)對PCB布板設(shè)計要求較高。