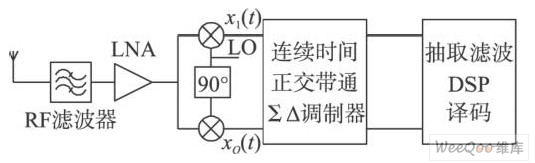

在低中頻射頻接收機(jī)中,如圖1所示,射頻信號(hào)經(jīng)過下混頻,產(chǎn)生I、Q兩路正交低中頻信號(hào),之后直接通過帶通ΣΔADC進(jìn)行模數(shù)轉(zhuǎn)換。由于中頻不在直流處,可以避免直流失調(diào)和閃爍噪聲。正交帶通ΣΔADC比傳統(tǒng)的帶通ΣΔADC更適用于低中頻架構(gòu),這是因?yàn)榍罢叩脑肼曊瘟泓c(diǎn)全部分布在單一頻域,后者的噪聲整形零點(diǎn)則對(duì)稱的分布在正負(fù)頻域,負(fù)頻域的噪聲整形零點(diǎn)是浪費(fèi),正交帶通ΣΔADC在噪聲整形性能上有優(yōu)勢(shì)。正交帶通ΣΔADC由模擬和數(shù)字兩部分組成,模擬部分是正交帶通ΣΔ調(diào)制器,數(shù)字部分是抽取濾波器,本文主要研究正交帶通ΣΔ調(diào)制器。

圖1 低中頻接收機(jī)架構(gòu)

連續(xù)時(shí)間ΣΔ調(diào)制器與離散時(shí)間ΣΔ調(diào)制器相比,它具有一些顯著的優(yōu)勢(shì),特別是無需獨(dú)立的抗混疊濾波器,同時(shí)降低對(duì)運(yùn)放單位增益帶寬和擺率的要求,從而有利于降低了調(diào)制器的功耗。文獻(xiàn)首次提出并驗(yàn)證了連續(xù)時(shí)間正交帶通ΣΔ調(diào)制器架構(gòu),近幾年文獻(xiàn)也提出了一些成功的設(shè)計(jì)。其根本設(shè)計(jì)方法都是將兩個(gè)低通濾波器的輸入輸出進(jìn)行交叉耦合來構(gòu)成一個(gè)具有帶通濾波特性的復(fù)數(shù)濾波器。

眾所周知,連續(xù)時(shí)間ΣΔ調(diào)制器有一些固有的非理想特性,時(shí)鐘抖動(dòng)就是最主要的非理想特性之一。本文主要研究如何減少時(shí)鐘抖動(dòng)影響,設(shè)計(jì)了一個(gè)對(duì)其不敏感的四階連續(xù)時(shí)間正交帶通ΣΔ調(diào)制器。

1 復(fù)數(shù)濾波器

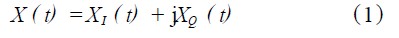

在低中頻架構(gòu)中,經(jīng)過下混頻產(chǎn)生的I、Q兩路正交實(shí)信號(hào)可以表示成一個(gè)復(fù)數(shù)信號(hào):

復(fù)數(shù)信號(hào)最重要的特性之一就是頻譜關(guān)于直流不對(duì)稱。處理復(fù)數(shù)信號(hào)就需要復(fù)數(shù)濾波器,如圖2所示,它是由實(shí)數(shù)濾波器經(jīng)過交叉耦合而形成,

圖2 復(fù)數(shù)積分器

其傳輸函數(shù)為:

實(shí)數(shù)積分器具有低通特性,其傳輸函數(shù)的頻譜關(guān)于直流對(duì)稱,而復(fù)數(shù)積分器具有帶通特性,其傳輸函數(shù)頻譜的對(duì)稱軸平移到了:

復(fù)數(shù)濾波器是構(gòu)成正交帶通ΣΔ調(diào)制器的基本模塊,其傳輸函數(shù)的極點(diǎn)就是ΣΔ調(diào)制器的噪聲整形零點(diǎn)。

2 正交帶通調(diào)制器

目前連續(xù)時(shí)間正交帶通ΣΔ調(diào)制器的設(shè)計(jì)方法主要有兩種: (1)先設(shè)計(jì)一個(gè)優(yōu)化好零點(diǎn)位置的連續(xù)時(shí)間低通ΣΔ調(diào)制器,然后用它構(gòu)成I、Q兩路,最后對(duì)兩路調(diào)制器進(jìn)行交叉耦合實(shí)現(xiàn)頻譜搬移; (2)通過平移離散時(shí)間低通ΣΔ調(diào)制器的NTF,得到一個(gè)離散時(shí)間的復(fù)數(shù)NTF,然后對(duì)它進(jìn)行DT2TO2CT變換,最終可以求得調(diào)制器的各支路系數(shù)。方法2設(shè)計(jì)過程繁瑣,且整個(gè)調(diào)制器系數(shù)多,在電路實(shí)現(xiàn)時(shí)意味著更多的元件。

本文采用的方法與第一種類似,調(diào)制器的設(shè)計(jì)分為兩步: 首先設(shè)計(jì)四階連續(xù)前饋低通ΣΔ調(diào)制器,然后根據(jù)文獻(xiàn)提供的四階ΣΔ調(diào)制器的零點(diǎn)位置確定耦合電阻大小。

四階前饋低通ΣΔ調(diào)制器整個(gè)環(huán)路濾波器是由有源RC積分器構(gòu)成的,這是因?yàn)榕c開環(huán)結(jié)構(gòu)的gm2C濾波器相比,反饋結(jié)構(gòu)的有源RC積分器具有更好的線性度。之所以選擇前饋結(jié)構(gòu),是因?yàn)榍梆伣Y(jié)構(gòu)中只有誤差信號(hào)通過整個(gè)環(huán)路濾波器,這降低了對(duì)各級(jí)積分器動(dòng)態(tài)范圍的要求,從而減少了功耗。然而前饋結(jié)構(gòu)需要額外的求和模塊,為了使求和網(wǎng)絡(luò)在大的輸入信號(hào)下仍具有良好線性,選擇采用電阻比例積分器。

量化器選擇本質(zhì)上線性的1 bit比較器,反饋路徑上采用對(duì)時(shí)鐘抖動(dòng)不敏感的開關(guān)電容DAC。

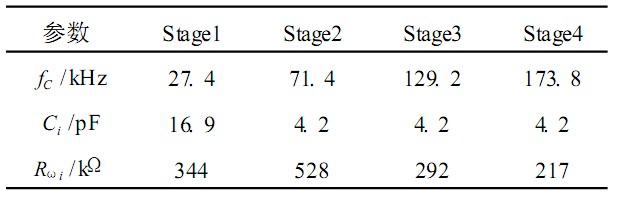

調(diào)制器零點(diǎn)頻率即為復(fù)數(shù)積分器的中心頻率fC ,根據(jù)式( 3)可以求出各級(jí)耦合電阻Rωi的值。表1反映了本文設(shè)計(jì)的正交帶通ΣΔ調(diào)制器零點(diǎn)的分布情況, Ci 為各級(jí)積分器的積分電容。

表1 調(diào)制器零點(diǎn)配置

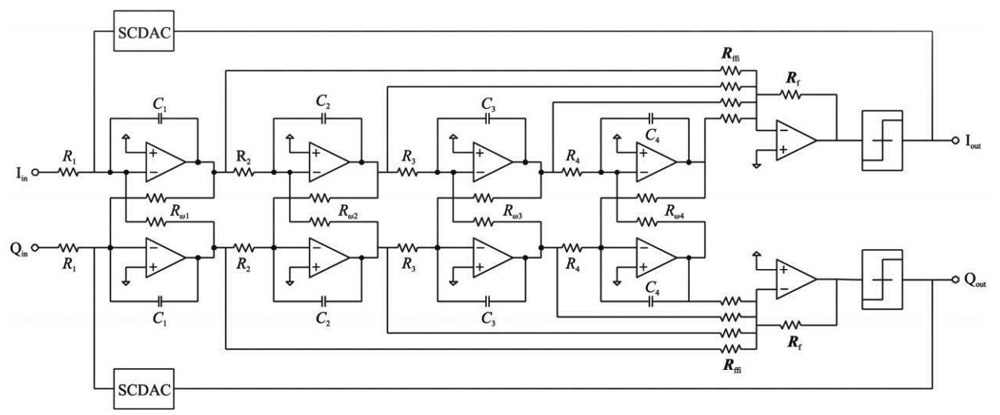

如圖3所示,這是本文設(shè)計(jì)的四階連續(xù)時(shí)間正交帶通ΣΔ調(diào)制器,它由I、Q兩路四階前饋低通ΣΔ調(diào)制器經(jīng)過電阻交叉耦合組成。

圖3 四階連續(xù)時(shí)間正交帶通ΣΔ調(diào)制器

3 時(shí)鐘抖動(dòng)

時(shí)鐘抖動(dòng)是限制連續(xù)時(shí)間ΣΔ調(diào)制器性能的主要非理想因素之一。由于時(shí)序的不確定性,在量化器對(duì)求和電路輸出進(jìn)行采樣和DAC產(chǎn)生反饋波形時(shí)都會(huì)引入誤差。在采樣過程中引入的誤差和量化噪聲一同被調(diào)制器的NTF整形。然而,DAC引入的誤差直接反饋到輸入,會(huì)限制整個(gè)調(diào)制器的性能。

采用開關(guān)電容反饋DAC能降低連續(xù)時(shí)間調(diào)制器的性能對(duì)時(shí)鐘抖動(dòng)的敏感度。

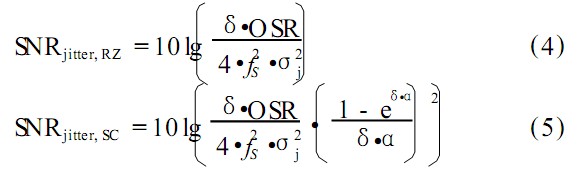

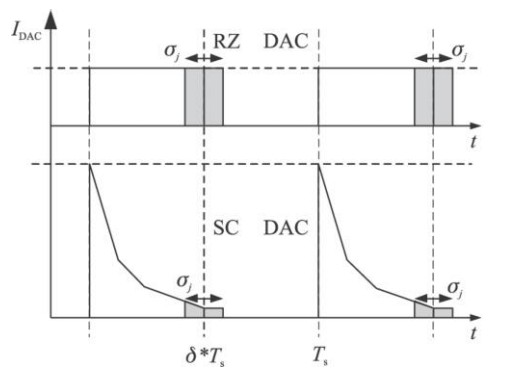

圖4反映了時(shí)鐘抖動(dòng)對(duì)歸零矩形波和指數(shù)波形的影響,在這兩種反饋波形下,時(shí)鐘抖動(dòng)對(duì)SNR 的限制分別為:

其中,δ是DAC的占空比,σj 時(shí)鐘抖動(dòng)的均分根,α =TS / (RdacCdac )是采樣周期與時(shí)間常數(shù)的比值,這里認(rèn)為時(shí)鐘抖動(dòng)是方差為σj2 的隨機(jī)白噪聲。由(5)式,可以看出時(shí)鐘抖動(dòng)引入的誤差與開關(guān)電容DAC的時(shí)間常數(shù)有關(guān)。比較以上兩式,可以看出與歸零矩形波相比,指數(shù)波形更能抑制時(shí)鐘抖動(dòng)效應(yīng)對(duì)SNR的影響。

圖4 時(shí)鐘抖動(dòng)的對(duì)反饋波形影響

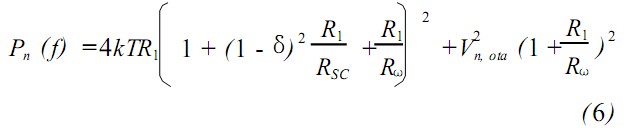

開關(guān)電容DAC的熱噪聲是調(diào)制器輸入?yún)⒖紵嵩肼暤闹匾M成部分,參考文獻(xiàn)的結(jié)論,可以推出第一級(jí)復(fù)數(shù)積分器輸入端的參考熱噪聲近似為:

其中RSC = TS /Cdac是開關(guān)電容電路的等效電阻。

4 電路模塊

ΣΔ調(diào)制器中最重要的模塊是構(gòu)成有源RC積分器和比例加法器的運(yùn)放, 1 bit量化器和開關(guān)電容反饋DAC。

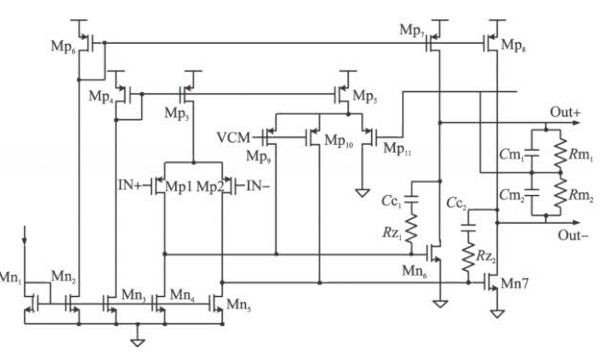

4. 1 運(yùn)放

ΣΔ調(diào)制器中的運(yùn)放都是兩級(jí)米勒結(jié)構(gòu),如圖5所示。運(yùn)放第1 級(jí)滿足增益和噪聲要求, 采用PMOS作為輸入管可以降低閃爍噪聲;第2級(jí)滿足擺幅要求。運(yùn)放的輸出被共模反饋電路檢測(cè),與參考電壓比較,誤差信號(hào)被反饋到運(yùn)放內(nèi)部,迫使運(yùn)放的輸出共模等于參考電平。與米勒電容串聯(lián)的電阻用來抵消次極點(diǎn)。

ΣΔ調(diào)制器第1級(jí)運(yùn)放直流增益為88 dB,單位增益帶寬為250 MHz,調(diào)制器中其余運(yùn)放的增益為85 dB,單位增益帶寬為45MHz。

圖5 兩級(jí)Miller運(yùn)放

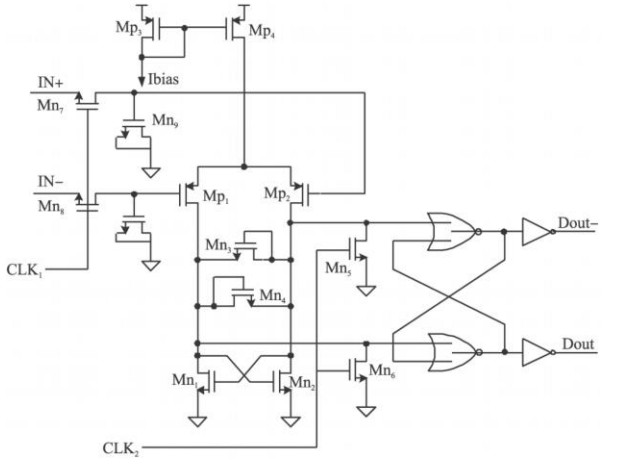

4. 2 量化器

量化器由比較器和SR鎖存器組成,如圖6 所示。比較器由Mp1 和Mp2 構(gòu)成差分輸入,Mn1 和Mn2 構(gòu)成的負(fù)阻,正的增益起到了再生作用。為了獲得更高的工作速度,在兩個(gè)輸出端之間還有兩個(gè)二極管連接Mn3 和Mn2 ,對(duì)差分輸出端的電壓進(jìn)行鉗位。當(dāng)CLK1 和CLK2 為1時(shí),所有開關(guān)管閉合,信號(hào)被采樣到MOS電容上,比較器的輸出為0,交叉耦合的或非門保持原來邏輯電平不變; 當(dāng)CLK1和CLK2 為0時(shí),所有開關(guān)管截止,比較器的一端產(chǎn)生邏輯電平1,另一段產(chǎn)生邏輯電平0, SR鎖存器更新邏輯值。

圖6 1 bit量化器

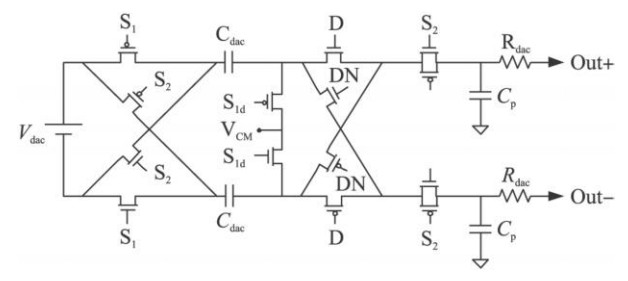

4. 3 開關(guān)電容DAC

開關(guān)電容DAC由MOS開關(guān),電容和電阻組成,如圖7所示。在第一個(gè)時(shí)鐘相,開關(guān)S1 閉合, S2 斷開,上下電容兩端的電壓為±0. 5Vref。在第二個(gè)時(shí)鐘相,開關(guān)S2 閉合, S1 斷開,電容放電,開關(guān)D 和DN決定放電通路。為了減小電荷注入效應(yīng),開關(guān)S1 比S1d提前閉合。輸出端接第一級(jí)運(yùn)放的輸入,所以在第一個(gè)時(shí)鐘相開關(guān)電容DAC的輸出端電壓等于運(yùn)放的輸入共模電壓VCM 。

圖7 開關(guān)電容DAC

5 仿真結(jié)果

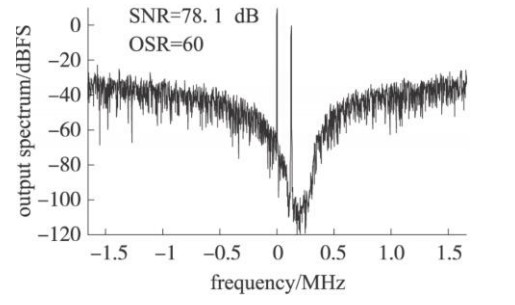

四階連續(xù)時(shí)間正交帶通ΣΔ調(diào)制器采用smic0. 13 mixed2signal CMOS工藝實(shí)現(xiàn)。采樣頻率為12MHz,過采樣率為60,有效帶寬為200 kHz,中心頻率為200 kHz。用Spectre進(jìn)行仿真驗(yàn)證,當(dāng)I、Q兩路的輸入分別為125 kHz的正弦和余弦信號(hào)時(shí),調(diào)制器的輸出功率譜密度如圖8所示,整個(gè)頻譜近似關(guān)于f = 200 kHz對(duì)稱,其SNDR為78 dB。

圖8 輸出頻譜密度

6 結(jié)論

本文提出了一個(gè)基于復(fù)數(shù)濾波器的四階連續(xù)時(shí)間帶通ΣΔ調(diào)制器電路,非常適用于低中頻架構(gòu)。

調(diào)制器采用開關(guān)電容DAC,有效減少了時(shí)鐘抖動(dòng)效應(yīng)的影響。