音頻交換混合矩陣" title="音頻交換混合矩陣">音頻交換混合矩陣是各種會(huì)議,、演播、指揮系統(tǒng)的核心設(shè)備,,連接不同的音頻輸入,、輸出設(shè)備,實(shí)現(xiàn)音頻的交換及混合功能,,并實(shí)現(xiàn)音頻信號(hào)的控制與調(diào)度,。

傳統(tǒng)的音頻矩陣通常基于模擬開關(guān)電路設(shè)計(jì),,設(shè)計(jì)復(fù)雜,,實(shí)現(xiàn)難度較大,不適合構(gòu)建中大規(guī)模交換矩陣,。而且,,大多數(shù)矩陣不具備音量調(diào)節(jié)及信號(hào)混合功能,,需要配合調(diào)音臺(tái),、信號(hào)混合器設(shè)備使用,。

本文提出一種基于FPGA ( Field ProgrammableGate Array)的音頻交換混合矩陣的設(shè)計(jì)方案。該方案以交換技術(shù)原理為基礎(chǔ),,采用數(shù)字音頻信號(hào)采樣及處理技術(shù),,構(gòu)建交換混合矩陣,實(shí)現(xiàn)了16 ×16路音頻信號(hào)的交換,、混合;設(shè)計(jì)及實(shí)現(xiàn)難度小,,且可根據(jù)系統(tǒng)需求裁減或增加系統(tǒng)交換容量、設(shè)置音頻信號(hào)采樣精度及采樣速率;每路輸入,、輸出信號(hào)的音量可以獨(dú)立進(jìn)行控制;還具有輸入輸出延時(shí)低,、信道間隔離度高、音質(zhì)好的特點(diǎn),。

1 音頻交換混合矩陣的數(shù)學(xué)模型

1. 1 交換系統(tǒng)原理

交換技術(shù)源于電話通信,,其基本任務(wù)就是在大規(guī)模網(wǎng)絡(luò)中實(shí)現(xiàn)各用戶之間信息的端到端的有效傳遞。交換技術(shù)的原理就是通過設(shè)置好的路徑,,將源端的數(shù)據(jù)可控地發(fā)往目的端,。

對(duì)于音頻系統(tǒng),交換即指將音頻信號(hào)從輸入端經(jīng)過一系列節(jié)點(diǎn)轉(zhuǎn)發(fā)到輸出端,。

1. 2 交換混合矩陣數(shù)學(xué)模型

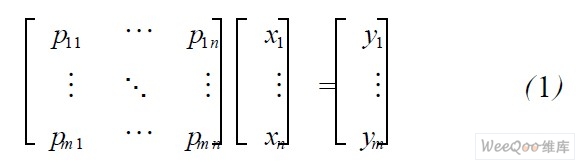

基于2. 1所述交換技術(shù)原理,,可構(gòu)建交換系統(tǒng)的一般數(shù)學(xué)模型。將多輸入輸出的交換系統(tǒng)抽象為一個(gè)矩陣P,,其輸入和輸出信號(hào)抽象為兩個(gè)向量( x,,y) ,交換系統(tǒng)實(shí)現(xiàn)的功能就是將輸入向量通過矩陣的運(yùn)算轉(zhuǎn)換為輸出向量:

其中pij ∈[0,, 1 ],,代表輸入與輸出的對(duì)應(yīng)關(guān)系。n和m 分別代表輸入和輸出信號(hào)個(gè)數(shù),。當(dāng)n = 1時(shí),,該系統(tǒng)為單輸入系統(tǒng);當(dāng)n > 1時(shí),該系統(tǒng)為多輸入系統(tǒng),。

當(dāng)m = 1時(shí),,該系統(tǒng)為單輸出系統(tǒng);當(dāng)m > 1時(shí),該系統(tǒng)為多輸出系統(tǒng),。

對(duì)于一個(gè)音頻交換混合系統(tǒng),, pij即代表了某路輸入與某路輸出的對(duì)應(yīng)關(guān)系,以及音量信息,。最終,,單獨(dú)的某路輸出信號(hào)yj 可以表示為:

本方案的核心技術(shù),是將多路模擬音頻輸入信號(hào)轉(zhuǎn)換為數(shù)字輸入向量,并構(gòu)建數(shù)字交換混合矩陣,,通過對(duì)矩陣的運(yùn)算得到數(shù)字輸出向量,, 并將輸出向量轉(zhuǎn)換為模擬音頻輸出信號(hào),分配至各輸出端口,,最終實(shí)現(xiàn)音頻交換混合矩陣,。

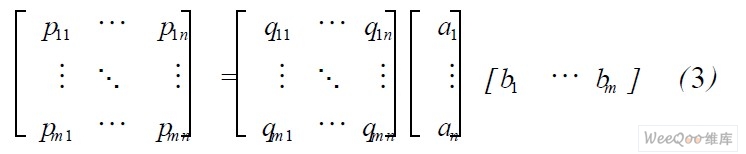

在此,設(shè)向量A,、B 分別為輸入和輸出音量控制向量,,矩陣Q 為控制矩陣,則交換矩陣P變換為:

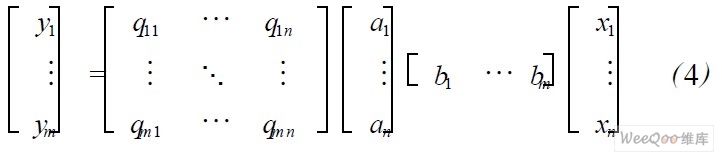

綜上,,構(gòu)建起系統(tǒng)的最終數(shù)學(xué)模型為:

其中qji = 0,, 1。

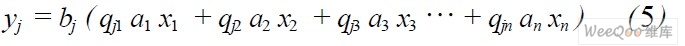

由式(4)可知,,第j路輸出的最終結(jié)果yj 為:

2 系統(tǒng)方案設(shè)計(jì)概述

2. 1 系統(tǒng)信號(hào)流程

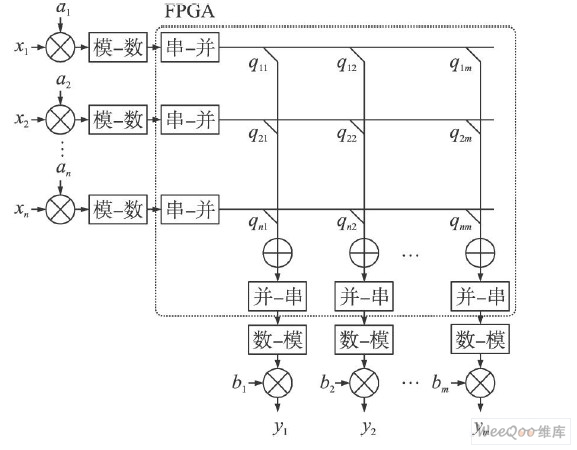

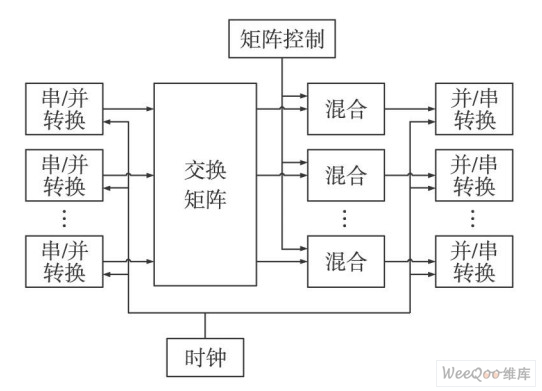

根據(jù)式( 4)及式( 5) ,, 可構(gòu)建出系統(tǒng)信號(hào)流程圖,如圖1所示,。

圖1 交換混合矩陣系統(tǒng)信號(hào)流程圖,。

ai 和bj 由音量控制芯片來實(shí)現(xiàn),數(shù)/模及模/數(shù)轉(zhuǎn)換分別由專用芯片來實(shí)現(xiàn),,矩陣Q 和多路加法器由FPGA來實(shí)現(xiàn),。

系統(tǒng)交換容量設(shè)定為16 ×16, 即n = 16,, m =16,。針對(duì)不同系統(tǒng)需求,可擴(kuò)展或縮減交換容量,。

2. 2 系統(tǒng)硬件設(shè)計(jì)

由系統(tǒng)信號(hào)流程圖可知,,系統(tǒng)總體的硬件模塊由輸入音量控制、數(shù)/模轉(zhuǎn)換,、交換混合矩陣,、模/數(shù)轉(zhuǎn)換、輸出音量控制等組成,。系統(tǒng)總體硬件模塊框圖如圖2所示,。

圖2 交換混合矩陣總體硬件模塊結(jié)構(gòu)框圖。

輸入音量控制芯片選用PGA4311,,其增益調(diào)節(jié)范圍為31. 5 dB~ - 95. 5 dB,。使用SPI總線對(duì)其進(jìn)行控制。

輸入模/數(shù)轉(zhuǎn)換芯片選用PCM4204,,該芯片采用IO接口控制工作模式和參數(shù),。具體設(shè)置方式見文獻(xiàn),。

輸出數(shù)/模轉(zhuǎn)換及音量控制芯片選用PCM1681,工作于從機(jī)方式,,使用I2C接口對(duì)其進(jìn)行控制,。具體設(shè)置及使用方法見文獻(xiàn)。

通過對(duì)模/數(shù)及數(shù)/模轉(zhuǎn)換芯片的設(shè)置,,可以根據(jù)系統(tǒng)需求調(diào)整數(shù)字音頻信號(hào)的采樣精度及頻率,。

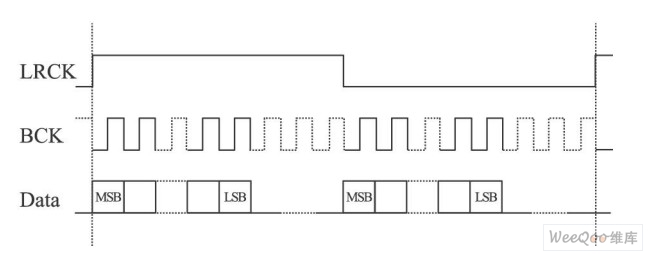

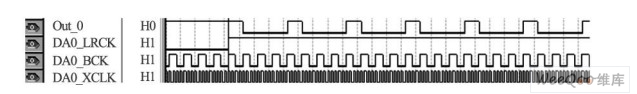

本文所述方案實(shí)例的采樣頻率為97. 7 kHz,,采樣精度為24 bit,,采用左對(duì)齊PCM編碼方式傳輸,其傳輸時(shí)序圖如圖3所示,。

圖3 PCM編碼傳送時(shí)序(左對(duì)齊),。

2. 3 FPGA及其程序設(shè)計(jì)

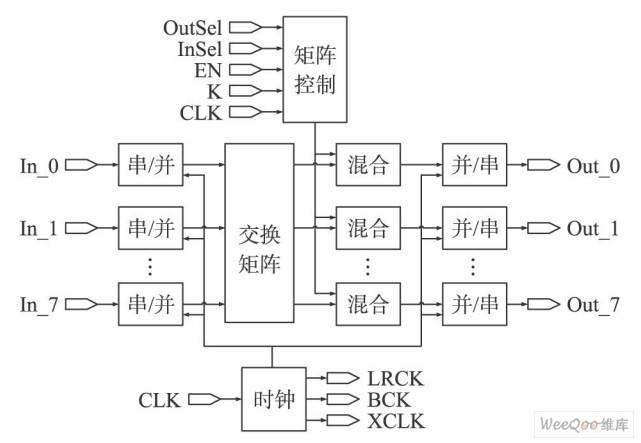

FPGA內(nèi)部包含串/并轉(zhuǎn)換、交換矩陣,、混合,、并/串轉(zhuǎn)換、時(shí)鐘模塊和矩陣控制模塊,,其內(nèi)部模塊框圖如圖4 所示,。FPGA 選用Altera的EP2C35 芯片,其具體參數(shù)見文獻(xiàn),。

2. 3. 1 時(shí)鐘模塊

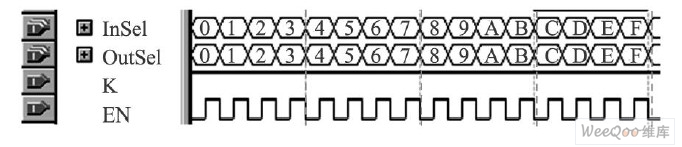

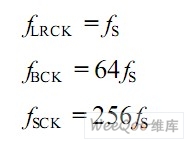

時(shí)鐘模塊的功能是為串/并,、并/串轉(zhuǎn)換模塊提供統(tǒng)一的全局時(shí)鐘。系統(tǒng)需要的時(shí)鐘信號(hào)有三種,,分別是:系統(tǒng)時(shí)鐘( SCK) ,、位時(shí)鐘(BCK)和聲道時(shí)鐘(LRCK) ,各時(shí)鐘頻率由采樣頻率( fS )決定:

圖4 FPGA內(nèi)部模塊框圖,。

本系統(tǒng)中,,采樣頻率fS 為97. 7 kHz,通過一個(gè)50MHz的外部時(shí)鐘信號(hào)分頻產(chǎn)生上述各個(gè)時(shí)鐘,。

在模塊內(nèi)建立一個(gè)9 bit累加計(jì)數(shù)器Q,,在時(shí)鐘信號(hào)的上升沿完成一個(gè)遞增計(jì)數(shù), 當(dāng)數(shù)值計(jì)到滿值111111111時(shí),, 在下一個(gè)時(shí)鐘周期將Q 置0,。將XCLK、BCK,、LRCK輸出分別連接到計(jì)數(shù)輸出的第0,、第2和第8位,并將第3 - 第7位合并成另一個(gè)計(jì)數(shù)輸出S_Count,,用于控制串- 并和并- 串轉(zhuǎn)換的位計(jì)數(shù),。所以,實(shí)際生成的fSCK為25 MHz, fBCK為6. 25MHz,, fLRCK和fS 為97. 7 kHz,。

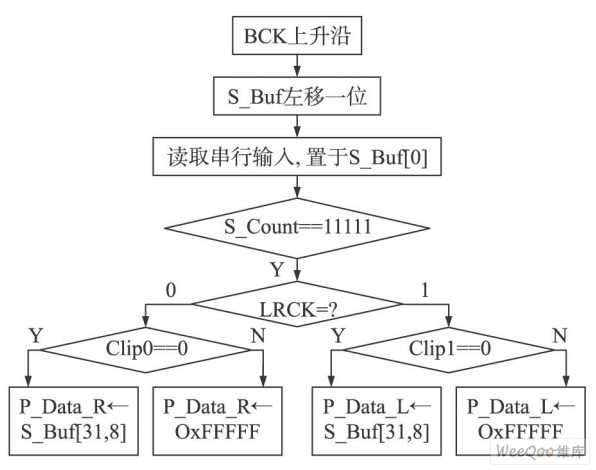

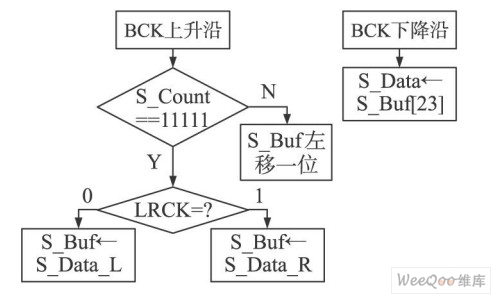

2. 3. 2 輸入串/并轉(zhuǎn)換模塊

該模塊負(fù)責(zé)將PCM4204輸入的串行PCM編碼轉(zhuǎn)換為并行數(shù)據(jù),送入交換矩陣模塊進(jìn)行處理,。模塊內(nèi)部建立通過一個(gè)32 bit移位寄存器( S_Buf) ,,用來存儲(chǔ)串行數(shù)據(jù),根據(jù)聲道時(shí)鐘(LRCK)的動(dòng)作來控制并行輸出,。串/并轉(zhuǎn)換流程如圖5所示,。

圖5 串/并轉(zhuǎn)換流程圖。

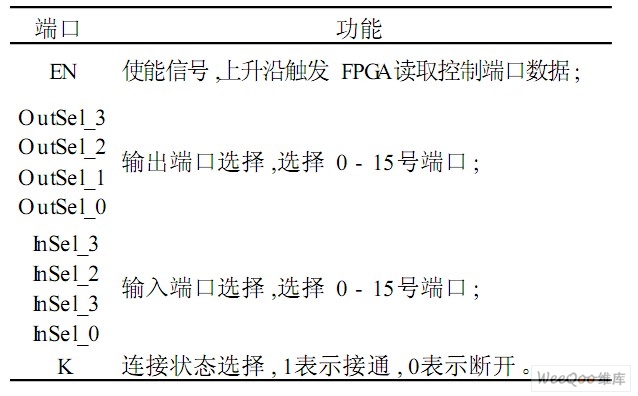

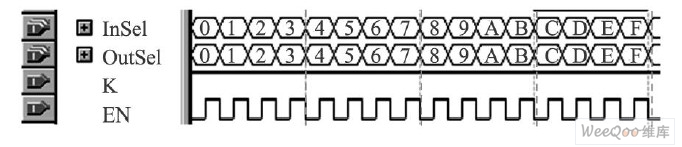

2. 3. 3 矩陣控制模塊

該模塊的功能為:接收外部控制單元的命令,,控制矩陣實(shí)現(xiàn)轉(zhuǎn)接操作,。FPGA保留10個(gè)GP IO作為使能控制端口,定義為表1,。

表1 矩陣控制端口定義

模塊的輸出是16組16 bit并行數(shù)據(jù),,形成一個(gè)矩陣表。其中,,每組數(shù)據(jù)代表輸出端口,,該組中的每個(gè)bit代表對(duì)應(yīng)的輸入端口,表中的元素代表相應(yīng)的輸入與輸出之間的連接關(guān)系,, 0表示斷開,, 1表示連接。

使用時(shí),,先選擇需要進(jìn)行操作的輸入和輸出端口以及操作狀態(tài),,然后向EN輸入高電平,觸發(fā)控制電路進(jìn)行工作,,將選擇的輸入與輸出信號(hào)相連接或斷開,。

2. 3. 4 混合模塊

該模塊由數(shù)據(jù)緩沖寄存器(AdderBuf)和加法器(Adder)兩部分組成。數(shù)據(jù)緩沖寄存器讀取控制端口( Sel)的狀態(tài),,然后判斷各個(gè)輸入是否有效,,即是否送入到輸出端口。若某輸入端口有效,,則將該端口數(shù)據(jù)直接送入加法器;若無效則送出數(shù)據(jù)0,。

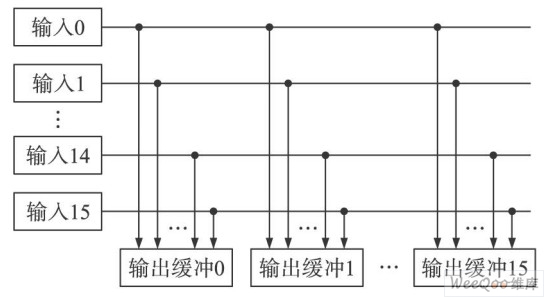

2. 3. 5 交換矩陣模塊

交換矩陣的工作原理是一個(gè)16轉(zhuǎn)256的分配器,將每一路輸入分配為16路,,分別送入每一路輸出的混合模塊中,。其結(jié)構(gòu)如圖6所示。

圖6 交換矩陣模塊結(jié)構(gòu)圖,。

2. 3. 6 輸出并/串轉(zhuǎn)換模塊

該模塊負(fù)責(zé)將混合模塊輸出的24 bit并并行數(shù)據(jù)轉(zhuǎn)化為PCM1681能夠接收的串行PCM編碼,。數(shù)據(jù)傳輸格式與PCM4204相同,。模塊內(nèi)部建立一個(gè)24 bit移位寄存器,用來產(chǎn)生串行輸出,,根據(jù)聲道時(shí)鐘(LRCK)的動(dòng)作判斷讀取并行輸入,。并/串轉(zhuǎn)換流程如圖7所示。

圖7 并/串轉(zhuǎn)換流程圖,。

3 系統(tǒng)仿真及實(shí)現(xiàn)

3. 1 系統(tǒng)仿真

FPGA總體端口及模塊框圖如圖8所示,。

圖8 FPGA總體端口及模塊框圖。

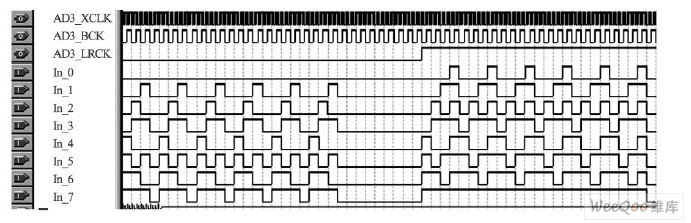

由時(shí)鐘輸入端(CLK)輸入50 MHz時(shí)鐘信號(hào);在交換控制端口送入控制信號(hào),,使In_0與Out_0相連,, In_1與Out_1相連, ……,, In_7與Out_7相連,,控制信號(hào)輸入如圖9所示,。

圖9 控制信號(hào)輸入,。

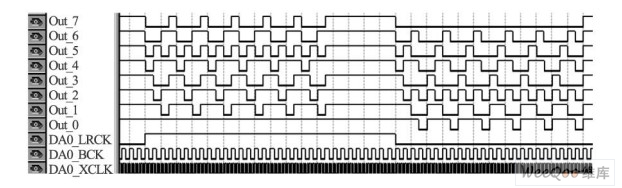

在第一路串行信號(hào)輸入端( In_0)的左聲道輸入時(shí)序輸入16進(jìn)制串行數(shù)據(jù)000000,在右聲道輸入時(shí)序輸入111111;同理,,在In_1的左聲道輸入時(shí)序輸入222222,,在右聲道輸入時(shí)序輸入333333; ?在In_7的左聲道輸入時(shí)序輸入EEEEEE,在右聲道輸入時(shí)序輸入FFFFFF,。串行數(shù)據(jù)輸入如圖10所示,。

圖10 串行數(shù)據(jù)輸入。

系統(tǒng)的串行輸出端有相應(yīng)數(shù)據(jù)輸出,, Out_0 端左聲道輸出數(shù)據(jù)為000000,, 右聲道輸出數(shù)據(jù)為111111,與In_0輸入數(shù)據(jù)一致;Out_1端左聲道輸出數(shù)據(jù)222222,,右聲道輸出數(shù)據(jù)333333,,與In_1輸入數(shù)據(jù)一致; ?; Out_7 端左聲道輸出數(shù)據(jù)EEEEEE,右聲道輸出數(shù)據(jù)FFFFFF,,與In _7 輸入數(shù)據(jù)一致,。

串行數(shù)據(jù)輸出如圖11所示。

圖11 串行數(shù)據(jù)輸出,。

改變控制端口數(shù)據(jù),,使In_1的左聲道輸入(數(shù)據(jù)為222222 ) 與In _ 2 的右聲道輸入(數(shù)據(jù)為555555)與Out_0的左聲道輸出連接。由圖3 - 5可見,,Out_0串行數(shù)據(jù)輸出變?yōu)?77777,。串行數(shù)據(jù)混合輸出如圖12所示。

由以上仿真結(jié)果可知,, FPGA 整體設(shè)計(jì)能夠?qū)崿F(xiàn)串行數(shù)字音頻信號(hào)的交換與混合,,達(dá)到預(yù)期設(shè)計(jì)要求,。

圖12 串行數(shù)據(jù)混合輸出。

3. 2 系統(tǒng)實(shí)現(xiàn)

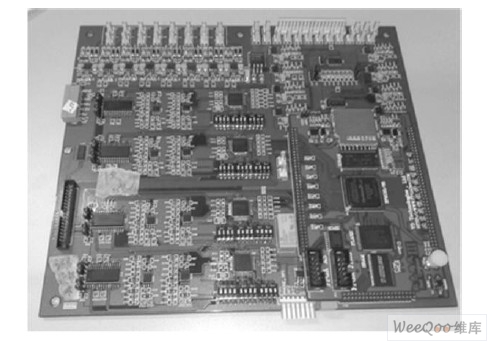

交換混合矩陣實(shí)物照片如圖13所示,。

圖13 交換混合矩陣實(shí)物照片

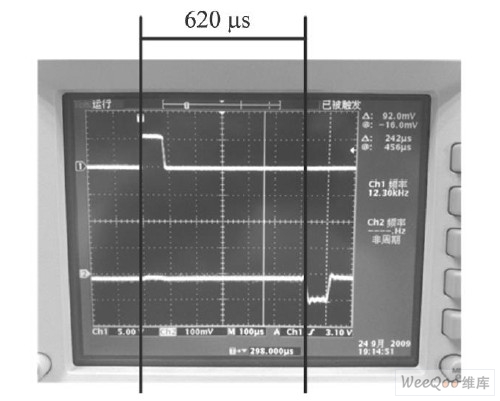

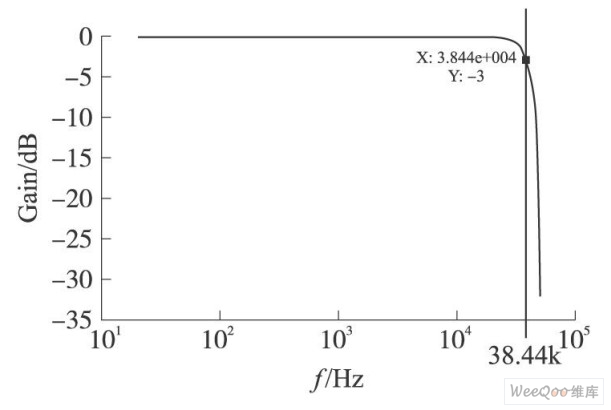

實(shí)物測試時(shí),,先將交換混合矩陣接入嵌入式控制系統(tǒng),利用嵌入式控制系統(tǒng)對(duì)其進(jìn)行控制,。采用計(jì)算機(jī),、MP3、便攜式CD 機(jī),、信號(hào)發(fā)生器等播放的音頻信號(hào)作為輸入源,,揚(yáng)聲器及耳機(jī)、示波器等作為輸出設(shè)備,,測試交換,、混合及音量調(diào)節(jié)功能。經(jīng)*測試,,輸出音頻信號(hào)無明顯失真,。在多路音頻信號(hào)混合輸出時(shí),仍然可以保證較好的信號(hào)質(zhì)量,。輸入輸出延時(shí)的測量波形如圖14所示,,約為620μs。通過逐點(diǎn)測量得到幅頻特性曲線如圖15所示,,通頻帶為20 Hz~38. 44 kHz,。

圖14 輸入輸出延遲測量波形。

圖15 幅頻特性曲線,。

測試結(jié)果證明,,交換混合矩陣能夠正確接受控制系統(tǒng)的命令,完成音頻信號(hào)的交換,、混合及音量調(diào)節(jié)功能,。

4 結(jié)論

本文針對(duì)音頻交換系統(tǒng)應(yīng)用需求,提出了一種基于FPGA音頻交換混合矩陣的設(shè)計(jì)方案,,并進(jìn)行軟硬件設(shè)計(jì)闡述及仿真,,并完成了實(shí)物制作與測試。

本文所述方案采用FPGA作為交換混合矩陣的核心器件,,因此具有較強(qiáng)的通用性,,可根據(jù)實(shí)際需要裁減或增加交換容量、配置音頻信號(hào)采樣頻率及采樣精度等特點(diǎn),。

經(jīng)仿真及實(shí)物測試,,基于FPGA的音頻交換混合矩陣能夠?qū)崿F(xiàn)音頻信號(hào)的交換、混合及音量調(diào)節(jié),,同時(shí)具有延時(shí)低,、隔離度高,、音質(zhì)好的特點(diǎn),可適用于各種會(huì)議,、指揮,、通信等場合。