在日常工作和學(xué)習(xí)中,經(jīng)常需要對作息時間進行控制,以規(guī)范工作、學(xué)習(xí)、休息等作息秩序,本文采用51系列單片機機實現(xiàn)對校園作息時間的控制設(shè)計,已完成對每天對作息最多40次打鈴控制,同時具有對控制器日常時間調(diào)整及顯示、打鈴時間設(shè)置、掉電數(shù)據(jù)不丟失等功能。

系統(tǒng)硬件結(jié)構(gòu)組成

為實現(xiàn)上述功能,硬件方面主要采用AT89C52單片機實現(xiàn)對整個系統(tǒng)控制,采用DS1302時鐘芯片完成對控制器時間的計時控制,同時采用24C02串行存儲芯片保存打鈴時間控制參數(shù)以免掉電丟失,設(shè)計8個按鍵分別用于對時間調(diào)整和打鈴時間的設(shè)置和調(diào)整,并采用靜態(tài)顯示方法對6個數(shù)碼管控制已完成對時間及打鈴時間點等參數(shù)的設(shè)置和調(diào)整顯示,采用繼電器控制電路完成弱電對強電220V控制以完成對電鈴的通斷電控制從而控制鈴聲。具體電路圖如圖1所示。

圖1 作息打鈴控制器硬件原理圖

MCS-51模擬IIC總線

本設(shè)計為防止掉電后所設(shè)置電鈴時間點數(shù)據(jù)丟失,特用一片IIC協(xié)議串行通信的含有256字節(jié)的EEPROM芯片CAT24WC02作為存儲芯片。IIC協(xié)議允許系統(tǒng)設(shè)計者只用兩根線就可以將多達128個不同的設(shè)備連接在一起,極大的節(jié)省了單片機接口線,只需在這兩根線上分別加一個10kΩ的上拉電阻,即可解決阻抗匹配問題。IIC器件通過各自的硬件連線方式來確定自己的地址,如本設(shè)計中CAT24WC02芯片地址為0000。對于沒有IIC總線接口的單片機來說,使用任何兩根線均可模擬IIC總線時序。在本設(shè)計中采用P3.3、P3.4分別來模擬SCL和SDA線,當(dāng)SCL處于高電平時,SDA由高電平變成低電平時構(gòu)成一個開始條件,對IIC總線的所有操作均須由開始條件開始;當(dāng)SCL處于高電平時,SDA由低電平變成高電平時構(gòu)成一個停止條件,此時IIC總線的所有操作均停止;當(dāng)SCL為低電平且SDA線電平變化時,則數(shù)據(jù)由CPU輸出到IIC總線;當(dāng)SCL為高電平且SDA線電平不變時,則CPU讀取IIC總線上的數(shù)據(jù);當(dāng)SCL為高電平且SDA電平變化時,IIC總線上位開始條件或停止條件;數(shù)據(jù)傳輸以8為序列進行,IIC器件在第9個時鐘周期時將SDA置位為低電平,即送出一個確認(rèn)(應(yīng)答)信號ACK,表明數(shù)據(jù)已經(jīng)被其收到。這里使用到以下4個公用函數(shù):

void I2cStart(); //產(chǎn)生開始信號

void I2cStop(); //產(chǎn)生停止信號

void I2cSendByte(uchar ByteData) ;//發(fā)送一個字節(jié)數(shù)據(jù)

uchar I2cReceiveByte(); //接收一個字節(jié)數(shù)據(jù)

DS1302時鐘電路

DS1302是美國Dallas公司推出的一種高性能、低功耗、帶RAM的實時時鐘芯片,它可以對年、月、日、星期、時、分、秒進行計時,具有閏年補償功能,工作電壓寬達2.5V~5.5V。采用三線接口與CPU進行同步通信,并可采用突發(fā)方式一次傳送多個字節(jié)的時鐘信號或RAM數(shù)據(jù)。DS1302內(nèi)部有一個31字節(jié)用于臨時性存放數(shù)據(jù)的RAM寄存器。DS1302控制電路圖如圖1所示,VCC1為后備電源, VCC2為主電源,在主電源關(guān)閉的情況下,也能保持時鐘連續(xù)運行。DS1302由VCC1或VCC2兩者中的電壓較大者供電,當(dāng)VCC2大于VCC1+0.2V時,VCC2給DS1302供電,當(dāng)VCC2小于VCC1時,DS1302由VCC1供電。X1、X2為振蕩源,外接32.768kHz晶振。RST是復(fù)位/片選線,通過把RST輸入驅(qū)動置高電平來啟動所有的數(shù)據(jù)傳送。RST輸入有兩種功能:1、RST接通控制邏輯,允許地址/命令序列送入移位寄存器;2、RST提供了終止單字節(jié)或多字節(jié)數(shù)據(jù)的的傳送手段,當(dāng)RST為高電平時,所有的數(shù)據(jù)傳送被初始化,允許對DS1302進行操作。如果在傳送工程中置RST為低電平,則會終止此次數(shù)據(jù)傳送,并且I/O引腳為高阻態(tài)。上電運行時,在 VCC≥2.5V之前,RST必須保持低電平。

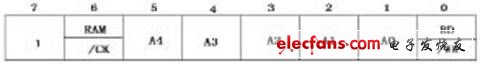

DS1302的控制字如圖2所示,字節(jié)的最高位(第7位)必須是邏輯1,如為0則不能報數(shù)據(jù)寫入到DS1302,位6如為0,則表示存取日歷時鐘數(shù)據(jù),為1表示存取RAM數(shù)據(jù);為5為至位1指示操作單元的地址,最低位(第0位)為0則表示要進行寫操作,為1表示進行讀操作,控制字節(jié)是從最低未開始輸出。在控制指令字輸入后的下一個SCLK時鐘的上升沿時數(shù)據(jù)寫入DS1302,數(shù)據(jù)輸入從低位開始,同樣,在緊跟8位控制指令字后的下一個SCLK脈沖的下降沿讀出DS1302的數(shù)據(jù),讀出數(shù)據(jù)是從低位至高位。

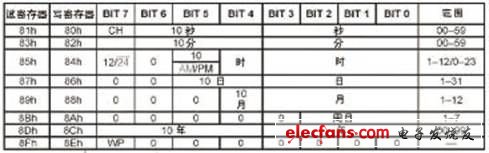

DS1302共有12個寄存器,其中7個寄存器與日歷、時鐘相關(guān),存放的數(shù)據(jù)位為BCD碼形式,其日歷、時間寄存器如圖3所示。 DS1302還有年份寄存器、充電寄存器、時鐘突發(fā)寄存器與RAM等相關(guān)寄存器。時鐘突發(fā)寄存器可一次性順序讀寫充電寄存器外的所有寄存器內(nèi)容。DS1302與RAM相關(guān)的寄存器分為兩類,一類是單個RAM單元,共31個,每個單元組態(tài)為一個8位的字節(jié),其命令控制字為C0H~FDH,其中奇數(shù)為讀操作,偶數(shù)為寫操作;另一類為突發(fā)方式下的RAM寄存器,此方式下可以一次性讀寫所有RAM的31個字節(jié),命令控制字地址寫操作時為FEH,讀操作時為FFH。

圖2 DS1320命令控制字

圖3 DS1320時鐘、日歷寄存器及控制字系統(tǒng)軟件實現(xiàn)

主程序流程

本系統(tǒng)主程序在考慮可設(shè)置每天最多40個打鈴時間點,而時間點精確的分鐘,因此每個時間點信息包括時、分兩個字節(jié)存儲,共需80字節(jié)作為打鈴時間點存儲緩沖區(qū),此緩沖區(qū)在AT89C52內(nèi)存中采用數(shù)組的形式定義,同時當(dāng)打鈴時間點設(shè)置好時,將此數(shù)據(jù)保存到CAT24WC02串行芯片中以防止掉電丟失,在下次啟動首先從CAT24WC02芯片中讀取數(shù)據(jù)保存到對應(yīng)數(shù)據(jù)緩沖區(qū)中。運行主程序是首先讀取時鐘芯片時間數(shù)據(jù)并在數(shù)碼管顯示相關(guān)信息,隨后將當(dāng)前時間與各打鈴時間點相比較看是否需要打鈴,最后進行鍵盤信息處理,分別完成時間設(shè)定和打鈴時間點設(shè)定等相關(guān)操作,具體流程如圖4所示。

圖4 主程序流程圖

鬧鈴時間設(shè)置程序設(shè)計

本設(shè)計中共采用8個按鍵,其中時間設(shè)置按鍵和鬧鈴設(shè)置按鍵為復(fù)用鍵,由圖4可知當(dāng)運行主程序時,按下相應(yīng)鍵則程序進入時間設(shè)置或鬧鈴時間設(shè)置程序處理中,在鬧鈴時間設(shè)置程序中,此二鍵亦分別用于添加鬧鈴和刪除鬧鈴設(shè)置,當(dāng)6位數(shù)碼管顯示信息均處于閃爍狀態(tài)時,此時按下添加鍵,則表示新添加一鬧鈴時間點,按下刪除鍵則表示刪除對應(yīng)鬧鈴時間點,如6位數(shù)碼管顯示信息不全閃爍,則此二鍵不起作用。左移和右移按鍵則分別用來選擇所要設(shè)置數(shù)據(jù)位(時或分),選擇對應(yīng)位后相應(yīng)數(shù)據(jù)進入閃爍狀態(tài),此時操作增加或減小鍵進入相應(yīng)數(shù)值設(shè)置,當(dāng)僅鬧鈴時間序號閃爍時,增加和減小鍵同時有依次進行查詢所有鬧鈴時間點的功能。信息設(shè)置完后當(dāng)按下確認(rèn)鍵則表示信息設(shè)置完成,此時所設(shè)置鬧鈴信息會統(tǒng)一進行從小到大排序(用于查詢時從小到大顯示),然后分別保存到單片機相應(yīng)內(nèi)存和CAT24WC02串行EEPROM中以防掉電丟失。如按下取消鍵,則表示放棄所設(shè)置信息,此時重新從CAT24WC02串行EEPROM中讀取原鬧鈴時間信息到單片機相應(yīng)內(nèi)存相應(yīng)緩沖區(qū)。具體流程圖如圖5所示。

圖5 主程序流程圖

鬧鈴時間信息顯示程序則由顯示程序void Display專門負(fù)責(zé),鬧鈴設(shè)置時的數(shù)據(jù)分別放在臨時顯示緩沖區(qū),結(jié)合其閃爍狀態(tài)值一起傳遞給顯示程序進一步處理,從而決定哪位數(shù)碼管顯示信息進行閃爍,閃爍狀態(tài)值FlagBit共有5個取值參數(shù),分別為0、1、2、3、4,其中0表示不閃爍, 1表示鬧鈴時間分值閃爍,2表示鬧鈴時間時值閃爍,3表示鬧鈴時間序號閃爍,4表示全部顯示數(shù)值一起閃爍。具體閃爍控制則由定時中斷服務(wù)程序里對閃爍標(biāo)志不斷取反,顯示程序里根據(jù)此標(biāo)志位的變化進行閃爍控制。

時間設(shè)置處理程序則主要是通過按鍵設(shè)置好時間后對DS1302進行數(shù)據(jù)更新, 具體過程與鬧鈴設(shè)置程序類似,篇幅原因不在多述。

結(jié)語

實驗初期本設(shè)計主要通過仿真軟件完成,由于受實驗條件影響,數(shù)碼管顯示部分采用靜態(tài)顯示方法完成,如考慮節(jié)約成本,在實際電路中本設(shè)計亦可采用動態(tài)顯示電路或串行顯示電路完成。