在過(guò)去幾年中,視頻監(jiān)控錄像設(shè)備的性能得到了極大提升。借助新的硅器件產(chǎn)品,監(jiān)控 DVR 設(shè)計(jì)人員可以創(chuàng)建全幀速率的多通道捕捉、壓縮和回放系統(tǒng),支持高質(zhì)量和高分辨率視頻,且價(jià)格合理。監(jiān)控 DVR 系統(tǒng)質(zhì)量和性能的進(jìn)步,主要取決于兩個(gè)關(guān)鍵因素:

1)采用高分辨率模數(shù)轉(zhuǎn)換和先進(jìn)亮度/色度分離技術(shù)的多通道視頻解碼器,可將質(zhì)量及信噪比(SNR)最大化;

2)支持 H.264 及其他先進(jìn)壓縮技術(shù)的視頻編解碼器SoC,可最大限度降低比特率,實(shí)現(xiàn)HDD 存儲(chǔ)容量的最大化。

當(dāng)然,還有許多其他的技術(shù)因素,如不斷進(jìn)步的處理器、網(wǎng)絡(luò)和存儲(chǔ)器等,都在不斷改善著監(jiān)控DVR 的品質(zhì)。盡管如此,這些技術(shù)也得益于其它技術(shù)市場(chǎng)的推動(dòng)。下面,我們將介紹主要面向視頻監(jiān)控應(yīng)用進(jìn)行開(kāi)發(fā)的多通道視頻解碼器和編解碼器。

視頻監(jiān)控DVR的架構(gòu)大有不同,這主要取決于終端用戶的要求。通常,監(jiān)控DVR接受來(lái)自多個(gè)模擬相機(jī)的輸入,并將視頻數(shù)字化;然后,將原始數(shù)字視頻傳送到編解碼器進(jìn)行壓縮(在一些基于 PC的架構(gòu)中,壓縮用軟件執(zhí)行,但是大多數(shù) DVR采用硬件編解碼器)。

大多數(shù)DVR還提供“預(yù)覽”或“實(shí)時(shí)顯示”模式,允許在相機(jī)上實(shí)時(shí)觀看現(xiàn)場(chǎng)事件,是“數(shù)字視頻錄像機(jī)”的“錄像機(jī)”部分,意味著該器件需要壓縮和存儲(chǔ)視頻。反過(guò)來(lái),這意味著DVR系統(tǒng)必須能夠?qū)囊曨l解碼器中獲得的未壓縮視頻傳送到編解碼器進(jìn)行壓縮。這看起來(lái)非常簡(jiǎn)單,但實(shí)際上,當(dāng)視頻解碼器的輸出不兼容,或輸出不是編解碼器輸入的最理想模式時(shí),就會(huì)產(chǎn)生嚴(yán)峻挑戰(zhàn)。ITU-R BT.656是一個(gè)未壓縮數(shù)字視頻的正式標(biāo)準(zhǔn),但為了節(jié)省引腳和印制線,許多編解碼器都要求具有多個(gè)視頻流交錯(cuò)在一起的超頻 BT.656。盡管提出了詳細(xì)的分辨率和計(jì)時(shí)要求,但是交錯(cuò)基本方法并非標(biāo)準(zhǔn)。

因?yàn)?I/O 引腳數(shù)的限制,許多編解碼器都要求字節(jié)交錯(cuò)數(shù)據(jù),這樣2或4個(gè)數(shù)字視頻流就可以與來(lái)自每個(gè)視頻流的交替數(shù)據(jù)字節(jié)進(jìn)行多路傳輸。有些編解碼器可以接受線交錯(cuò)數(shù)據(jù),在這些器件中,所有視頻流組成的一個(gè)完整視頻隊(duì)列在下一次視頻流隊(duì)列之前被送出,如此反復(fù)。為了進(jìn)一步挑戰(zhàn)監(jiān)控 DVR 系統(tǒng)設(shè)計(jì)人員,大多數(shù)編解碼器都要求幀交錯(cuò)視頻數(shù)據(jù),而來(lái)自各個(gè)源的整個(gè)幀都是按順序輸入的,以實(shí)現(xiàn)其最高工作效率。即使在字節(jié)或線交錯(cuò)數(shù)據(jù)發(fā)送到編解碼器的情況下,無(wú)論如何也必須將數(shù)據(jù)解復(fù)用成幀,用于每個(gè)源。在輸入引腳上直接接收幀交錯(cuò)視頻數(shù)據(jù),可以降低這種難度,對(duì)于編解碼器來(lái)說(shuō)是處理器密集型應(yīng)用。

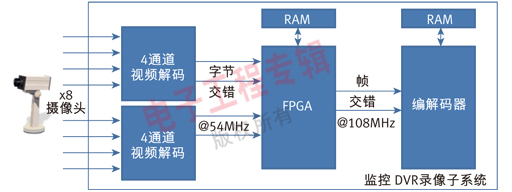

因?yàn)榫幗獯a器通常是監(jiān)控 DVR 中所使用的最昂貴、最復(fù)雜的硅器件(不包括用于基于PC 的DVR的微處理器),大多數(shù)系統(tǒng)設(shè)計(jì)人員都希望編解碼器以最高效率運(yùn)行,所以許多設(shè)計(jì)人員采用外部邏輯來(lái)生成幀交錯(cuò)數(shù)據(jù)以發(fā)送到編解碼器。圖1顯示了采用FPGA的監(jiān)控 DVR錄像子系統(tǒng),執(zhí)行從視頻解碼器54MHz字節(jié)交錯(cuò)數(shù)據(jù)到編解碼器108MHz幀交錯(cuò)數(shù)據(jù)的轉(zhuǎn)換。

圖 1:使用FPGA進(jìn)行未壓縮視頻格式轉(zhuǎn)換的子系統(tǒng)

因?yàn)榇蠖鄶?shù)多通道視頻解碼器不支持幀交錯(cuò)數(shù)據(jù)格式,而這種格式恰恰對(duì)于編解碼器是最佳的,或是在某些情況下是必須的,因此需要用FPGA來(lái)轉(zhuǎn)換數(shù)據(jù)。這是個(gè)令人滿意的解決方案,但是FPGA 增加了設(shè)計(jì)的成本和復(fù)雜性。如果視頻解碼器可提供幀交錯(cuò)數(shù)據(jù),F(xiàn)PGA就可以完全從子系統(tǒng)中移除。

為了應(yīng)對(duì)這個(gè)挑戰(zhàn)并降低集成成本,科勝迅系統(tǒng)公司新近推出8通道視頻解碼器CX25838和CX25858,可提供幀交錯(cuò)輸出并與監(jiān)控DVR中普遍使用的編解碼器兼容。圖2顯示了當(dāng)帶有幀交錯(cuò)輸出的CX25838 發(fā)送到圖1所示子系統(tǒng)時(shí),子系統(tǒng)結(jié)構(gòu)圖是如何改變的。

圖 2:帶幀交錯(cuò)輸出的基于 8 通道視頻解碼器的子系統(tǒng)

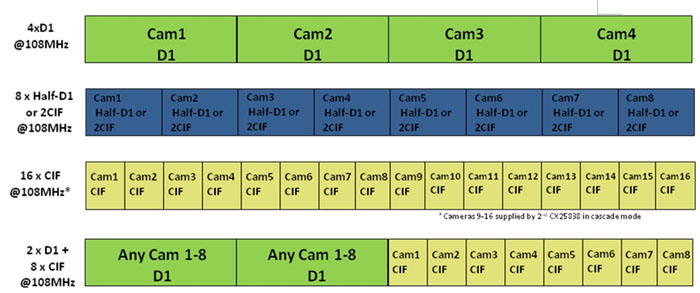

8 通道架構(gòu)和幀交錯(cuò)輸出可幫助錄像子系統(tǒng)實(shí)現(xiàn)可能最高水平的集成,由于不再需要FPGA和 4通道解碼器,所以可以將元件數(shù)量減少到2個(gè)。這不僅節(jié)省了成本,還節(jié)省了寶貴的板上空間。那么,該產(chǎn)品的靈活性怎樣呢?雖然FPGA和可編程邏輯為定制化提供了最廣泛的選擇,但是CX25838也非常靈活。為了處理各種系統(tǒng)要求,CX25838 能夠輸出各種分辨率和幀速率。CX25838上有4條專(zhuān)用8位視頻I/O總線。圖3說(shuō)明了CX25838 的一條8位視頻輸出總線上的幀交錯(cuò)數(shù)據(jù)格式的例子。

CX25838為監(jiān)控DVR設(shè)計(jì)人員提供機(jī)會(huì),通過(guò)提供幀交錯(cuò)數(shù)據(jù)實(shí)現(xiàn)編解碼器效率最大化,而不采用昂貴的FPGA或可編程邏輯。它還通過(guò)提供各種分辨率和幀速率,在一系列產(chǎn)品中共享系統(tǒng)架構(gòu),提供規(guī)模優(yōu)勢(shì)的能力。例如,低成本DVR可采用一個(gè)編解碼器以全幀速率壓縮16個(gè)CIF分辨率通道,這可通過(guò)一條8位總線實(shí)現(xiàn)。其他解決方案可能需要每個(gè)編解碼器以全幀速率壓縮4個(gè)D1分辨率通道。還有些可能需要降低幀速率的D1 分辨率(在圖3中并未體現(xiàn),但是在CX25838上可以實(shí)現(xiàn))。

圖3 :來(lái)自 CX25838 的字節(jié)寬總線幀交錯(cuò)輸出

具有幀交錯(cuò)輸出的解碼器可實(shí)現(xiàn)與編解碼器的直接連接,并為系統(tǒng)設(shè)計(jì)人員提供很大的靈活性,從而實(shí)現(xiàn)設(shè)計(jì)的差異化和規(guī)模化。隨著視頻DVR繼續(xù)增加各種特性和功能,具有幀交錯(cuò)輸出的視頻解碼器,代表了向增加監(jiān)控DVR系統(tǒng)效率和降低系統(tǒng)成本邁進(jìn)的關(guān)鍵一步。