一,、引言

隨著PCB設(shè)計(jì)復(fù)雜度的逐步提高,,對于信號完整性的分析除了反射,,串?dāng)_以及EMI之外,,穩(wěn)定可靠的電源供應(yīng)也成為設(shè)計(jì)者們重點(diǎn)研究的方向之一,。尤其當(dāng)開關(guān)器件數(shù)目不斷增加,,核心電壓不斷減小的時(shí)候,電源的波動(dòng)往往會給系統(tǒng)帶來致命的影響,,于是人們提出了新的名詞:電源完整性" title="電源完整性">電源完整性,,簡稱PI(powerintegrity)。當(dāng)今國際市場上,,IC設(shè)計(jì)比較發(fā)達(dá),,但電源完整性設(shè)計(jì)還是一個(gè)薄弱的環(huán)節(jié)。因此本文提出了PCB板中電源完整性問題的產(chǎn)生,,分析了影響電源完整性的因素并提出了解決PCB板中電源完整性問題的優(yōu)化方法與經(jīng)驗(yàn)設(shè)計(jì),,具有較強(qiáng)的理論分析與實(shí)際工程應(yīng)用價(jià)值。

二,、電源噪聲" title="電源噪聲">電源噪聲的起因及分析

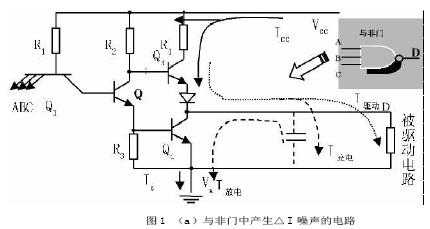

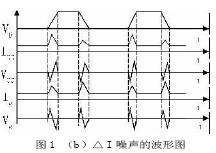

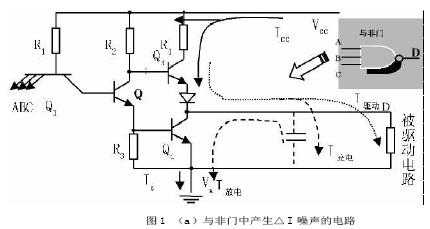

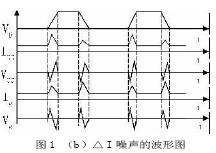

對于電源噪聲的起因我們通過一個(gè)與非門電路圖進(jìn)行分析,。圖1中的電路圖為一個(gè)三輸入與非門的結(jié)構(gòu)圖,因?yàn)榕c非門屬于數(shù)字器件,,它是通過“1”和“0”電平的切換來工作的,。隨著IC技術(shù)的不斷提高,數(shù)字器件的切換速度也越來越快,,這就引進(jìn)了更多的高頻分量,,同時(shí)回路中的電感在高頻下就很容易引起電源波動(dòng)。如在圖1中,,當(dāng)與非門輸入全為高電平時(shí),,電路中的三極管導(dǎo)通,電路瞬間短路,,電源向電容充電,,同時(shí)流入地線,。此時(shí)由于電源線和地線上存在寄生電感,我們由公式V=LdI/dt可知,,這將在電源線和地線上產(chǎn)生電壓波動(dòng),,如圖2中所示的電平上升沿所引入的ΔI噪聲。當(dāng)與非門輸入為低電平時(shí),,此時(shí)電容放電,,將在地線上產(chǎn)生較大的ΔI噪聲;而電源此時(shí)只有電路的瞬間短路所引起的電流突變,由于不存在向電容充電而使電流突變相對于上升沿來說要小,。從對與非門的電路進(jìn)行分析我們知道,,造成電源不穩(wěn)定的根源主要在于兩個(gè)方面:一是器件高速開關(guān)狀態(tài)下,瞬態(tài)的交變電流過大;

二是電流回路上存在的電感,。所謂地電源完整性問題是指在高速PCB" title="高速PCB">高速PCB中,當(dāng)大量的芯片同時(shí)開啟或關(guān)閉時(shí),,在電路中就會產(chǎn)生較大的瞬態(tài)電流,,同時(shí)由于電源線和地線上電感電阻的存在,就會在兩者之上產(chǎn)生電壓波動(dòng),。了解到電源完整性問題的本質(zhì),,我們知道,要解決電源完整性問題,,首先對于高速器件來說,,我們通過加去耦電容來去掉它的高頻噪聲分量,這樣就減少信號的瞬變時(shí)間;對于回路中所存在的電感來說,,我們則要從電源的分層設(shè)計(jì)來考慮,。

三、去耦電容的應(yīng)用

在高速PCB設(shè)計(jì)中,,去耦電容起著重要的作用,,它的放置位置也很重要。這是因?yàn)樵陔娫聪蜇?fù)載短時(shí)間供電中,,電容中的存儲電荷可防止電壓下降,,如電容放置位置不恰當(dāng)可使線阻抗過大,影響供電,。同時(shí)電容在器件的高速切換時(shí)可濾除高頻噪聲,。我們在高速PCB設(shè)計(jì)中,一般在電源的輸出端和芯片的電源輸入端各加一個(gè)去耦電容,,其中靠近電源端的電容值一般較大(如10μF),,這是因?yàn)镻CB中我們一般用的是直流電源,為了濾除電源噪聲電容的諧振頻率可以相對較低;同時(shí)大電容可以確保電源輸出的穩(wěn)定性,。對于芯片接電源的引腳處所加的去耦電容來說,,其電容值一般較?。ㄈ?.1μF),這是因?yàn)樵诟咚傩酒?,噪聲頻率一般都比較高,,這就要求所加去耦電容的諧振頻率要高,即去耦電容的容值要小,。

對于去耦電容的放置,,我們知道,如果位置不當(dāng)?shù)脑挄龃缶€路阻抗,,降低其諧振頻率同時(shí)影響供電,。對于去耦電容和芯片或電源中的電感,我們可以通過公式: 求出,,在公式中,,l:電容與芯片間的線長;r:線半徑;d:電源線與地之間的距離;

求出,,在公式中,,l:電容與芯片間的線長;r:線半徑;d:電源線與地之間的距離;

由此我們知道,要減少電感L,,則必須減少l和d,,即減少去耦電容和芯片所形成的環(huán)路面積,也就是要求電容與芯片盡可能靠近芯片器件,。

一,、引言

隨著PCB設(shè)計(jì)復(fù)雜度的逐步提高,對于信號完整性的分析除了反射,,串?dāng)_以及EMI之外,,穩(wěn)定可靠的電源供應(yīng)也成為設(shè)計(jì)者們重點(diǎn)研究的方向之一。尤其當(dāng)開關(guān)器件數(shù)目不斷增加,,核心電壓不斷減小的時(shí)候,,電源的波動(dòng)往往會給系統(tǒng)帶來致命的影響,于是人們提出了新的名詞:電源完整性,,簡稱PI(powerintegrity),。當(dāng)今國際市場上,IC設(shè)計(jì)比較發(fā)達(dá),,但電源完整性設(shè)計(jì)還是一個(gè)薄弱的環(huán)節(jié),。因此本文提出了PCB板中電源完整性問題的產(chǎn)生,分析了影響電源完整性的因素并提出了解決PCB板中電源完整性問題的優(yōu)化方法與經(jīng)驗(yàn)設(shè)計(jì),,具有較強(qiáng)的理論分析與實(shí)際工程應(yīng)用價(jià)值,。

二、電源噪聲的起因及分析

對于電源噪聲的起因我們通過一個(gè)與非門電路圖進(jìn)行分析,。圖1中的電路圖為一個(gè)三輸入與非門的結(jié)構(gòu)圖,,因?yàn)榕c非門屬于數(shù)字器件,它是通過“1”和“0”電平的切換來工作的,。隨著IC技術(shù)的不斷提高,,數(shù)字器件的切換速度也越來越快,,這就引進(jìn)了更多的高頻分量,同時(shí)回路中的電感在高頻下就很容易引起電源波動(dòng),。如在圖1中,,當(dāng)與非門輸入全為高電平時(shí),電路中的三極管導(dǎo)通,,電路瞬間短路,,電源向電容充電,同時(shí)流入地線,。此時(shí)由于電源線和地線上存在寄生電感,,我們由公式V=LdI/dt可知,這將在電源線和地線上產(chǎn)生電壓波動(dòng),,如圖2中所示的電平上升沿所引入的ΔI噪聲,。當(dāng)與非門輸入為低電平時(shí),此時(shí)電容放電,,將在地線上產(chǎn)生較大的ΔI噪聲;而電源此時(shí)只有電路的瞬間短路所引起的電流突變,,由于不存在向電容充電而使電流突變相對于上升沿來說要小。從對與非門的電路進(jìn)行分析我們知道,,造成電源不穩(wěn)定的根源主要在于兩個(gè)方面:一是器件高速開關(guān)狀態(tài)下,瞬態(tài)的交變電流過大;

二是電流回路上存在的電感,。所謂地電源完整性問題是指在高速PCB中,,當(dāng)大量的芯片同時(shí)開啟或關(guān)閉時(shí),在電路中就會產(chǎn)生較大的瞬態(tài)電流,,同時(shí)由于電源線和地線上電感電阻的存在,,就會在兩者之上產(chǎn)生電壓波動(dòng)。了解到電源完整性問題的本質(zhì),,我們知道,,要解決電源完整性問題,首先對于高速器件來說,,我們通過加去耦電容來去掉它的高頻噪聲分量,,這樣就減少信號的瞬變時(shí)間;對于回路中所存在的電感來說,我們則要從電源的分層設(shè)計(jì)來考慮,。

三,、去耦電容的應(yīng)用

在高速PCB設(shè)計(jì)中,去耦電容起著重要的作用,,它的放置位置也很重要,。這是因?yàn)樵陔娫聪蜇?fù)載短時(shí)間供電中,電容中的存儲電荷可防止電壓下降,,如電容放置位置不恰當(dāng)可使線阻抗過大,,影響供電,。同時(shí)電容在器件的高速切換時(shí)可濾除高頻噪聲。我們在高速PCB設(shè)計(jì)中,,一般在電源的輸出端和芯片的電源輸入端各加一個(gè)去耦電容,,其中靠近電源端的電容值一般較大(如10μF),這是因?yàn)镻CB中我們一般用的是直流電源,,為了濾除電源噪聲電容的諧振頻率可以相對較低;同時(shí)大電容可以確保電源輸出的穩(wěn)定性,。對于芯片接電源的引腳處所加的去耦電容來說,其電容值一般較?。ㄈ?.1μF),,這是因?yàn)樵诟咚傩酒校肼曨l率一般都比較高,,這就要求所加去耦電容的諧振頻率要高,,即去耦電容的容值要小。

對于去耦電容的放置,,我們知道,,如果位置不當(dāng)?shù)脑挄龃缶€路阻抗,降低其諧振頻率同時(shí)影響供電,。對于去耦電容和芯片或電源中的電感,,我們可以通過公式: 求出,在公式中,,l:電容與芯片間的線長;r:線半徑;d:電源線與地之間的距離;

求出,在公式中,,l:電容與芯片間的線長;r:線半徑;d:電源線與地之間的距離;

由此我們知道,,要減少電感L,則必須減少l和d,,即減少去耦電容和芯片所形成的環(huán)路面積,,也就是要求電容與芯片盡可能靠近芯片器件。

四,、電源回路的設(shè)計(jì)

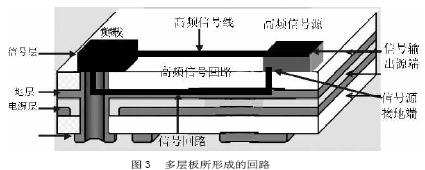

要保證電源完整性,,我們知道,良好的電源分配網(wǎng)絡(luò)是必不可少的,。首先對電源線和地線的設(shè)計(jì),,我們要保證線寬加粗(如寬為40mil,而普通信號線為10mil),,這樣才能盡可能地減少其阻抗值,。隨著芯片的速度越來越高,根據(jù)5/5規(guī)則,,我們越來越多地使用多層板,,通過專用的電源層進(jìn)行供電和專用的地層構(gòu)成回路,這樣就減少了線路的電感,。

圖4中所示的是一個(gè)四層板的信號回路圖,,高頻信號將從地層返回,,在地層理想的情況下(沒有分隔和過多的過孔),高頻信號線將在地層上形成射頻的鏡像回路,,返回電流將主要從高頻信號在地層上的鏡像路徑返回,,而在PCB中,信號線與地層之間的距離非常?。ù蠹s是0.3mm),,這樣就形成了小環(huán)路,不僅可以減少電源完整性的問題,,也能夠減少環(huán)路的射頻輻射,,避免引起其它的電磁兼容性問題。但在當(dāng)今高集成度的PCB設(shè)計(jì)中,,由于芯片集成度過高,,過孔過密,多電源供電及數(shù)字器件及模擬器件共存所引起的電源層和地層的分隔等因素,,要保證電源回路的暢通無阻則是很難的,。

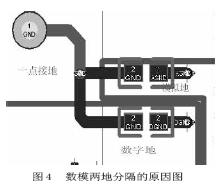

如在圖4中所示,在數(shù)字器件和模擬器件共存的高速PCB中,,為了防止數(shù)字器件所帶來的高頻噪聲對模擬器件造成影響,,我們把數(shù)字地和模擬地進(jìn)行了分隔,分立的數(shù)字地和模擬地用0歐電阻通過一點(diǎn)接地最后與電源地相連形成回路,。這樣就把數(shù)模兩部分噪聲進(jìn)行了隔離,,但同時(shí)也引進(jìn)了問題,由于地層的分隔破壞了地層的連續(xù)性,,阻礙了信號的小環(huán)路回路,這就使信號回路阻抗增大,,增加了出現(xiàn)電源完整性問題的可能,,同時(shí)大回路的返回路徑也增大了回路的射頻輻射和板間的電磁兼容性。為了避免以上的問題,,在數(shù)字器件和模擬器件混合布局中我們提倡采用統(tǒng)一地,,就是將數(shù)字器件和模擬器件分區(qū)布局,而地則不進(jìn)行分隔,。合理地對數(shù)模器件進(jìn)行布局,,通過基爾霍夫定律我們知,高頻下電路地返回路徑將沿著最小阻抗,,即最小的環(huán)路面積返回,,數(shù)字器件和模擬器件的返回路徑也將分別在數(shù)字器件和模擬器件所對應(yīng)的鏡像路徑返回,它們之間不會引起干擾,。

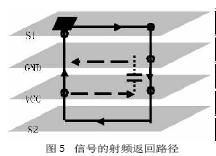

對于高集成度的PCB設(shè)計(jì)中,,由于信號線的走線可能比較復(fù)雜,,形成的回路面積可能比較大。如圖5,,在四層板中,,某信號源的信線在頂層經(jīng)過地層和電源層后從地層傳輸,最后返回,。在這個(gè)傳輸路徑中,,高頻信號線所形成的信號回路非常大。為了解決這個(gè)問題,,我們在靠近信號線的附近,,在電源層和地層之間加了一個(gè)電容。這樣,,對于高頻信號來說,,頂層的信號線在地層上將會產(chǎn)生一個(gè)鏡像回路,而地層的信號線將在電源層上產(chǎn)生一條鏡像回路,,這兩條鏡像回路將與電源層和地層之間的電容構(gòu)成回路,,這樣我們就盡可能地利用電源層和地層作為回路,減少了返回環(huán)路面積,,從而減少了產(chǎn)生電源完整性及板間電磁兼容問題地可能性,。

五、結(jié)束語

現(xiàn)今高速數(shù)字電路的設(shè)計(jì)趨向于復(fù)雜,,多電源的應(yīng)用,、電源電平的降低、芯片的高反應(yīng)速度和高敏感度以及PCB的高集成度所帶來的設(shè)計(jì)影響,,板內(nèi)的電源完整性問題也越來越嚴(yán)重且受到廣泛的重視,。因此本文通過對電源完整性問題的分析提出了其產(chǎn)生因素,并就電源完整性提出了一些設(shè)計(jì)方法,,這對于優(yōu)化PCB的EMC設(shè)計(jì)具有一定的價(jià)值,。