隨著半導(dǎo)體工藝技術(shù)向著納米尺度的發(fā)展,微電子技術(shù)進(jìn)入SoC(系統(tǒng)芯片)時(shí)代,且沿著可靠性強(qiáng)、體積小、功耗低等方向繼續(xù)發(fā)展。在下一代SoC設(shè)計(jì)流程中,系統(tǒng)級EDA工具的地位變得比以往更加重要,ESL(Electronic System Level)設(shè)計(jì)方法學(xué)將是設(shè)計(jì)下一代SoC的關(guān)鍵,因?yàn)橹饾u縮短的上市時(shí)間需要硬件-軟件并行設(shè)計(jì)。

本文以Tensilica Xtensa可配置、可擴(kuò)展處理器為開發(fā)平臺,探索了高性能低功耗ASIP(Application Specific Instruction-set Processor專用指令處理器)開發(fā)流程。

ASIP設(shè)計(jì)理論

面向特定應(yīng)用的ASIP處理器,既有ASIC執(zhí)行特定應(yīng)用的高效性,又有GPP處理器可編程的靈活性,能夠簡化設(shè)計(jì)復(fù)雜度、縮短設(shè)計(jì)周期、加快上市步伐,在SoC設(shè)計(jì)中得到了廣泛的應(yīng)用。如何快速高效地定制ASIP,使其滿足運(yùn)算性能、芯片面積、上市時(shí)間和功耗等要求,是一個(gè)極具挑戰(zhàn)性的問題。設(shè)計(jì)者需要在ASIP指令集設(shè)計(jì)過程中在廣泛的設(shè)計(jì)空間進(jìn)行指令集探索,尋找滿足設(shè)計(jì)約束的處理器體系結(jié)構(gòu)[1-8]。因此迫切需要可以支持快速ASIP設(shè)計(jì)的行為級設(shè)計(jì)方法和合適的EDA工具。

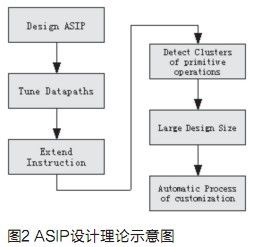

現(xiàn)在設(shè)計(jì)可編程處理器,很少是全新定制指令,普遍采用的方式是在已有的某RISC指令集基礎(chǔ)上進(jìn)行部分定制(或說擴(kuò)展/自定義/優(yōu)化指令)。理論上,為了研發(fā)一款A(yù)SIP式處理器,需要在已有GPP、ASIP、ASIC的基礎(chǔ)上調(diào)整數(shù)據(jù)通路(Datapath),即增加功能單元,如圖1所示的5級Pipeline處理器中添加自定義功能單元(Custom Unit),同時(shí)需要專用指令將操作數(shù)調(diào)入此自定義單元進(jìn)行數(shù)據(jù)處理。為了實(shí)現(xiàn)指令擴(kuò)展,首先需要分析應(yīng)用目標(biāo)數(shù)據(jù)處理算法的特性,從中找出那些經(jīng)常出現(xiàn)且可以綁定的基本操作包;然后從眾多實(shí)現(xiàn)方式(或大設(shè)計(jì)空間)如:(1)FLIX(VLIW或Multi-slot);(2)Vector(SIMD);(3)FUSED(Add-with-Shift-by-1)中選擇最合適的途徑[9-10]。因?yàn)樵O(shè)計(jì)者很難一次性找到最優(yōu)途徑,常常需要不同方式之間進(jìn)行比較,因此一般需要某些EDA工具幫助快速實(shí)現(xiàn)指令自定義以及分析當(dāng)前自定義指令對ASIP性能的影響。圖2采用Top-down方式示意出ASIP設(shè)計(jì)的理論步驟。

Xtensa開發(fā)工具集

目前,可用于ASIP體系結(jié)構(gòu)及指令系統(tǒng)開發(fā)的EDA工具,包括Tensilica的Xtensa開發(fā)工具集(Xplorer、XCC、XPRES、XTMS、XEnergy),CoWare的Processor Design,University of Campinas的ArchC等。但Tensilica 的Xtensa開發(fā)工具集因功能強(qiáng)大而得到廣泛應(yīng)用。

Tensilica針對SoC應(yīng)用而設(shè)計(jì)的Xtensa系列可配置處理器及其開發(fā)工具,提供了一種自動(dòng)化程度非常高的開發(fā)流程,該流程包括仿真C/SystemC級算法、調(diào)整處理器體系結(jié)構(gòu)、向基本處理器添加專用指令、自動(dòng)生成硬件RTL代碼和與之相匹配的軟件工具鏈(如編譯器等),通過可配置處理器技術(shù)和TIE(Tensilica Instruction Extension)指令擴(kuò)展技術(shù)替代了RTL開發(fā)。和ASIP相關(guān)的具體功能如下。

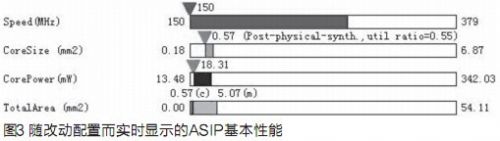

(1) 對處理器的體系結(jié)構(gòu)進(jìn)行配置的同時(shí),設(shè)計(jì)者可以在Xplorer中實(shí)時(shí)看到每一次調(diào)整對ASIP性能產(chǎn)生的影響,如圖3。

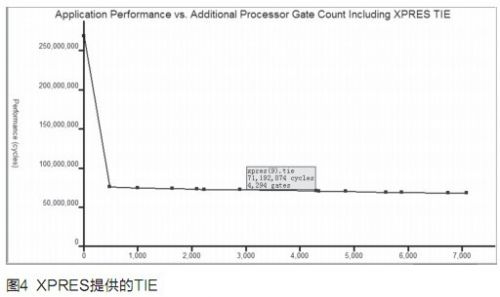

(2) XPRES工具可以完全自動(dòng)地分析應(yīng)用程序生成相應(yīng)的指令擴(kuò)展。設(shè)計(jì)人員只需輸人利用標(biāo)準(zhǔn)ANSI C/C++設(shè)計(jì)的原始算法,XPRES便可以根據(jù)內(nèi)置的配置選項(xiàng)完全自動(dòng)化地產(chǎn)生多種TIE指令組合供設(shè)計(jì)者折中選擇。

(3) 使用自定義的FLIX指令,它包括七種不同的64位指令字格式以及高達(dá)8個(gè)并行操作指令槽。FLIX提供VLIW風(fēng)格的并行執(zhí)行功能卻沒有VLIW處理器會發(fā)生的“代碼膨脹”現(xiàn)象。

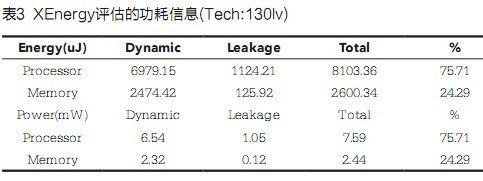

(4) XEnergy可以根據(jù)最終的體系結(jié)構(gòu)配置和指令系統(tǒng)(包括設(shè)計(jì)者自定義的TIE擴(kuò)展指令)評估ASIP功耗指標(biāo)。

基于Xtensa開發(fā)工具的ASIP設(shè)計(jì)流程

本項(xiàng)目目標(biāo)是設(shè)計(jì)一款實(shí)現(xiàn)低功耗無損壓縮的嵌入式ASIP。首先,經(jīng)過比較從眾多壓縮算法中選擇了簡單高效的FELICS算法[11];然后開發(fā)算法的C++代碼進(jìn)行實(shí)際圖像壓縮實(shí)驗(yàn)。試驗(yàn)結(jié)果:FELICS對12幅目標(biāo)圖像的平均無損壓縮比為2.7:1,滿足本項(xiàng)目要求。之后的工作就是根據(jù)圖2流程實(shí)現(xiàn)針對FELICS算法的ASIP設(shè)計(jì)。

(1)將C++代碼輸入Tensilica Xplorer開發(fā)環(huán)境,選擇系統(tǒng)自帶的sample_config-params (RB-2006.0)配置信息作為ASIP開發(fā)的起點(diǎn),即在此基礎(chǔ)上進(jìn)行體系結(jié)構(gòu)的調(diào)整和指令的自定義開發(fā)。

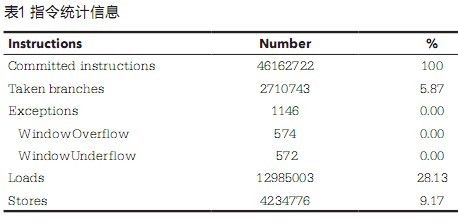

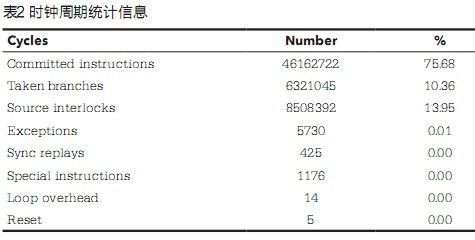

(2) 運(yùn)行代碼并進(jìn)行特性分析(Profile),表1和表2是最基本的指令和時(shí)鐘周期信息,此外還可以得到pipeline甘特圖、Branch cycle和Interlock cycle對比圖等信息。這些信息為后續(xù)的體系結(jié)構(gòu)調(diào)整和指令優(yōu)化提供了必要的數(shù)據(jù)依據(jù)。

(3) 調(diào)整處理器配置信息中的眾多項(xiàng)目,如MUL16 / MUL32 / MAC、Zero-overhead loop instructions、Pipeline length、Number of coprocessors、Floating point coprocessor、Special register、Cache size等,設(shè)計(jì)者可以得到圖3所示的速度、面積、功耗信息。然后回到(2)再次運(yùn)行代碼及特性分析,考察體系結(jié)構(gòu)改動(dòng)帶來的影響。

(4)利用XPRES工具,設(shè)置FLIX的Issue Width、SIMD的Vector Length、Register的Depth / Width / Ports、Fusion的Area / Latency / Operands等,XPRES會自動(dòng)生成若干種不同的自定義指令TIE供設(shè)計(jì)者選擇使用。設(shè)計(jì)者參考每一個(gè)TIE的Cycles和Gates數(shù)折衷考慮,當(dāng)然設(shè)計(jì)者還可以手動(dòng)增加TIE指令。然后將TIE綁定到調(diào)整后的體系結(jié)構(gòu)(配置信息)上,回到(2)運(yùn)行代碼及特性分析,考察TIE帶來的性能提高效果。

(5) 運(yùn)行XEnergy命令工具,對以上步驟生成的ASIP進(jìn)行全面功耗評估,如表3所示。

(6)經(jīng)過(2)到(5)多次反復(fù)調(diào)試,在Xtensa高效的開發(fā)工具下,用戶很快會得到滿意的ASIP體系結(jié)構(gòu)及指令系統(tǒng)。然后,將配置信息和TIE指令信息提交給Tensilica的服務(wù)器,Xtensa Porcessor Generator(XPG)會生成相應(yīng)的RTL或Netlist,供用戶進(jìn)行后端實(shí)現(xiàn),同時(shí)XPG還會生成ASIP所需的軟件開發(fā)工具,如編譯器、匯編器,使設(shè)計(jì)人員省去了針對ASIP開發(fā)編譯器(或編譯器重定向)的繁重工作。

結(jié)語

Tensilica Xtensa體系結(jié)構(gòu)可配置、指令集可自定義處理器和Xplorer、XPRES、XEnergy等工具集大大提高了ASIP處理器開發(fā)速度,加快了針對不同應(yīng)用領(lǐng)域探索專用處理器設(shè)計(jì)空間的效率。本文重點(diǎn)敘述了借助Xtensa平臺開發(fā)ASIP時(shí)前端設(shè)計(jì)的各個(gè)步驟,此設(shè)計(jì)流程具有較強(qiáng)的借鑒價(jià)值。