一、前言:

集成電路產(chǎn)業(yè)是我國(guó)高新技術(shù)產(chǎn)業(yè)的一個(gè)重要部分,它帶動(dòng)了其它產(chǎn)業(yè)的蓬勃發(fā)展,集成電路已成為各個(gè)行業(yè)中電子、機(jī)電設(shè)備智能化的核心,起著十分重要的作用。

近年來越來越多的電路設(shè)計(jì)人員和應(yīng)用人員開展集成電路的EMC設(shè)計(jì)和測(cè)試方法的研究,EMC性已成為衡量集成電路性能的又一重要技術(shù)指標(biāo)。隨著集成電路集成度的提高,越來越多的元件集成到芯片上,電路的功能和密度增加了,傳輸脈沖電流的速度提高了,工作電壓降低了,集成電路本身的電磁騷擾與抗干擾問題已成為集成電路的設(shè)計(jì)、制造業(yè)關(guān)注的課題。集成電路EMC的研究不僅涉及集成電路自身的電磁騷擾與抗擾度測(cè)試和設(shè)計(jì)方法研究,而且有必要與集成電路的應(yīng)用相結(jié)合,將強(qiáng)制性標(biāo)準(zhǔn)對(duì)設(shè)備和系統(tǒng)的EMC要求,結(jié)合到集成電路的設(shè)計(jì)中,使電路更易于設(shè)計(jì)出符合標(biāo)準(zhǔn)的最終產(chǎn)品。電磁騷擾小的集成電路更有利于產(chǎn)品的EMC設(shè)計(jì),可以減少系統(tǒng)設(shè)計(jì)的負(fù)擔(dān),節(jié)約濾波、屏蔽等措施的費(fèi)用,因此開展集成電路的EMC設(shè)計(jì)和檢測(cè)研究能為電路的應(yīng)用提供設(shè)計(jì)指南,節(jié)約最終產(chǎn)品的成本。

集成電路的廣泛應(yīng)用,反過來對(duì)其又提出了更高的要求,人們需要性能更好、可靠性高、成本更低的集成電路。從20世紀(jì)60年代以來正如摩爾定律預(yù)計(jì)的那樣每隔18到 24個(gè)月芯片上的元件數(shù)翻了一番,出現(xiàn)了在芯片的價(jià)格持續(xù)降低的同時(shí),性能和可靠性不斷提高的行業(yè)特點(diǎn)。集成的元件數(shù)的提高可以通過減小芯片上的關(guān)鍵尺寸(CD)或最小化特征尺寸來實(shí)現(xiàn),這樣在集成度提高的同時(shí)芯片的速度也提高了。由于集成電路通過高速的脈沖數(shù)字信號(hào)來進(jìn)行工作,工作頻率越高產(chǎn)生的電磁騷擾頻譜越寬,越容易引起對(duì)外輻射的EMC方面的問題。

二、研究對(duì)象

在集成電路電磁騷擾研究檢測(cè)領(lǐng)域,通常將直接從芯片上的電路和集成電路封裝產(chǎn)生的電磁發(fā)射稱為輻射騷擾;將由集成電路引腳注入到印制電路板的布線或電纜上的脈沖電流引起的電磁發(fā)射稱為傳導(dǎo)騷擾1。一般芯片上的電路和集成電路封裝產(chǎn)生的直接輻射騷擾比由射頻電流通過外圍電路產(chǎn)生的電磁輻射小得多。從電磁發(fā)射的角度來看,電路板上布線與連接電纜構(gòu)成了電磁發(fā)射的天線。

由集成電路內(nèi)部產(chǎn)生的射頻電流,通過引腳和與之相連的PCB 板上的連線向外發(fā)射,引腳和連線形成了等效的發(fā)射天線,產(chǎn)生了無意發(fā)射。向外發(fā)射功率的大小可由式(1)來計(jì)算:

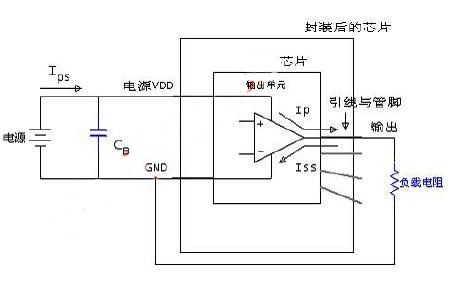

其中Rr為無意發(fā)射天線的等效發(fā)射阻抗,IRF為IC工作時(shí)產(chǎn)生的射頻電流。由此可以看出評(píng)價(jià)集成電路傳導(dǎo)騷擾可通過測(cè)量集成電路引腳的射頻電流來進(jìn)行。在數(shù)字集成電路中,該射頻電流是由電路芯片和驅(qū)動(dòng)電路產(chǎn)生的脈沖射頻電流。如圖(一)是集成電路的電流分布示意圖,ZL 為連接輸出端口外圍電路的等效阻抗,IP 為輸出電平由低電平到高電平時(shí)的輸出電流,ISS 為輸出電平由高電平到低電平時(shí)的輸出電流,ICC 為輸出級(jí)電路的供電電源的電流。當(dāng)電路工作時(shí),瞬時(shí)脈沖電流一部分從旁路電容CB得到,另一部分來自供電電源IPS。經(jīng)過旁路電容的電流大小與旁路電容相對(duì)于集成電路的放置位置、布線情況、電容的特性有關(guān),即與連接旁路電容的串聯(lián)阻抗、諧振頻率等電容本身的特性有關(guān)。通常旁路電容為高頻信號(hào)提供一個(gè)低阻抗回路,這樣電流的高頻部分由電容來提

供,其余由電源提供形成輸出電流。

圖(一)數(shù)字集成電路的芯片與I/O電路電流分布

可以看出,外圍電路的變化會(huì)對(duì)電流的分布情況產(chǎn)生影響,因而測(cè)試應(yīng)在專門設(shè)計(jì)的電路板上進(jìn)行。在確定的電路板上,集成電路的電磁發(fā)射的水平,可通過測(cè)出的電源端和輸出端口電流來描述。

三、集成電路電磁騷擾標(biāo)準(zhǔn)發(fā)展?fàn)顩r

目前國(guó)際電工委員會(huì)制定的有關(guān)集成電路電磁發(fā)射的標(biāo)準(zhǔn)如表(一)所示:

序號(hào)標(biāo)準(zhǔn)名稱

1 IEC61967-1 集成電路-電磁發(fā)射,150kHz to 1GHz-通用條件與定義

2 IEC61967-2 集成電路-電磁發(fā)射,150kHz to 1GHz-TEM 小室法

3 IEC TS61967-3 集成電路-電磁發(fā)射,150kHz to 1GHz-表面掃描法

4 IEC61967-4 集成電路-電磁發(fā)射,150kHz to 1GHz-1Ω/150Ω直接耦合法

5 IEC61967-5 集成電路-電磁發(fā)射,150kHz to 1GHz-工作臺(tái)法拉第籠法

6 IEC61967-6 集成電路-電磁發(fā)射,150kHz to 1GHz-磁場(chǎng)探頭法

下面簡(jiǎn)要介紹幾種電磁發(fā)射的測(cè)試方法。

1、TEM 小室法

TEM小室法是在電磁兼測(cè)試中應(yīng)用較為廣泛的TEM小室的基礎(chǔ)上建立起來的一種電磁騷擾測(cè)量方法。TEM 小室中間的矩形部分開了一個(gè)與被測(cè)線路板相適應(yīng)的矩形窗口,用于放置裝有被測(cè)集成電路的專用評(píng)估線路板,該P(yáng)CB 板的內(nèi)側(cè)為被測(cè)的集成電路,外側(cè)為集成電路的外圍電路及輔助設(shè)備的連接端子。如果TEM 小室工作頻率低于截止頻率,只有TEM 模被激發(fā),傳遞到兩同軸負(fù)載的功率與被測(cè)PCB 板上試品的電流平方成正比,這樣通過測(cè)試同軸輸出端的頻譜就能評(píng)估線路板上集成電路的電磁發(fā)射性能。該方法的缺點(diǎn)是必須制作專用的測(cè)試板用于測(cè)試,在電路電磁發(fā)射源多的情形下測(cè)試板對(duì)測(cè)試結(jié)果的影響比較大。

2、表面掃描法

表面掃描法通過測(cè)量集成電路表面電場(chǎng)和磁場(chǎng)的方法來描述集成電路的電磁發(fā)射特性。該方法的測(cè)量頻率范圍可達(dá)10MHz—3GHz,測(cè)量采用電場(chǎng)探頭或磁場(chǎng)探頭按一定順序掃過集成電路表面,由接收機(jī)將相應(yīng)的測(cè)量結(jié)果依次傳送給計(jì)算機(jī)處理。測(cè)試結(jié)果的準(zhǔn)確性與電場(chǎng)或磁場(chǎng)探頭的特性和探頭定位裝置的精度有關(guān)。該方法可用于探測(cè)集成電路芯片上不同部位的電磁發(fā)射分布情況,適用于對(duì)集成電路的不同設(shè)計(jì)方案的電磁發(fā)射特性的比較。

3、1Ω/150Ω直接耦合法

直接耦合法分為射頻電流測(cè)試和引腳的射頻電壓測(cè)試兩種測(cè)試方法。射頻電流測(cè)試法是在需進(jìn)行測(cè)試的電路中接入一串聯(lián)電阻為1Ω的電流探頭,用頻譜儀或接收機(jī)測(cè)量射頻電流流經(jīng)該電阻時(shí)產(chǎn)生的射頻電壓,所測(cè)得的電壓應(yīng)為所有流回到集成電路的射頻電流在電流探頭上產(chǎn)生電壓的總和。射頻電壓測(cè)試法用于測(cè)試集成電路的單個(gè)引腳或一組引腳上的射頻電壓,該方法主要用于測(cè)試那些準(zhǔn)備

連接較長(zhǎng)引線輸出高頻信號(hào)的引腳,因?yàn)檩^長(zhǎng)的引線更易成為發(fā)射電磁波的天線。集成電路的引腳通過標(biāo)準(zhǔn)規(guī)定的匹配網(wǎng)絡(luò)接到測(cè)試接收機(jī)。由于電流探頭和電壓探頭及網(wǎng)絡(luò)需設(shè)計(jì)在線路板上才能進(jìn)行測(cè)試,所以該方法需要設(shè)計(jì)專用的標(biāo)準(zhǔn)測(cè)試板來進(jìn)行。該方法的具有重復(fù)性高的優(yōu)點(diǎn),可用于比較不同集成電路的電磁發(fā)射特性。

4、工作臺(tái)法拉第籠法

工作臺(tái)法拉第籠法的測(cè)試在一個(gè)長(zhǎng)0.5m 寬0.35m 高0.15m的金屬屏蔽盒中進(jìn)行,如圖(四)所示。被測(cè)試線路板與底部參考地的距離為0.03m,與周圍金屬面的距離至少為0.06m,測(cè)試端口的共模阻抗為150Ω,其它功能連線應(yīng)經(jīng)過相應(yīng)的濾波器并接磁環(huán)使其共模阻抗遠(yuǎn)大于150Ω(頻率150kHz 時(shí)LCM≥280uH)。其測(cè)試布置如圖(六)所示。

圖(四)工作臺(tái)法拉第籠法圖(五)磁場(chǎng)探頭法

工作臺(tái)法拉第籠法用于評(píng)估可在小尺寸的線路板上模擬其獨(dú)立功能的集成電路。集成電路的電磁發(fā)射可在預(yù)定的工作條件下進(jìn)行測(cè)量,另外該方法可以直接測(cè)量實(shí)際應(yīng)用電路板相同或與實(shí)際應(yīng)用相近的電路板,這就為預(yù)測(cè)集成電路在實(shí)際應(yīng)用場(chǎng)合的電磁發(fā)射情況提供了評(píng)估方法,也為在對(duì)EMC有強(qiáng)制性要求的集成電路功能模塊的電磁發(fā)射性能分級(jí)提供了測(cè)試方法。

該方法來源于IEC61000-4-6,當(dāng)線路板的電尺寸較小,也就是尺寸≤ , 如在1GHz 頻率線路板尺寸小于0.15m 時(shí),連接線路板的電纜成為集成電路的發(fā)射天線,電磁發(fā)射主要由這些天線產(chǎn)生,相對(duì)這些天線,由集成電路本身產(chǎn)生的發(fā)射小得多,通常可以忽略。從該方法的原 理可以看出,測(cè)試結(jié)果中還體現(xiàn)了如下因數(shù)的影響:電路板的布線結(jié)構(gòu);集成電路的去耦措施;電容、電感等分立元

, 如在1GHz 頻率線路板尺寸小于0.15m 時(shí),連接線路板的電纜成為集成電路的發(fā)射天線,電磁發(fā)射主要由這些天線產(chǎn)生,相對(duì)這些天線,由集成電路本身產(chǎn)生的發(fā)射小得多,通常可以忽略。從該方法的原 理可以看出,測(cè)試結(jié)果中還體現(xiàn)了如下因數(shù)的影響:電路板的布線結(jié)構(gòu);集成電路的去耦措施;電容、電感等分立元

件的高頻性能以及集成電路內(nèi)部不同功能模塊工作時(shí)的影響。所以用專門制作的標(biāo)準(zhǔn)測(cè)試板測(cè)試可以比較集成電路EMC性能,而用實(shí)際電路板還可以評(píng)估實(shí)際應(yīng)用場(chǎng)合所設(shè)計(jì)的線路板的EMC性能。在共模測(cè)試端測(cè)得的電壓與測(cè)試距離為10米時(shí)的騷擾場(chǎng)強(qiáng)的關(guān)系大致為:

實(shí)際場(chǎng)強(qiáng)數(shù)值與線路板及引線的結(jié)構(gòu)和長(zhǎng)度有很大的關(guān)系。

5、磁場(chǎng)探頭法

該方法用于測(cè)量由集成電路輸出到線路板引線上的射頻電流引起的電磁輻射,與該激勵(lì)電流有關(guān)的引線、電源層和地層以及與線路板相連的電纜起到了發(fā)射天線的作用,產(chǎn)生的場(chǎng)強(qiáng)的大小與該電流成正比。線路板的設(shè)計(jì),虛擬天線的發(fā)射效率,射頻電流的耦合因子等因數(shù)也會(huì)影響最終場(chǎng)強(qiáng)的大小,而集成電路的射頻電流是產(chǎn)生電磁輻射的根源。所以測(cè)量集成電路產(chǎn)生的射頻電流可作為評(píng)價(jià)

集成電路、PCB 板及系統(tǒng)EMC特性的一個(gè)方法。采用一個(gè)微型磁場(chǎng)探頭在被測(cè)線路(如電源線或I/O線)上的特定位置測(cè)量其磁場(chǎng)就可經(jīng)計(jì)算得出被測(cè)引線上的電流大小。在該磁場(chǎng)探頭放置精確的情況下用這種方法所得的測(cè)試結(jié)果的可重復(fù)性比較高。

我所根據(jù)工作臺(tái)法拉第籠法和磁場(chǎng)探頭法建立了兩個(gè)方法的測(cè)試系統(tǒng),測(cè)試儀器采用Agilent公司的頻譜分析儀E4440A和26dB的預(yù)放大器。 E4440A的頻率范圍為10Hz—26.5GHz,它的分辨率帶寬可從1Hz-8MHz的范圍內(nèi)選擇,并具有附合CISPR標(biāo)準(zhǔn)的電磁干擾測(cè)試分辨率帶寬和峰值、準(zhǔn)峰值和平均值檢測(cè)模式,它還具有MIL-STD-461E標(biāo)準(zhǔn)要求的帶寬和檢波方式,適合用于電磁騷擾的測(cè)試與評(píng)估。測(cè)量小信號(hào)的靈敏度很高,在1Hz時(shí)底噪聲可達(dá)到-160dBm,配上預(yù)放大器,即使磁場(chǎng)探頭的插入損耗大,也足以檢測(cè)到較小的干擾信號(hào)。為提高測(cè)量準(zhǔn)確度,系統(tǒng)配備了射頻電壓校準(zhǔn)功能,使儀器的測(cè)量誤差小于1dB。工作臺(tái)法拉第籠法和磁場(chǎng)探頭法的特點(diǎn)是不僅能測(cè)試專用測(cè)試電路的電磁兼容性,還可以在實(shí)際的應(yīng)用板上進(jìn)行測(cè)試,可作為不同設(shè)計(jì)應(yīng)用方案的性能評(píng)估,評(píng)價(jià)實(shí)際應(yīng)用線路板的電路EMC性能,這樣集成電路生產(chǎn)企業(yè)與應(yīng)用集成電路設(shè)計(jì)產(chǎn)品的工程師都能利用該方法進(jìn)行檢測(cè)。由于其體積小,使用方便,可方便EMC設(shè)計(jì)人員查找產(chǎn)品電路設(shè)計(jì)、結(jié)構(gòu)布局方面存在的問題,在電路設(shè)計(jì)改進(jìn)階段和產(chǎn)品的整改階段提供幫助。