摘要:在軟件接收機的研究中,,為了實現在GPS或者北斗模式下基帶對射頻前端數據的采集,在Altera公司的CycloneⅢ系列FPGA器件上采用VERILOG語言編寫了SPI總線協(xié)議,,完成了對射頻前端芯片GPS/北斗兩種工作模式的切換,,使基帶可以隨時獲得兩種模式下的數據。通過驗證,,采集來的數據與期望的結果一致,。同時為工程設計提供了一種原型,也為進一步的工程開發(fā)奠定了基礎,。

關鍵詞:SPI總線協(xié)議,;FPGA;射頻前端,;基帶

隨著現代技術的發(fā)展,,SPI接口總線已經成為了一種標準的接口,,由于協(xié)議實現簡單,并且I/O資源占用少,,為此SPI總線的應用十分廣泛,。目前,SPI接口的軟件擴展方法雖然簡單方便,,但若用來通信,,則速度受到限制。因此,,我們采用ALTERA公司的FPGA器件設計SPI總線的通信接口,,該總線接口具有高速、配置靈活等優(yōu)點,,大大地縮短了系統(tǒng)的開發(fā)周期,。

1 SPI總線原理

1.1 SPI總線協(xié)議簡介

SPI總線是一種全雙工同步串行接口,能夠實現微控制器與外設通信,。它采用主從模式架構,,支持多slave模式應用,并且只占用芯片上四個管腳,,節(jié)省了芯片的引腳,。

1.2 SPI總線接口

SPI是一個環(huán)形總線結構,通常有4條線:串行時鐘(SCK)線,、主機輸入/從機輸出(MISO)數據線,,主機輸出/從機輸入(MOSI)數據線和低電平有效的從機選擇線(CS),。

SPI總線在與外設進行數據交換時,,可根據外設的工作要求,配置SCK的相位和極性,,從而產生不同的數據格式,。如果時鐘相位CPFIA=0,數據在時鐘脈沖的前沿被采樣,;如果時鐘相位CPHA=1,,數據在時鐘脈沖的后沿被采樣。如果時鐘的極性CPOL=0,,串行數據的移位操作由時鐘的正脈沖觸發(fā),;如果時鐘的極性CPOL=1,串行數據的移位操作由時鐘的負脈沖觸發(fā),。因此,,SPI主模塊和從模塊的時鐘相位和極性應該一致。

2 開發(fā)平臺介紹

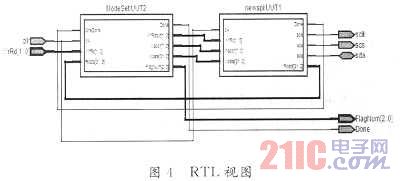

本文主要介紹在FPGA中實現基帶對射頻前端數據的采集,,通過SPI總線實現對射頻前端模式的轉換,。當射頻前端被配置為GPS模式時,,采集到的數據來自GPS衛(wèi)星;當被配置為北斗模式時,,采集到的數據來自北斗衛(wèi)星,。本文選用的芯片為杭州中科微有限公司HZG09V2D和ALTERA公司Cyclone III系列中的EP3C40Q240C8。接口之問的連接關系如圖1所示,。

HZG09V2D是杭州中科微有限公司的一款射頻芯片,,它是一款工作在L1頻段的多模式衛(wèi)星導航射頻前端接收芯片,可支持L1頻段中國北斗二代,、美國GPS,、俄羅斯GLONASS、歐洲伽利略等多個導航系統(tǒng),。

EP3C40Q240C8是Altera公司CycloneⅢ系列中的一款FPGA芯片,,它前所未有地同時實現了低功耗、低成本和高性能,。其中CycloneⅢFPGA在布局上提供豐富的存儲器和乘法器資源,,并且所有體系結構都含有非常高效的互聯。

3 FPGA實現與調試結果

3.1 實現步驟

首先使用ModelSim SE 6.2對所編寫的Verilog代碼進行編譯仿真,,從而得到對功能的驗證,。再用QuartusⅡ軟件進行編譯后,將生成的編程文件.sof文件通過JTAG下載到Altera公司CycloneⅢ系列EP3C40Q240C8運行,,在數字示波器的輔助分析下都得到了正確的結果,。

3.2 模塊設計

3.2.1 分頻模塊

由于SPI總線協(xié)議要求的SCK時鐘頻率與FPGA時鐘頻率不一致,所以對基帶時鐘進行分頻,。本文中,,基帶時鐘頻率為40 MHz,SPI總線時鐘頻率為1 MHz,,故需要進行40倍分頻,。

3.2.2 發(fā)送數據模塊

在片選信號拉低之前,時鐘信必須為低電平,。當片選信號拉低后,,SCK開始工作,然后寫八位地址,,接著寫32位數據,;發(fā)送操作結束后,片選信號拉高,,SCK=0,。代碼如下:

3.2.3 接收數據模塊

當片選拉低后,SCK=0,,同時寫八位地址并且使SDA為高阻,,再讀32位數據,;當片選拉高時,CS=1,,SCK=0,,此外,在片選信號拉低之前,,SCK必須為低電平,。代碼如下:

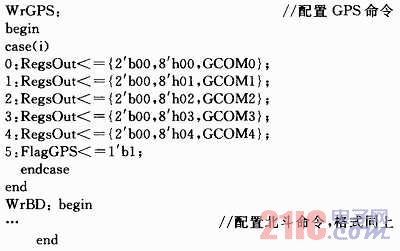

3.2.4 配置模塊

配置模塊發(fā)送GPS/Compass模式配置命令給SPI功能模塊,從而實現一次完整的射頻前端工作模式配置,。其中,,射頻前端有5個與SPI相關的配置寄存器,具體模式配置命令如下:

3.3 仿真結果

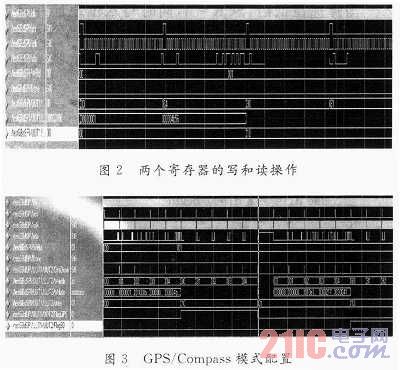

在GPS模式下,,實現了寄存器的讀寫時序,,如圖2所示。

在GPS/Compass模式下,,實現了5個地址的寫操作和讀操作,。在基帶處理中,將讀出來的數據與設定好的配置的數據進行對比,,當結果一致后,,就完成了一次正確的配置操作。如圖3所示,。

3.4 RTL視圖

RTL視圖由兩個模塊組成,,分別為ModeSet和newspi,其中ModeSet模塊的功能是發(fā)送命令來配置射頻前端的模式,,newspi模塊實現射頻前端和基帶之間具體的數據讀寫,。如圖4所示。

4 結語

在現代SPI總線得到了廣泛的應用,,它能夠有效地與FPGA編程結合在一起,,利用FPGA的靈活性,將大大減少了電子設計的開發(fā)周期,。本文通過FPGA實現了射頻前端GPS/北斗模式的切換,為將來射頻前端多模設計奠定了基礎,,并且可通過外部器件查看讀寫操作是否完成,,從而實現了實時配置。