引言

ARM和DSP作為嵌入式技術(shù)應(yīng)用在地震信號(hào)處理系統(tǒng)中,能很好地滿足地震加速度計(jì)對實(shí)時(shí)性、高精度以及網(wǎng)絡(luò)化的要求,因此,利用光線傳感基于ARM 和DSP雙核微處理器的嵌入式系統(tǒng)設(shè)計(jì)方案,一方面發(fā)揮DSP的快速信號(hào)處理能力,且能進(jìn)行小數(shù)運(yùn)算,提高運(yùn)算精度,完成地震加速度已調(diào)信號(hào)的解調(diào)和頻譜分析;另一方面充分利用ARM豐富的片上系統(tǒng)資源,能實(shí)現(xiàn)解調(diào)信號(hào)及其頻譜信息的網(wǎng)絡(luò)傳輸和顯示,該方案僅通過改變軟件無需重構(gòu)電路就能方便快捷地實(shí)現(xiàn)系統(tǒng)升級。

1 系統(tǒng)構(gòu)成及工作原理

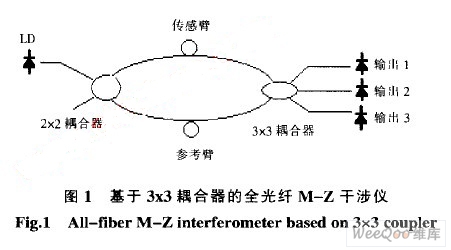

地震加速度計(jì)由傳感探頭、光電轉(zhuǎn)換及信號(hào)處理系統(tǒng)構(gòu)成。傳感探頭由采用基于3x3耦合的光纖M—z干涉儀和相關(guān)機(jī)械部分組成。如圖1所示,干涉儀的輸入端是一只2x2耦合器,輸出端是一只3x3耦合器,被測信號(hào)加在干涉儀的傳感臂上。

干涉儀的兩臂光纖分別纏繞在傳感頭中的上下兩個(gè)力臂圓筒上,當(dāng)外部施加振動(dòng)時(shí),簡諧振子施加給信號(hào)臂光纖一個(gè)縱向的應(yīng)力,光纖的長度產(chǎn)生變化±△L (應(yīng)變效應(yīng))、光纖芯的直徑d產(chǎn)生變化±△d(泊松效應(yīng))、纖芯折射率n產(chǎn)生變化±△n(光彈效應(yīng)),這些變化將導(dǎo)致光纖中光波的相位發(fā)生變化。泊松效應(yīng)相對應(yīng)變效應(yīng)和光彈效應(yīng)造成的相位變化非常小,可以忽略不計(jì),從而即完成加速度信號(hào)對光信號(hào)的相位調(diào)制。參考臂和信號(hào)臂在3x3耦合器內(nèi)發(fā)生十涉,將相位變化轉(zhuǎn)換成光強(qiáng)變化,輸出的光強(qiáng)信號(hào)經(jīng)PIN轉(zhuǎn)換為電流信號(hào),輸出給信號(hào)處理系統(tǒng),能進(jìn)行地震加速度信號(hào)的解調(diào)、頻譜分析顯示及網(wǎng)絡(luò)傳輸控制等。

2 信號(hào)解調(diào)原理

對傳感系統(tǒng)中的簡諧振子進(jìn)行分析可以得出,光波相位變化 Φ(t)與簡諧振子感受的加速度a(t)有如下關(guān)系。

式中,E為光纖的楊氏模量;A為光纖的橫截面積;為彈簧片剛度系數(shù):為有效光纖長度;m為簡諧振子質(zhì)量。從(1)式可以看出被測加速度與光相位變化呈線性關(guān)系。

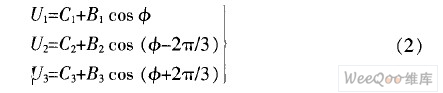

在3x3耦合對稱情況下,從干涉儀輸出的3路電流信號(hào),經(jīng)I,v變換電路和放大電路后的輸出為:

式中,C 、B ( i=1,2,3)分別為3路輸出的直流分量和交流增益;為被測信號(hào)引起的光相位差。從(2)中解出Φ(t),再結(jié)合(1)式就可以得到加速度信號(hào)。求解Φ(t)的算法框圖如圖2所示。

解調(diào)輸出信號(hào):

結(jié)合式(1)和式(3)即可求出加速度a(t)。

3 信號(hào)處理的硬件實(shí)現(xiàn)

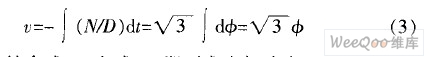

信號(hào)處理子系統(tǒng)的原理框圖如圖3所示。

以ARM(選用飛利浦公司的LPC2214)和DSP(Ti公司的TMS320VC5402)為核心,外擴(kuò)信號(hào)調(diào)理、A/D采集、網(wǎng)絡(luò)控制及液晶顯示模塊。以ARM作為系統(tǒng)控制中心,控制A/D轉(zhuǎn)換器進(jìn)行地震加速度已調(diào)信號(hào)的采集,經(jīng)DSP的HPI接口將數(shù)據(jù)存儲(chǔ)到DSP內(nèi)部RAM 中。完成解調(diào)信號(hào)的網(wǎng)絡(luò)傳輸控制、實(shí)時(shí)顯示以及TMS320VC5402的HPI引導(dǎo)裝載。而DSP主要進(jìn)行信號(hào)運(yùn)算,完成解調(diào)和FFT頻譜分析。

LPC2214控制器片內(nèi)有16 kbits RAM和256 kbitsFLASHl 31.為了便于系統(tǒng)升級,擴(kuò)展了128 kbits的外部RAM 和2 Mbits的外部FLASH.由于DSP要對大量的數(shù)據(jù)進(jìn)行運(yùn)算,而內(nèi)部RAM 空間有限且還要用于存放上電復(fù)位后的boot loader程序,所以擴(kuò)展128 kbits外部RAM.

LPC2214有bank。 bank 4個(gè)外部存儲(chǔ)器組,而對于圖3中的系統(tǒng)設(shè)計(jì),ARM擴(kuò)展的存儲(chǔ)器或外部I/O器件有6個(gè)。所以利用片選信號(hào)CS3、地址線A23、A22、A21和一片138譯碼器進(jìn)行地址空間細(xì)分,此片外存儲(chǔ)器或I/O 器件屬于bank,組, 所用地址為0x83000000~0x83ffffff。

3.1 信號(hào)調(diào)理及A,D采集電路

信號(hào)調(diào)理最主要目的是為了去除信號(hào)中的噪聲,使被測電壓范圍和AD采樣范圍相匹配以提高采樣精度。本系統(tǒng)選用Anolog Device公司的ADA4861—3專用放大芯片。該芯片集成了3路放大器。采用單5 V供電。通過調(diào)節(jié)外接電阻的阻值可以獲得1~1 900的放大增益,輸出具有良好的線性度和溫度穩(wěn)定性。由于放大電路集成在芯片中。故減少了噪聲的引入。

選擇MD芯片主要考慮的性能指標(biāo)有分辨率、轉(zhuǎn)換速率、輸入通道數(shù)、信噪比、輸出接口等參數(shù)。因?yàn)樗杉募铀俣刃盘?hào)頻率在1 kHz以內(nèi)根據(jù)奈圭斯特定理采樣頻率 >2 kHz就能無失真地恢復(fù)原信號(hào),輸入信號(hào)有3路,綜合考慮以上因素本系統(tǒng)選用Anolog Device公司生產(chǎn)的AD7655芯片。該芯片支持4路輸入(INA1、INA2、INB。、INB2),轉(zhuǎn)換位數(shù)達(dá)16位,1MSPS的轉(zhuǎn)換速率,單電源+5 V供電,串/并口輸出方式,雙通道同步采樣。采樣由A。引腳電平控制,A0=0,INA1/INB1采樣同步;A o=1,INA~NB2采樣同步問。參考電壓 面接2.5 V,分辨率為2×VREF/655 36,約為76-3 V.

3.2 ARM 和DSP的接口電路

ARM 和DSP通過HPI接口進(jìn)行連接。ARM先向DSP寫入控制字,設(shè)置工作模式,然后將訪問地址寫入地址寄存器(HPIA),再對數(shù)據(jù)鎖存器(HPID)進(jìn)行讀寫,即可讀出和寫入指定的存儲(chǔ)單元。主機(jī)由兩根地址線A 、A 可以尋址到HPI接口的控制寄存器、地址寄存器和數(shù)據(jù)寄存器[51;由HBIL、HCNTL1、HCNTL0區(qū)分16位數(shù)據(jù)的高、低字節(jié)。當(dāng)向HBIL=0的地址寫入數(shù)據(jù)時(shí),表示是第1個(gè)字節(jié),向HBIL=I的地址寫入數(shù)據(jù)表示第2個(gè)字節(jié)。并且在數(shù)據(jù)交互之前要設(shè)置控制寄存器中的BOB位,指示高地址在前還是低地址在前。這一步在程序初始化時(shí)由ARM來完成。DSP的片選信號(hào)接主機(jī)的nCS2,地址空間屬bankz組,即0)【82000000~0x82眥DSP可以通過HINT向主機(jī)發(fā)出中斷信號(hào),通知主機(jī)一幀數(shù)據(jù)處理完畢。主機(jī)收到中斷信號(hào)后讀取約定的DSP內(nèi)部數(shù)據(jù)空間中的數(shù)據(jù)進(jìn)行顯示或網(wǎng)絡(luò)傳輸?shù)忍幚聿僮鳌?/p>

DSP的引導(dǎo)裝載采用HPI方式,中斷2信號(hào)用于激活HPI自舉模式。有兩種方式可以用來獲取中斷2引腳上的輸入信號(hào):①將主機(jī)中斷HINT與INT2直接相連:②在捕捉到DSP復(fù)位向量后的30個(gè)時(shí)鐘周期內(nèi)觸發(fā)一個(gè)有效的外部中斷INT2.由于本設(shè)計(jì)HINT信號(hào)用于向主機(jī)產(chǎn)生中斷信號(hào),所以HPI自舉加載采用方式②。注意到在自舉加載的開始,HINT引腳會(huì)產(chǎn)生一個(gè)有效的中斷信號(hào),所以ARM在初始化時(shí)要清除這個(gè)中斷。

3.3 ARM 和DM9Ooo網(wǎng)絡(luò)控制接口

DM90OOE是Davicom公司生產(chǎn)的以太MAC控制器。支持10/100 Mbps傳輸速率。電路使用16位總線方式進(jìn)行控制。即數(shù)據(jù)總線D。~D。與芯片的SD。~SD。連接,地址線也進(jìn)行相對應(yīng)的連接,片選線與芯片的AEN相連。DM9000E 以太網(wǎng)控制器的基地址為Ox300。而總線的地址線A 與芯片的命令/數(shù)據(jù)使能端CMD相連,所以對其進(jìn)行操作的地址是0x300(地址端口)和0x304(數(shù)據(jù)端口),而結(jié)合ARM 的片選線得到的32位地址為0x83000300 (地址端口)和0x83000304(數(shù)據(jù)端口)。

4 系統(tǒng)軟件設(shè)計(jì)

傳統(tǒng)的嵌入式系統(tǒng)軟件設(shè)計(jì)中,由于廣泛采用單任務(wù)順序機(jī)制因而編程復(fù)雜。同時(shí)系統(tǒng)安全性差而導(dǎo)致系統(tǒng)頻繁復(fù)位以至無法達(dá)到設(shè)計(jì)目標(biāo)。本設(shè)計(jì)在軟件設(shè)計(jì)中引入tzCOS—II實(shí)時(shí)操作系統(tǒng),使程序設(shè)計(jì)變得非常簡單,將操作系統(tǒng)移植到LPC2214中以提高系統(tǒng)實(shí)時(shí)性。

首先編寫好與硬件接口的驅(qū)動(dòng)程序。應(yīng)用層程序以任務(wù)為編程對象。任務(wù)具有任務(wù)堆棧、優(yōu)先級等參數(shù),根據(jù)任務(wù)的執(zhí)行順序和重要程度可分配不同的優(yōu)先級;在任務(wù)調(diào)度過程中可以通過OSTaskSuspend(os PRIO—SELF)、OSTaskResume(task_prio)函數(shù)進(jìn)行任務(wù)之間的切換。本系統(tǒng)可分為DSP boot loader、 D采集、讀HPI、寫HPI、網(wǎng)絡(luò)傳輸、液晶顯示等6大任務(wù)。在主函數(shù)中創(chuàng)建任務(wù),設(shè)置任務(wù)各項(xiàng)參數(shù)。主程序流程圖如圖4所示。

5 實(shí)驗(yàn)結(jié)果及分析

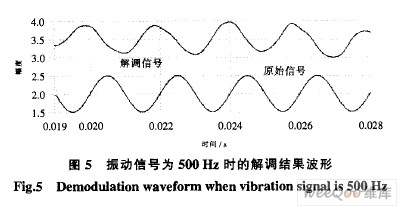

用丹麥產(chǎn)PM4808型振動(dòng)臺(tái)模擬產(chǎn)生地震信號(hào),將光纖傳感器輸出信號(hào)輸入到本系統(tǒng)進(jìn)行解調(diào)及頻譜分析網(wǎng)絡(luò)傳輸測試實(shí)驗(yàn),解調(diào)實(shí)驗(yàn)結(jié)果分別如圖5所示。

從圖5可以看出,系統(tǒng)能較準(zhǔn)確地解調(diào)出原始信號(hào),其誤差主要來源有光纖傳感耦合器的非對稱、A/D量化誤差、模擬電路中殘留的熱噪聲干擾等等。

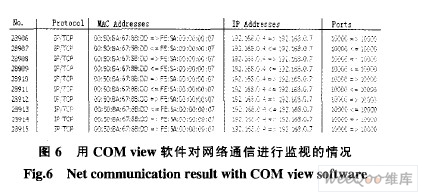

圖6所示為網(wǎng)絡(luò)數(shù)據(jù)包的傳輸情況。其中PC機(jī)的IP地址設(shè)置為192.168.0.4,本設(shè)計(jì)系統(tǒng)的IP地址設(shè)置為192.168.0.7,端*為10000.實(shí)驗(yàn)證明所設(shè)計(jì)的嵌入式信號(hào)處理系統(tǒng)可以實(shí)現(xiàn)基于TCP/IP的網(wǎng)絡(luò)通信。

6 結(jié)語

本文設(shè)計(jì)的雙CPU光纖傳感地震加速度信號(hào)處理系統(tǒng)能實(shí)時(shí)地完成信號(hào)解調(diào)、頻譜分析及其網(wǎng)絡(luò)傳輸,系統(tǒng)靈敏度達(dá)4.35 V/g,支持10/100 Mbps速率的以太網(wǎng)傳輸,其提供網(wǎng)絡(luò)控制接口對于實(shí)現(xiàn)傳感器網(wǎng)絡(luò)化、數(shù)據(jù)共享、遠(yuǎn)程監(jiān)控等具有重要意義采用雙CPU的處理方案,實(shí)現(xiàn)了對光纖傳感地震加速度信號(hào)的高精度采集和快速處理,并具有以太網(wǎng)傳輸功能,實(shí)現(xiàn)了地震加速度數(shù)據(jù)的共享。