關(guān)鍵字:

作者:Stuart Cording,德州儀器 (TI) 應(yīng)用工程師

Lori Vidra,TI eXpressDSP" title="DSP">DSP開(kāi)發(fā)工具市場(chǎng)營(yíng)銷經(jīng)理

許多電池供電的手持系統(tǒng)都要求具備數(shù)字信號(hào)處理功能,設(shè)計(jì)這種產(chǎn)品時(shí),我們必須高度重視功耗問(wèn)題" title="功耗問(wèn)題">功耗問(wèn)題。

選擇具備所有必需的計(jì)算能力且還能滿足設(shè)計(jì)功耗要求的DSP,使設(shè)計(jì)要么取得顯著成功,要么徹底失敗,設(shè)計(jì)小組不得不進(jìn)行昂貴的再設(shè)計(jì)。

不過(guò),大多數(shù)設(shè)計(jì)工程師已經(jīng)痛苦地了解到,傳統(tǒng) DSP 功耗估算方法最多也只能獲得近似值,因此我們需要用軟件來(lái)管理功耗并估算功耗的新技術(shù)。

數(shù)據(jù)表不夠用

以前,設(shè)計(jì)小組選擇處理器時(shí)首先要查看備選DSP的數(shù)據(jù)表。以 mA/MIP 或mA/MHz 為單位的測(cè)量值通常與芯片的最大 IDD 配套提供。幾乎所有數(shù)據(jù)表都提供上述信息。

上述數(shù)據(jù)的問(wèn)題在于,功耗很大程度上取決于應(yīng)用本身,而數(shù)據(jù)表中的統(tǒng)計(jì)數(shù)據(jù)往往不能完全符合實(shí)際應(yīng)用。

半導(dǎo)體公司認(rèn)識(shí)到上述問(wèn)題,通常只給出基本情況,供估算功耗數(shù)值參考。舉例來(lái)說(shuō),常見(jiàn)的 TI DSP 會(huì)給出以下工作情況:CPU 執(zhí)行 75% 雙 MAC 和 25% ADD,數(shù)據(jù)總線活動(dòng)適中(正弦波形圖表)。CPU 及 CLKGEN (DPLL) 域處于工作狀態(tài)中。

除非設(shè)計(jì)小組的應(yīng)用情況與上述描述一致,否則數(shù)據(jù)表中的數(shù)據(jù)僅用于比較同一制造商推出的類似芯片。事實(shí)上,其他半導(dǎo)體公司很可能會(huì)在不同情況下測(cè)量功耗。

還有一些情況會(huì)使得數(shù)據(jù)表上的數(shù)據(jù)更加值得懷疑,這對(duì)那些面臨嚴(yán)格功耗限制的設(shè)計(jì)人員提出了更嚴(yán)峻的挑戰(zhàn)。

- DSP是復(fù)雜的芯片,其包括休眠模式和斷電模式等節(jié)電功能。上述功能會(huì)將單次估算中的誤差加以放大。

- 數(shù)據(jù)表未考慮到功耗實(shí)際上由兩部分組成:工作在內(nèi)核電壓源上的處理器和工作在 I/O 電源上的外設(shè)" title="外設(shè)">外設(shè)都涉及功耗問(wèn)題。

- 設(shè)計(jì)小組希望用不同的實(shí)施方法和平臺(tái)比較功耗。

由于面臨上述挑戰(zhàn),設(shè)計(jì)小組往往需要構(gòu)建原型板,并根據(jù)不同處理器、實(shí)施方法及平臺(tái)等因素對(duì)功耗加以估算。上述方法盡管要花很多時(shí)間而且成本不菲,但至少還能為我們提供比較精確的數(shù)據(jù)。

變量測(cè)量

我們對(duì)估算不同情況及實(shí)施方法下的功耗所用的方法已經(jīng)有了較好的了解。只有經(jīng)過(guò)細(xì)分,并根據(jù)實(shí)際測(cè)量得出的數(shù)據(jù)才會(huì)更加有用。具體過(guò)程通常如下:

- 將芯片分為子系統(tǒng);

- 獨(dú)立執(zhí)行每個(gè)子系統(tǒng);

- 用減法分析來(lái)確定每個(gè)子系統(tǒng)的功耗;

- 確定每個(gè)子系統(tǒng)的最大功耗及閑置功耗;

- 用內(nèi)插法估算子系統(tǒng)功耗;

- 最后用疊加法估算芯片功耗。

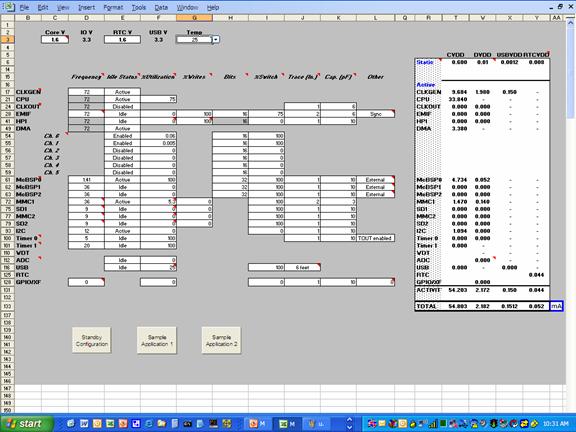

我們通常將經(jīng)測(cè)量得出的數(shù)據(jù)連同制造商給出的數(shù)據(jù)(如內(nèi)核電壓)制成電子數(shù)據(jù)表,并通過(guò)適當(dāng)運(yùn)算進(jìn)行估算。如圖 1 所示,右側(cè)的灰白部分即為功耗估算結(jié)果。

圖1. 電子數(shù)據(jù)表有一定的用處,但仍不能反映實(shí)際情況。

這種方法與數(shù)據(jù)表值比較法相比盡管有一定改進(jìn),但仍需進(jìn)一步完善。舉例來(lái)說(shuō),我們不妨假設(shè)主要用于過(guò)濾應(yīng)用的 DSP,其工作時(shí)間約占 20%,待機(jī)時(shí)間約占80%。

目前的 DSP 需要考慮到占空比問(wèn)題,這有助于節(jié)電。舉例來(lái)說(shuō),芯片不工作時(shí),電壓可降至待機(jī)數(shù)值。頻率在 CMOS 功耗中起主要作用,如果芯片不參與過(guò)濾工作,那么我們就能降低頻率。

電源優(yōu)化技術(shù)

TI 等半導(dǎo)體廠商努力推出芯片級(jí)電源控制技術(shù)。以前設(shè)計(jì)小組是無(wú)法應(yīng)用這種特性的。現(xiàn)在,設(shè)計(jì)人員能通過(guò)軟件發(fā)揮電源優(yōu)化技術(shù)的優(yōu)勢(shì)。

為了說(shuō)明如何實(shí)現(xiàn)上述工作,我們不妨先來(lái)看看設(shè)計(jì)小組能采用哪些優(yōu)化性能的方法。

在芯片自身內(nèi)部,系統(tǒng)設(shè)計(jì)人員能采用深度休眠模式、動(dòng)態(tài)電壓和頻率縮放等技術(shù),而且還能在芯片閑置時(shí)關(guān)閉不必要的資源。

我們還能在系統(tǒng)啟動(dòng)過(guò)程中節(jié)約大量電力。通常說(shuō)來(lái),啟動(dòng)過(guò)程中會(huì)開(kāi)啟所有系統(tǒng),不過(guò)我們可以讓那些應(yīng)用及啟動(dòng)過(guò)程中不用的部分關(guān)閉或保持閑置狀態(tài)。

我們?cè)谲浖a優(yōu)化時(shí)也要想到功耗問(wèn)題。通常的規(guī)律是,我們應(yīng)以盡可能小的占用空間集成盡可能多的必需功能,這樣可以縮減存儲(chǔ)器的占用面積。不過(guò),由于應(yīng)用不得不更頻繁的執(zhí)行代碼,這種做法往往會(huì)導(dǎo)致功耗的加大。

編寫代碼時(shí)還應(yīng)減少指令存取的數(shù)量,并優(yōu)化緩存和內(nèi)部指令緩沖。上述措施都有助于節(jié)約DSP的工作模式時(shí)間,并最大化閑置時(shí)間,以此來(lái)降低頻率和電壓。

我們還能用其他技術(shù)來(lái)實(shí)現(xiàn)系統(tǒng)級(jí)控制,包括:

- 認(rèn)真選擇組件

- 盡可能減少組件數(shù)量

- 首先采用內(nèi)部存儲(chǔ)器來(lái)最小化芯片間的功率損耗

- 對(duì)于啟動(dòng)或低速運(yùn)算以及偶爾用到的功能采用外部存儲(chǔ)器

- 啟動(dòng)后給啟動(dòng)存儲(chǔ)器斷電

新一代電源控制技術(shù)

通常說(shuō)來(lái),半導(dǎo)體廠商在芯片中內(nèi)置的節(jié)電功能會(huì)自動(dòng)工作,舉例來(lái)說(shuō),芯片進(jìn)入閑置狀態(tài)后電壓和頻率就會(huì)自動(dòng)降低。

不過(guò),我們現(xiàn)在有了更尖端的技術(shù),系統(tǒng)設(shè)計(jì)人員現(xiàn)在能對(duì) DSP BIOS 進(jìn)行工作,從而進(jìn)一步加強(qiáng)電源管理。

自動(dòng)的電壓或頻率縮放是一種有用的特性。不過(guò) DSP 的內(nèi)核電壓快速變動(dòng)往往會(huì)對(duì)外設(shè)造成意料不到的影響。操作系統(tǒng)的時(shí)基可能會(huì)因頻率變動(dòng)而受到影響,有些外設(shè)驅(qū)動(dòng)程序可能需要了解頻率和電源狀態(tài)的變化,這樣才能繼續(xù)有效工作。

操作系統(tǒng)調(diào)度程序的有效性也會(huì)因?yàn)轭l率縮放而受影響。通常說(shuō)來(lái),系統(tǒng)應(yīng)進(jìn)行協(xié)調(diào),以確保安全的電壓和頻率控制,適當(dāng)?shù)剡M(jìn)入閑置狀態(tài)。

半導(dǎo)體廠商通過(guò)創(chuàng)建DSP BIOS功率調(diào)整程序庫(kù)" title="程序庫(kù)">程序庫(kù),可實(shí)現(xiàn)更高級(jí)的功耗控制,同時(shí)還能確保避免因電壓和頻率縮放而發(fā)生問(wèn)題。通過(guò)GPIO引腳向外設(shè)發(fā)送消息,我們還能將上述控制技術(shù)從芯片延伸到外設(shè)。

圖2顯示了功率調(diào)整例程的實(shí)例(如下圖中的 PSL),設(shè)計(jì)人員通過(guò)代碼編寫,可從程序庫(kù)中直接調(diào)用。

我們不妨假設(shè) DSP 正在運(yùn)行非常復(fù)雜的算法。通常說(shuō)來(lái),內(nèi)核電壓為 1.6V,頻率為 200 MHz,如圖 2 中左側(cè)藍(lán)線所示。不過(guò),當(dāng)未運(yùn)行算法時(shí),我們可用功率調(diào)整程序庫(kù)將頻率降至 72 MHz。

一般來(lái)說(shuō),內(nèi)核電壓會(huì)保持為1.6V。不過(guò)我們也可用功率調(diào)整程序庫(kù)安全地將電壓降至1.2V,從而在算法不運(yùn)行期間使功耗進(jìn)一步降低 30 mW。

TI 率先在其TMS320VC5509A DSP中采用功率調(diào)整程序庫(kù),這就是本例所用的DSP。

圖2. 功率調(diào)整程序庫(kù)功能實(shí)現(xiàn)功耗微調(diào)。

新一代功耗估算技術(shù)

除了上述各種功耗工具的幫助之外,設(shè)計(jì)人員還需要想辦法估算整個(gè)系統(tǒng)的功率。解決這一問(wèn)題的最新方法需要將半導(dǎo)體公司提供的軟件與虛擬儀表廠商(如美國(guó)國(guó)家儀器公司National Instruments)提供的硬件進(jìn)行集成。

在采用這種方法時(shí),開(kāi)發(fā)人員可利用美國(guó)國(guó)家儀器公司提供的 LabView 來(lái)監(jiān)控實(shí)際應(yīng)用過(guò)程中芯片的執(zhí)行情況。TI 在數(shù)據(jù)表中提供了有關(guān) TMS320VC5509 的豐富功率測(cè)試數(shù)據(jù)。

采用 LabView 和 C55 電源優(yōu)化 DSK (C55 Power Optimization DSP Starter Kit),設(shè)計(jì)小組能嘗試采用不同的實(shí)施方案,并用類似于圖 3 所示的 GUI 工具對(duì)功耗加以調(diào)節(jié)。

圖3. 調(diào)節(jié)DSP 內(nèi)核、I/O及電路板功耗。

我們可用上述工具包探索各種設(shè)計(jì)方案,并分別測(cè)得 DSP 內(nèi)核、DSP I/O 以及包括閃存存儲(chǔ)器、編解碼器及其他外設(shè)在內(nèi)的整個(gè)電路板的高精度功耗。

通過(guò)結(jié)合采用上述創(chuàng)新方法來(lái)控制芯片功耗并估算系統(tǒng)功耗,設(shè)計(jì)人員能夠獲得一種功能強(qiáng)大的新型方法,適用于功耗要求嚴(yán)格的 DSP 應(yīng)用。