FPGA是一種現(xiàn)場(chǎng)可編程器件,設(shè)計(jì)靈活方便可以反復(fù)修改內(nèi)部邏輯,適用于算法結(jié)構(gòu)比較簡(jiǎn)單、處理速度較高的情況。DSP是一種基于指令集的處理器,適于大信息、復(fù)雜算法的信息處理場(chǎng)合。鑒于兩種處理器件自身優(yōu)勢(shì),F(xiàn)PGA+DSP信號(hào)處理架構(gòu),已成為信號(hào)處理系統(tǒng)的常用結(jié)構(gòu)。但當(dāng)前FPGA+DSP的信號(hào)處理平臺(tái)或者是基于某些固定目的,實(shí)現(xiàn)某些固定功能,系統(tǒng)的移植性、通用性較差。或者僅僅簡(jiǎn)要介紹了平臺(tái)的結(jié)構(gòu)沒(méi)有給出一些具體的實(shí)現(xiàn)。

本文提出的基于FPGA+DSP通用信號(hào)處理平臺(tái)具有兩種處理器的優(yōu)點(diǎn),兼頤速度和靈活性,而且可以應(yīng)用在不同雷達(dá)信號(hào)處理系統(tǒng)中,具有很強(qiáng)的通用性。本文舉例說(shuō)明該系統(tǒng)在連續(xù)波雷達(dá)和脈沖雷達(dá)中的典型應(yīng)用。

1 系統(tǒng)資源概述

1.1 處理器介紹

本系統(tǒng)FPGA選擇Altera公司的EP2S60F1020。Stratix II FPGA采用TSMC的90 nm低k絕緣工藝技術(shù)。Stratix II FPGA支持高達(dá)1 Gb·s-1的高速差分I/O信號(hào),滿足新興接口包括LVDS,LNPECL和HyperTransport標(biāo)準(zhǔn)的高性能需求,支持各種單端I/O接口標(biāo)準(zhǔn)。EP2S60系列內(nèi)部有48 352個(gè)ALUT;具有2 544 192 bit的RAM塊,其中M512 RAM(512 bit)329個(gè),M4K RAM(4 kbit)255個(gè),M-RAM(512 kbit)2個(gè)。具有嵌入式DSP塊36個(gè),等效18bit×18bit乘法器144個(gè);具有加強(qiáng)型鎖相環(huán)EPLL 4個(gè),快速鎖相環(huán)FPLL 8個(gè)。這些鎖相環(huán)具有高端功能包括時(shí)鐘切換,PLL重新配置,擴(kuò)頻時(shí)鐘,頻率綜合,可編程相位偏移,可編程延遲偏移,外部反饋和可編程帶寬等。

本系統(tǒng)DSP選擇ADI公司的ADSP TS201。它有高達(dá)600 MHz的運(yùn)行速度,1.6 ns的指令周期;有24 MB的片內(nèi)DRAM;雙運(yùn)算模塊,每個(gè)計(jì)算塊包含1個(gè)ALU,一個(gè)乘法器,1個(gè)移位器,1個(gè)寄存器組和1個(gè)通信邏輯單元(CLU);雙整數(shù)ALU,提供數(shù)據(jù)尋址和指針操作功能;集成I/O接口,包括14通道的DMA控制器,外部端口,4個(gè)鏈路口,SDRAM控制器,可編程標(biāo)識(shí)引腳,2個(gè)定時(shí)器和定時(shí)器輸出引腳等用于系統(tǒng)連接;IEEE1 149.1兼容的JTAG端口用于在線仿真;通過(guò)共享總線可以無(wú)縫連接多達(dá)8個(gè)TigerSHARC DSP。

1.2 FPGA+DSP結(jié)構(gòu)

由于FPGA和DSP各自的自身優(yōu)勢(shì),F(xiàn)PGA+DSP信號(hào)處理架構(gòu)已成為信號(hào)處理系統(tǒng)的常用結(jié)構(gòu)。一般情況下FPGA+DSP的拓?fù)浣Y(jié)構(gòu)會(huì)根據(jù)需要進(jìn)行不同的連接,這就導(dǎo)致這種結(jié)構(gòu)的專用性,缺乏靈活性。對(duì)于一個(gè)通用處理平臺(tái)要考慮到各種不同的信號(hào)通路,因此大部分通用FPGA+ DSP平臺(tái)都采取各個(gè)處理器間均有通路的方式。這種拓?fù)浣Y(jié)構(gòu)靈活方便,可以滿足各種不同的通路需求,這種結(jié)構(gòu)的缺點(diǎn)就是硬件設(shè)計(jì)的復(fù)雜以及可能會(huì)有資源浪費(fèi)。對(duì)于這種通用FPGA+DSP結(jié)構(gòu),F(xiàn)PGA與各個(gè)DSP之間均有連接,不同之處便是DSP之間的拓?fù)浣Y(jié)構(gòu)。一般分兩種,一是高速外部總線口耦合結(jié)構(gòu)組成多DSP系統(tǒng),這種結(jié)構(gòu)可以實(shí)現(xiàn)多DSP共享系統(tǒng)內(nèi)的資源,系統(tǒng)內(nèi)的個(gè)處理器可以共享RAM,SDRAM和主機(jī)等資源,還可共享其他處理器核內(nèi)資源。這種結(jié)構(gòu)的長(zhǎng)處就在資源共享上,但這種結(jié)構(gòu)的PCB設(shè)計(jì)十分困難,而且當(dāng)總線負(fù)載較重時(shí)速度很難提高,要達(dá)到50~60 MHz的數(shù)據(jù)速率都很難。另外一種結(jié)構(gòu)就是高速鏈路口耦合結(jié)構(gòu)。ADSP TS201有4個(gè)高速鏈路口內(nèi)核時(shí)鐘600 MHz時(shí),單向數(shù)據(jù)傳輸率最高可達(dá)600 MHz。高速鏈路口通信是點(diǎn)對(duì)點(diǎn)的,這是它的局限,但也帶來(lái)的一個(gè)優(yōu)點(diǎn)就是較高的傳輸可靠性。在本信號(hào)處理系統(tǒng)中采用第2種結(jié)構(gòu)。

1.3 本信號(hào)處理系統(tǒng)的硬件結(jié)構(gòu)

在充分考慮系統(tǒng)的通用性能上,本系統(tǒng)在硬件結(jié)構(gòu)上采用1片F(xiàn)PGA與4片DSP的拓?fù)浣Y(jié)構(gòu)。每片DSP與FPGA分別有一路鏈路口相連,4片DSP之間由鏈路口相連,同時(shí),DSPA與DSPD分別有64位的數(shù)據(jù)總線與FPGA相連。這種拓?fù)浣Y(jié)構(gòu)使得任意兩片DSP之間都可以連通,對(duì)角的DSP可以通過(guò)連到FPGA內(nèi)部的鏈路口相互通信。此外,本系統(tǒng)采用一片F(xiàn)LASG存儲(chǔ)DSP程序,對(duì)所有DSP進(jìn)行加載。DSPB,DSPC分別連有32×64 Mbit的SDRAM,對(duì)DSP的內(nèi)存空間進(jìn)行了擴(kuò)展,便于大量數(shù)據(jù)處理,如圖1所示。

2 具體應(yīng)用

2.1 在連續(xù)波雷達(dá)中的應(yīng)用

其主要功能是完成對(duì)接收的全相參體制的雙波束原始視頻信號(hào)的數(shù)字采樣信號(hào)進(jìn)行相關(guān)處理,其中包括時(shí)/頻轉(zhuǎn)換、MTI、MTD處理、雙波束估高處理等,最終能夠?qū)?dòng)目標(biāo)進(jìn)行檢測(cè)。

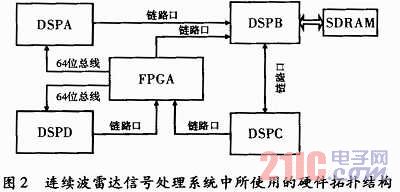

拓?fù)浣Y(jié)構(gòu):待處理數(shù)據(jù)通過(guò)接插件傳送到FPGA內(nèi)部,通過(guò)FPGA的初步處理,經(jīng)由FPGA與DSPA、DSPD相連的64位數(shù)據(jù)總線傳送到兩片DSP內(nèi)進(jìn)行進(jìn)一步的處理。DSPA將處理完的數(shù)據(jù)經(jīng)過(guò)鏈路口直接傳送到DSPB,而DSPD將處理完的數(shù)據(jù)通過(guò)DSPD到FPGA,F(xiàn)PGA到DSPB的鏈路口也傳送到DSPB。DSPC接收DSPB處理完的數(shù)據(jù)并將數(shù)據(jù)進(jìn)行進(jìn)一步的處理后通過(guò)鏈路口傳送到FPGA輸出。如圖2所示為應(yīng)用所使用的硬件拓?fù)浣Y(jié)構(gòu)。

處理流程:FPGA將接收到的兩路信號(hào)分別進(jìn)行4 096點(diǎn)FFT,并對(duì)FFT的結(jié)果進(jìn)行MTI,MTI可以是根據(jù)命令選做。DSP中完成兩路信號(hào)的二維FFT也就是MTD,CFAR,估高,雜波圖等,最后將整理后的結(jié)果輸出到FPGA,由FPGA輸出給雷達(dá)的其它模塊,如圖3所示。

資源的使用:在FPGA需要完成的功能為兩路復(fù)信號(hào)的FFT,MTI,以及與DSP的數(shù)據(jù)通信。FFT的實(shí)現(xiàn)采用Altera公司的FFT IP Core實(shí)現(xiàn),它是一個(gè)高性能、高度參數(shù)化的快速傅里葉變換(FFT)處理器,實(shí)時(shí)正序輸出變換結(jié)果。采用緩沖突發(fā)模式4輸出引擎結(jié)構(gòu)完成一路4 096點(diǎn)FFT。MTI采用3次相消器即4脈沖對(duì)消法,在FPGA中采用FIFO實(shí)現(xiàn)。與DSP的總線數(shù)據(jù)通信的實(shí)現(xiàn)為FPGA將待傳輸數(shù)據(jù)寫(xiě)到FIFO中同時(shí)向DSP發(fā)送中斷,DSP響應(yīng)中斷后從FIFO中將數(shù)據(jù)讀出。與DSP的鏈路口數(shù)據(jù)通信,無(wú)論是接收鏈路口還是發(fā)送鏈路口均由一個(gè)數(shù)據(jù)緩沖模塊和一個(gè)數(shù)據(jù)拆包/打包模塊組成。表1為FPGA中資源時(shí)間的具體使用,由此看出EP2S60F1020的資源豐富。

在DSPA,DSPD中接收數(shù)據(jù)采用乒乓操作,在接收一組數(shù)據(jù)的同時(shí)對(duì)已接收的數(shù)據(jù)進(jìn)行操作,完成數(shù)據(jù)的定浮轉(zhuǎn)換和MTD。應(yīng)用中用N點(diǎn)傅立葉變換實(shí)現(xiàn)N個(gè)窄帶多普勒濾波器實(shí)現(xiàn)MTD。在DSPB中實(shí)現(xiàn)恒虛警檢測(cè)(CFAR),采用的是兩側(cè)單元平均選大CFAR處理(GO—CFAR),也就是從被檢測(cè)電路單元前后各取一段距離范圍的回波信號(hào),分別計(jì)算前后兩部分的平均值,選取平均值較大的一個(gè)乘以門限因子C作為檢測(cè)門限,與被檢測(cè)單元作比較,如果被檢測(cè)距離單元的回波幅度高于檢測(cè)門限,就可認(rèn)為被檢測(cè)距離單元有目標(biāo)存在。被檢測(cè)單元前后各空出幾個(gè)參考單元避免目標(biāo)本身對(duì)門限值的影響。速度維聚心是指,對(duì)同一距離單元的各個(gè)通道道進(jìn)行幅度峰選,取出其中的最大值作為目標(biāo)所在的速度通道號(hào)。雜波圖的實(shí)現(xiàn),首先建立雜波圖,然后選取零通道數(shù)據(jù)并根據(jù)已知的方位信息及遞歸公式更新雜波圖中數(shù)據(jù)。假設(shè)DSPA和DSPD接收到的數(shù)據(jù)位每周期1 024點(diǎn)的數(shù)據(jù),DSP需要每8周期一滑窗做32脈沖的MTD,CFAR取8個(gè)單元平均選大,則DSP中各功能所占資源如表2所示。

2.2 在脈沖雷達(dá)中的應(yīng)用

功能:完成對(duì)接收的全相參體制的回波信號(hào)的中頻采樣信號(hào)進(jìn)行相關(guān)處理,其中包括DDC、脈沖壓縮、MTI、MTD處理、CFAR、測(cè)角等,最終能夠?qū)?dòng)目標(biāo)進(jìn)行檢測(cè)。

所用到的拓?fù)浣Y(jié)構(gòu):待處理數(shù)據(jù)通過(guò)接插件傳送到FPGA內(nèi)部,通過(guò)FPGA的初步處理,經(jīng)由FPGA與DSPA、DSPD相連的64位數(shù)據(jù)總線傳送到兩片DSP內(nèi)進(jìn)行進(jìn)一步的處理。DSPA將處理完的數(shù)據(jù)經(jīng)過(guò)鏈路口直接傳送到DSPB,DSPD將處理完的數(shù)據(jù)直接傳送到DSPC。DSPC處理完自身數(shù)據(jù)并接收DSPB的數(shù)據(jù)并將數(shù)據(jù)進(jìn)行進(jìn)一步的處理后通過(guò)鏈路口傳送到FPGA輸出。如圖4所示為應(yīng)用所使用的硬件拓?fù)浣Y(jié)構(gòu)。

處理流程:FPGA將接收到的和差兩路信號(hào)分別進(jìn)行DDC以及低通濾波,并對(duì)結(jié)果進(jìn)行整理,和路信號(hào)發(fā)送給DSPA,差路信號(hào)發(fā)送給DSPD。在DSPA和DSPD中分別進(jìn)行和路以及差路信號(hào)的脈壓、MTI,其中MTI可以是根據(jù)命令選做的。DSPA將處理完的信號(hào)傳送給DSPB,DSPD將處理后的數(shù)據(jù)傳送給DSPC,在DSPB和DSPC中進(jìn)行和路以及差路信號(hào)的MTD、MOD、CFAR,同時(shí)DSPC接收DSPB處理后的信號(hào),在DSPC中進(jìn)行和差比商測(cè)角,最后將整理后的結(jié)果輸出到FPGA,由FPGA輸出給雷達(dá)的其它模塊,如圖5所示。

資源使用:在FPGA需要完成的功能為兩路信號(hào)的DDC、低通濾波,以及與DSP的數(shù)據(jù)通信。其中在做DDC時(shí)為了便于測(cè)試在FPGA內(nèi)部有Mat-lab產(chǎn)生的兩組數(shù)據(jù)分別作和差兩路數(shù)據(jù)的內(nèi)部源數(shù)據(jù)。與DSP交互部分無(wú)論是總線傳輸還是鏈路口傳輸均與連續(xù)波雷達(dá)信號(hào)處理實(shí)現(xiàn)方法一致,在此不再贅述(假設(shè)FPGA到DSP傳輸數(shù)據(jù)為1 024個(gè)復(fù)數(shù))。則在FPGA中占用的主要資源如表3所示。

在DSPA和DSPD中以乒乓方式接收FPGA的數(shù)據(jù)完成數(shù)據(jù)的定浮轉(zhuǎn)換,脈沖壓縮和MTI。其中脈沖壓縮采用頻域脈壓的方式,然后對(duì)脈壓結(jié)果作MTI,采用四脈沖對(duì)消。在DSPB和DSPC中要完成數(shù)據(jù)的MTD,MOD,CFAR,最后在DSPC中實(shí)現(xiàn)測(cè)角,最終將目標(biāo)數(shù)據(jù)結(jié)果傳輸給FPGA。這些功能的實(shí)現(xiàn)與連續(xù)波雷達(dá)實(shí)現(xiàn)這些功能方法相同,在此不再贅述。則在DSP中所占用的資源如表4所示。

2.3 幾個(gè)重要模塊的速度

在實(shí)時(shí)信號(hào)處理系統(tǒng)中,系統(tǒng)的速度至關(guān)重要,本文所介紹的平臺(tái)在各個(gè)接口及模塊上均能達(dá)到不錯(cuò)的速率。

(1)FPGA與DSP總線傳輸速率。

在本系統(tǒng)中總線傳輸可以采取流水協(xié)議,零等待周期的配置,這樣總線速度可以達(dá)到DSP SCLK的速度,在本系統(tǒng)中為50 MHz×64 bit的速率。

(2)FPGA與DSP鏈路口傳輸速率。

在本系統(tǒng)中鏈路口采取四位模式,則鏈路口可以配置成150 MHz,300 MHz,400 MHz,600 MHz。經(jīng)過(guò)測(cè)試,F(xiàn)PGA與DSP之間的鏈路口速度可以達(dá)到400 MHz×4 bit的完美無(wú)錯(cuò)傳輸。

(3)DSP與DSP鏈路口傳輸速率。

經(jīng)過(guò)測(cè)試,DSP與DSP之間的鏈路口速度可以達(dá)到600 MHz×4 bit的無(wú)錯(cuò)傳輸。以上幾個(gè)速率為數(shù)據(jù)傳輸十分重要的幾個(gè)接口的速度,通過(guò)測(cè)試數(shù)據(jù)可知,系統(tǒng)可以達(dá)到較高的,完全可以滿足信號(hào)實(shí)時(shí)性的要求。

3 結(jié)束語(yǔ)

針對(duì)當(dāng)前FPGA+DSP的信號(hào)處理平臺(tái)現(xiàn)狀,提出一種通用的硬件結(jié)構(gòu),該結(jié)構(gòu)不僅將兩種處理器的優(yōu)點(diǎn)集于一身,兼顧速度和靈活性而且可以應(yīng)用在不同雷達(dá)信號(hào)處理系統(tǒng)中,具有很強(qiáng)的通用性。分別介紹了此平臺(tái)在連續(xù)波雷達(dá)以及脈沖雷達(dá)中的一種應(yīng)用,并且這些方法已經(jīng)成功應(yīng)用于雷達(dá)信號(hào)處理機(jī)中。除了文中列舉的方法外由于本結(jié)構(gòu)硬件連通的靈活性,本結(jié)構(gòu)可以根據(jù)需要應(yīng)用于各種雷達(dá)處理系統(tǒng)中。