ARM公司于2008年11月12日發(fā)布了ARM Cortex微控制器" title="微控制器">微控制器軟件接口標(biāo)準(zhǔn)(CMSIS:Cortex Microcon-troller Software Interface Standard)。CMSIS是獨(dú)立于供應(yīng)商的Cortex-M處理器系列硬件抽象層,為芯片廠商" title="芯片廠商">芯片廠商和中間件供應(yīng)商提供了連續(xù)的、簡(jiǎn)單的處理器軟件接口,簡(jiǎn)化了軟件復(fù)用,降低了Cortex-M3" title="Cortex-M3">Cortex-M3上操作系統(tǒng)的移植難度,并縮短了新入門(mén)的微控制器開(kāi)發(fā)者的學(xué)習(xí)時(shí)間和新產(chǎn)品的上市時(shí)間。

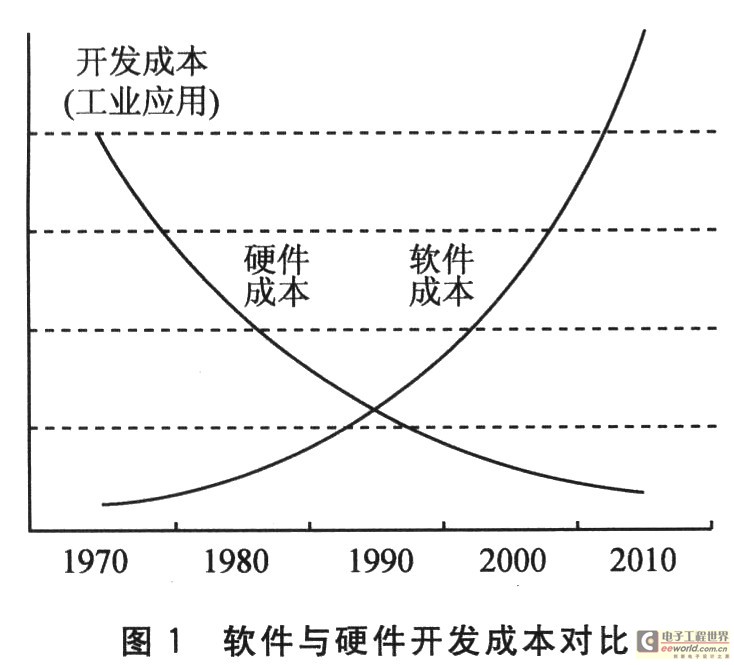

根據(jù)近期的調(diào)查研究,軟件開(kāi)發(fā)" title="軟件開(kāi)發(fā)">軟件開(kāi)發(fā)已經(jīng)被嵌入式行業(yè)公認(rèn)為最主要的開(kāi)發(fā)成本" title="開(kāi)發(fā)成本">開(kāi)發(fā)成本。圖1為近年來(lái)軟件開(kāi)發(fā)與硬件開(kāi)發(fā)成本對(duì)比圖。因此,ARM與Atmel、IAR、Keil、hami-nary Micro、Micrium、NXP、SEGGER和ST等諸多芯片和軟件廠商合作,將所有Cortex芯片廠商產(chǎn)品的軟件接口標(biāo)準(zhǔn)化,制定了CMSIS標(biāo)準(zhǔn)。此舉意在降低軟件開(kāi)發(fā)成本,尤其針對(duì)新設(shè)備項(xiàng)目開(kāi)發(fā),或者將已有軟件移植到其他芯片廠商提供的基于Cortex處理器的微控制器的情況。有了該標(biāo)準(zhǔn),芯片廠商就能夠?qū)⑺麄兊馁Y源專注于產(chǎn)品外設(shè)" title="外設(shè)">外設(shè)特性的差異化,并且消除對(duì)微控制器進(jìn)行編程時(shí)需要維持的不同的、互相不兼容的標(biāo)準(zhǔn)的需求,從而達(dá)到降低開(kāi)發(fā)成本的目的。

1 基于CMSIS標(biāo)準(zhǔn)的軟件架構(gòu)

如圖2所示,基于CMSIS標(biāo)準(zhǔn)的軟件架構(gòu)主要分為以下4層:用戶應(yīng)用層、操作系統(tǒng)及中間件接口層、CMSIS層、硬件寄存器層。其中CMSIS層起著承上啟下的作用:一方面該層對(duì)硬件寄存器層進(jìn)行統(tǒng)一實(shí)現(xiàn),屏蔽了不同廠商對(duì)Cortex-M系列微處理器核內(nèi)外設(shè)寄存器的不同定義;另一方面又向上層的操作系統(tǒng)及中間件接口層和應(yīng)用層提供接口,簡(jiǎn)化了應(yīng)用程序開(kāi)發(fā)難度,使開(kāi)發(fā)人員能夠在完全透明的情況下進(jìn)行應(yīng)用程序開(kāi)發(fā)。也正是如此,CMSIS層的實(shí)現(xiàn)相對(duì)復(fù)雜。

CMSIS層主要分為3部分。

①核內(nèi)外設(shè)訪問(wèn)層(CPAL):由ARM負(fù)責(zé)實(shí)現(xiàn)。包括對(duì)寄存器地址的定義,對(duì)核寄存器、NVIC、調(diào)試子系統(tǒng)的訪問(wèn)接口定義以及對(duì)特殊用途寄存器的訪問(wèn)接口(如CONTROL和xPSR)定義。由于對(duì)特殊寄存器的訪問(wèn)以內(nèi)聯(lián)方式定義,所以ARM針對(duì)不同的編譯器統(tǒng)一用_INLINE來(lái)屏蔽差異。該層定義的接口函數(shù)均是可重入的。

②中間件訪問(wèn)層(MWAL):由ARM負(fù)責(zé)實(shí)現(xiàn),但芯片廠商需要針對(duì)所生產(chǎn)的設(shè)備特性對(duì)該層進(jìn)行更新。該層主要負(fù)責(zé)定義一些中間件訪問(wèn)的API函數(shù),例如為T(mén)CP/IP協(xié)議棧、SD/MMC、USB協(xié)議以及實(shí)時(shí)操作系統(tǒng)的訪問(wèn)與調(diào)試提供標(biāo)準(zhǔn)軟件接口。該層在1.1標(biāo)準(zhǔn)中尚未實(shí)現(xiàn)。

③設(shè)備外設(shè)訪問(wèn)層(DPAL):由芯片廠商負(fù)責(zé)實(shí)現(xiàn)。該層的實(shí)現(xiàn)與CPAL類似,負(fù)責(zé)對(duì)硬件寄存器地址以及外設(shè)訪問(wèn)接口進(jìn)行定義。該層可調(diào)用CPAL層提供的接口函數(shù),同時(shí)根據(jù)設(shè)備特性對(duì)異常向量表進(jìn)行擴(kuò)展,以處理相應(yīng)外設(shè)的中斷請(qǐng)求。

2 CMSIS規(guī)范

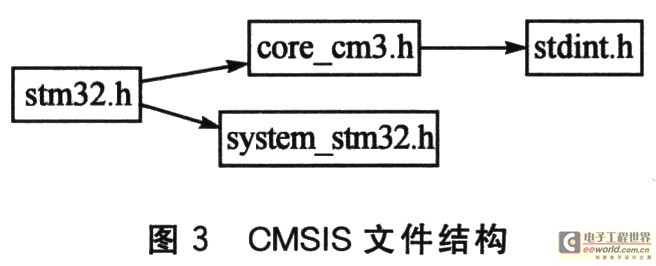

(1)文件結(jié)構(gòu)

CMSIS的文件結(jié)構(gòu)如圖3所示(以STM32為例)。其中stdint.h包括對(duì)8位、16位、32位等類型指示符的定義,主要用來(lái)屏蔽不同編譯器之前的差異。core_cm3.h和core_cm3.C中包括Cortex_M3核的全局變量聲明和定義,并定義一些靜態(tài)功能函數(shù)。system_

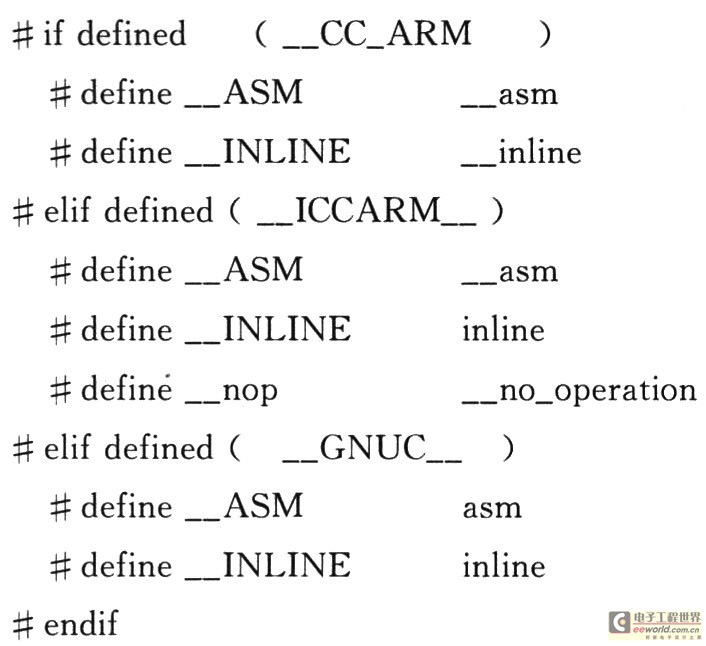

(2)工具鏈

CMSIS支持目前嵌入式開(kāi)發(fā)的三大主流工具鏈,即ARM ReakView(armcc)、IAR EWARM(iccarm)以及GNU工具鏈(gcc)。通過(guò)在core_cm3.C中的如下定義,來(lái)屏蔽一些編譯器內(nèi)置關(guān)鍵字的差異。

這樣,CPAL中的功能函數(shù)就可以被定義成靜態(tài)內(nèi)聯(lián)類型(static_INLINE),實(shí)現(xiàn)編譯優(yōu)化。

(3)中斷異常

CMSIS對(duì)異常和中斷標(biāo)識(shí)符、中斷處理函數(shù)名以及中斷向量異常號(hào)都有嚴(yán)格的要求。異常和中斷標(biāo)識(shí)符需加后綴_IRQn,系統(tǒng)異常向量號(hào)必須為負(fù)值,而設(shè)備的中斷向量號(hào)是從0開(kāi)始遞增,具體的定義如下所示(以STM32為例):

CMSIS對(duì)系統(tǒng)異常處理函數(shù)以及普通的中斷處理函數(shù)名的定義也有所不同。系統(tǒng)異常處理函數(shù)名需加后綴_Handler,而普通中斷處理函數(shù)名則加后綴_IRQHandler。這些異常中斷處理函數(shù)被定義為weak屬性,以便在其他的文件中重新實(shí)現(xiàn)時(shí)不出現(xiàn)重復(fù)定義的錯(cuò)誤。這些處理函數(shù)的地址用來(lái)填充中斷異常向量表,并在啟動(dòng)代碼中給以聲明,例如:NMI_Handler、MemManage_Handler、SysTick_Handler、WWDG_IRQHandler等。

(4)數(shù)據(jù)類型

CMSIS對(duì)數(shù)據(jù)類型的定義是在stdint.h中完成的,對(duì)核寄存器結(jié)構(gòu)體的定義是在core_cm3.h中完成的,寄存器的訪問(wèn)權(quán)限是通過(guò)相應(yīng)的標(biāo)識(shí)來(lái)指示的。CMSIS定義以下3種標(biāo)識(shí)符來(lái)指定訪問(wèn)權(quán)限:_I(volatile const)、_O(volatile)和_IO(volatile)。其中_I用來(lái)指定只讀權(quán)限,_O指定只寫(xiě)權(quán)限,_IO指定讀寫(xiě)權(quán)限。

(5)調(diào) 試

嵌入式軟件開(kāi)發(fā)中的一個(gè)基本需求就是能通過(guò)終端來(lái)輸出調(diào)試信息,一般可通過(guò)2種方式實(shí)現(xiàn):一種是使用串口線連接板上的UART和PC上的COM口,通過(guò)PC上的超級(jí)終端來(lái)查看調(diào)試信息;另一種則是采用半主機(jī)機(jī)制,但有可能不被所用的工具鏈支持。基于Cortex-M3核的軟件調(diào)試突破了這樣的限制,Cortex-M3內(nèi)核提供了一個(gè)ITM(Instrumentation Trace Macrocell)接口,通過(guò)SWV(Serial Wire Viewer)可調(diào)試由SWO引腳接收到的ITM數(shù)據(jù)。ITM實(shí)現(xiàn)了32個(gè)通用的數(shù)據(jù)通道,基于這樣的實(shí)現(xiàn),CMSIS規(guī)定用通道0作為終端來(lái)輸出調(diào)試信息,通道31用于操作系統(tǒng)的輸出調(diào)試(特權(quán)模式訪問(wèn))。在core_cm3.h中定義了ITM_SendChar()函數(shù),因此可通過(guò)調(diào)用該函數(shù)來(lái)重寫(xiě)fputc,以在應(yīng)用程序中通過(guò)printf打印調(diào)試信息,并可通過(guò)ITM Viewer查看這些調(diào)試信息。有了這樣的實(shí)現(xiàn),嵌入式軟件開(kāi)發(fā)者就可以在不配置串口和使用終端調(diào)試軟件的情況下輸出調(diào)試信息,在一定程度上減少了工作量。

(6)安全機(jī)制

在嵌入式軟件開(kāi)發(fā)過(guò)程中,代碼的安全性和健壯性一直是開(kāi)發(fā)人員所關(guān)注的,因此CMSIS在這方面也作出了努力,所有的CMSIS代碼都基于MISRA-C2004(Motor Industry Software Reliability Association forthe C programming language)標(biāo)準(zhǔn)。MIRSA-C 2004制定了一系列安全機(jī)制用來(lái)保證驅(qū)動(dòng)層軟件的安全性,是嵌入式行業(yè)都應(yīng)遵循的標(biāo)準(zhǔn)。對(duì)于不符合MISRA標(biāo)準(zhǔn)的,編譯器會(huì)提示錯(cuò)誤或警告,這主要取決于開(kāi)發(fā)者所使用的工具鏈。

3 基于CMSIS標(biāo)準(zhǔn)的代碼實(shí)現(xiàn)

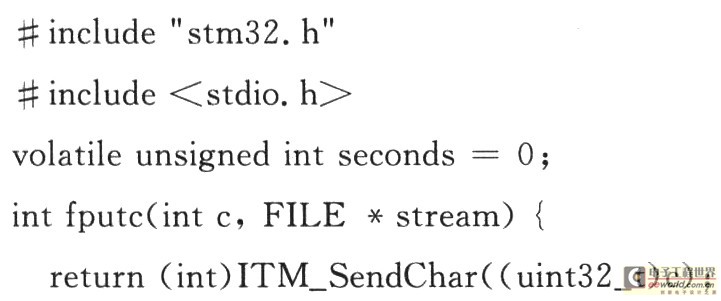

CMSIS降低了代碼開(kāi)發(fā)的難度,為了更好地詮釋這一點(diǎn),下面以一個(gè)基于STM32微處理器的簡(jiǎn)單例子來(lái)說(shuō)明。代碼實(shí)現(xiàn)如下:

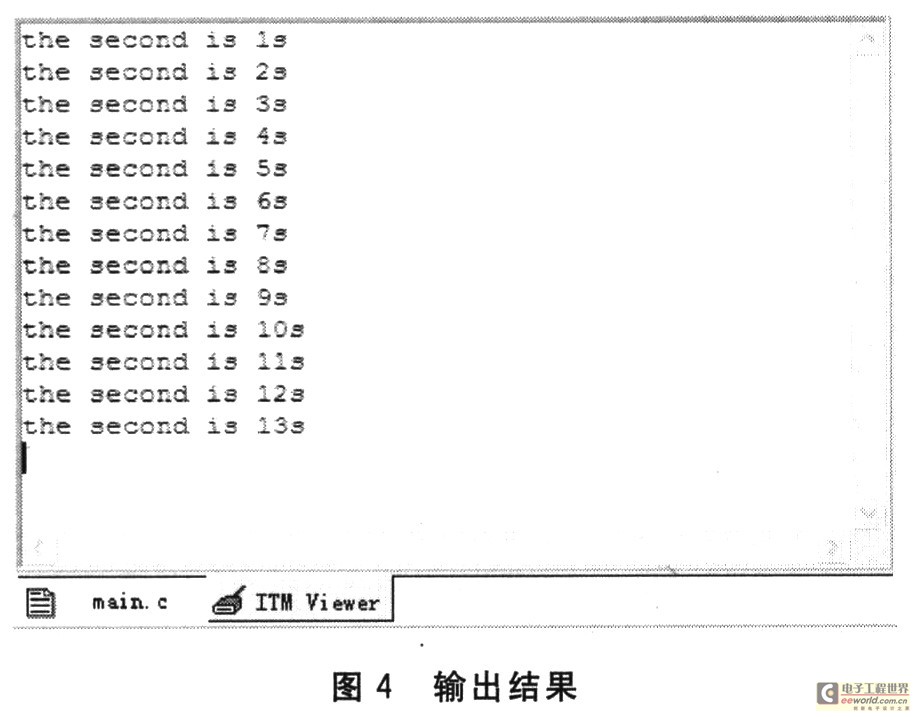

可以看到用戶程序中僅需短短的幾行代碼就實(shí)現(xiàn)了定時(shí)器的功能,每隔1 S報(bào)數(shù)1次,并可通過(guò)ITM窗口查看輸出的調(diào)試信息。其中SystemInit()用來(lái)初始化時(shí)鐘,SysTick_Config()用來(lái)配置系統(tǒng)定時(shí)器,而SysTick_Han-dler()用來(lái)處理系統(tǒng)時(shí)鐘異常,該異常每1 ms發(fā)生1次。由于重寫(xiě)了fputc(),所以可通過(guò)printf()函數(shù)將調(diào)試信息打印到ITM窗口上,輸出結(jié)果如圖4所示。

結(jié) 語(yǔ)

本文闡述了基于CMSIS標(biāo)準(zhǔn)的軟件架構(gòu)、規(guī)范,并通過(guò)一個(gè)實(shí)例更加清晰地解讀了CMSIS作為一個(gè)新的基于Cortex-M核處理器系列的軟件開(kāi)發(fā)標(biāo)準(zhǔn)所具有的巨大潛力。它不僅降低了軟件開(kāi)發(fā)的難度,更減少了軟件開(kāi)發(fā)的成本。因此,工程師盡早掌握CMSIS標(biāo)準(zhǔn),對(duì)進(jìn)行基于Cortex-M3處理器的軟件開(kāi)發(fā)會(huì)大有幫助。