摘要:為提高8B/10B編解碼的工作速度和簡(jiǎn)化邏輯方法,提出一種基于FPGA的8B/10B編解碼系統(tǒng)設(shè)計(jì)方案。與現(xiàn)有的8B/10B編解碼方案相比,該方案是一種利用FPGA實(shí)現(xiàn)8B/lOB編解碼的模塊方法,接收模塊在收到外部發(fā)送的并行數(shù)據(jù)時(shí),通過直接查找映射的方法轉(zhuǎn)換成利于傳輸?shù)拇行盘?hào)。串行信號(hào)經(jīng)串并行轉(zhuǎn)換模塊,將數(shù)據(jù)經(jīng)10B/8B解碼模塊解碼還原成原始數(shù)據(jù)。為了更好實(shí)現(xiàn)數(shù)據(jù)的傳輸,系統(tǒng)加入了極性偏差RD控制。結(jié)果表明,該8B/10B編解碼系統(tǒng)設(shè)計(jì)方案?jìng)鬏敂?shù)據(jù)穩(wěn)定,滿足設(shè)計(jì)要求。

關(guān)鍵詞:串行數(shù)據(jù)傳輸;8B/lOB編解碼;極性偏差(RD);VHDL

隨著通信技術(shù)的發(fā)展,在復(fù)雜的電磁環(huán)境下正確傳輸數(shù)據(jù)受到人們的關(guān)注,因此性能優(yōu)異的光纖通訊越來越受到青睞,而誤碼率要滿足設(shè)計(jì)需求,關(guān)鍵在于串行傳輸數(shù)據(jù)所選用的編碼方法。

8B/10B編解碼技術(shù)是主流傳輸標(biāo)準(zhǔn)的編解碼技術(shù)之一,廣泛應(yīng)用于高速串行標(biāo)準(zhǔn)中,例如光纖通道1、PCI-Express、串行ATA、1394b等。8B/10B編解碼技術(shù)設(shè)定傳輸數(shù)據(jù)流擁有連續(xù)“l”或連續(xù)“0”不能超過5個(gè),保證傳輸?shù)闹绷鞒煞纸咏?,基線漂移減至最小,避免因接收端時(shí)鐘漂移或同步丟失而引起數(shù)據(jù)丟失。8B/10B編碼方法具有DC補(bǔ)償功能,能夠保證鏈路中不隨著時(shí)間推移而出現(xiàn)DC偏移。這使得信號(hào)的轉(zhuǎn)換不會(huì)因電壓位階的關(guān)系造成信號(hào)錯(cuò)誤。8B/10B編碼采用冗余方式,將8位的數(shù)據(jù)和一些特殊字符按照特定的規(guī)則編碼成10位的數(shù)據(jù),根據(jù)這些規(guī)則,能檢測(cè)出傳輸過程中發(fā)生錯(cuò)誤的信息。通過以上各種措施,8B/10B編碼方式能夠確保數(shù)據(jù)在高速傳輸過程中正確傳送和識(shí)別。

因此這里提出一種利用FPGA實(shí)現(xiàn)8B/lOB編解碼系統(tǒng)設(shè)計(jì)方案。

1 系統(tǒng)設(shè)計(jì)總體設(shè)計(jì)

1.1 系統(tǒng)設(shè)計(jì)結(jié)構(gòu)

該系統(tǒng)是基于FPGA設(shè)計(jì)的8B/10B編解碼器,首先系統(tǒng)接收外部發(fā)送的8B并行數(shù)據(jù),在8B/10B編碼模塊中完成編碼后,再通過10B數(shù)據(jù)并串轉(zhuǎn)換模塊生成利于傳輸?shù)?0B串行信號(hào)。這樣8B/10B編碼模塊和10B并串轉(zhuǎn)換模塊構(gòu)成8B/lOB編碼器。編碼端發(fā)送的10B串行信號(hào)經(jīng)過傳輸線路傳輸后被lOB數(shù)據(jù)串并行轉(zhuǎn)換模塊所接收,轉(zhuǎn)換完成的10B并行數(shù)據(jù)再通過1OB/8B解碼模塊解碼完成后即是還原后的原始數(shù)據(jù)。這樣lOB串行數(shù)據(jù)到10B并行數(shù)據(jù)轉(zhuǎn)換模塊和1OB/8B解碼模塊就構(gòu)成了1OB/8B解碼器。圖1為系統(tǒng)設(shè)計(jì)框圖。

1.2 設(shè)計(jì)方案

8B/10B編解碼器通常有兩種設(shè)計(jì)方法:一種是用查找表直接將8位信號(hào)映射成lO位信號(hào),該方法是采用存儲(chǔ)器存儲(chǔ)所有可能出現(xiàn)的碼組,再將輸入碼組轉(zhuǎn)換為存儲(chǔ)地址,找出對(duì)應(yīng)的編解碼。這種方法邏輯簡(jiǎn)單,開發(fā)時(shí)間很短;另一種是通過邏輯運(yùn)算直接實(shí)現(xiàn)編解碼功能,其優(yōu)點(diǎn)是明顯減小內(nèi)部使用面積,但邏輯關(guān)系復(fù)雜。從系統(tǒng)優(yōu)化考慮把1節(jié)8 bit字節(jié)拆分成3 bit和5 bit,然后在極性偏差RD(running dis-

parity)控制器的控制下以并列方式編解碼。這種方法的組合邏輯實(shí)現(xiàn)可以簡(jiǎn)化碼表,減小電路板的面積,有效提高編碼工作速度,同時(shí)由于電路板的面積減小,功耗顯著降低。這里采用第1種方法,同時(shí)結(jié)合第2種方法的設(shè)計(jì)思路。

2 系統(tǒng)軟件程序設(shè)計(jì)

2.1 8B/10B編碼模塊

2.2 10B并串轉(zhuǎn)換模塊

該模塊主要完成10B并行數(shù)據(jù)到lOB串行數(shù)據(jù)的轉(zhuǎn)換功能,lOB串行數(shù)據(jù)的數(shù)據(jù)格式為:l bit低電平起始位、10 bit數(shù)據(jù)位、l bit高電平停止位、2 bit高電平數(shù)據(jù)空碼。生成一個(gè)完整的10B串行數(shù)據(jù)包含4個(gè)狀態(tài),生成起始位、轉(zhuǎn)換10 bit數(shù)據(jù)位、生成停止位、生成數(shù)據(jù)空碼。

2.3 10B串并行轉(zhuǎn)換模塊

該模塊主要完成10B串行信號(hào)到10B并行信號(hào)的轉(zhuǎn)換,10B信號(hào)的串并轉(zhuǎn)換模塊主要是要從14 bit的串行信號(hào)中挑出10 bit的有效數(shù)據(jù)位,過程中首先要判斷起始位(而不是任意一個(gè)低電平),然后采集10 bit的有效數(shù)據(jù)位,完成后等待下一個(gè)起始位。程序同樣是通過狀態(tài)機(jī)來實(shí)現(xiàn)整個(gè)過程的流通。

2.4 10B/8B解碼模塊

解碼模塊根據(jù)系統(tǒng)要求可分為6B/5B解碼模塊、4B/3B解碼模塊和誤碼檢測(cè)模塊。解碼模塊相對(duì)編碼模塊而言邏輯過程要簡(jiǎn)單的多,該模塊首先將10 bit信號(hào)分割成4 bit和6bit兩部分(高低位必須和編碼端對(duì)應(yīng)),然后4 bit和6 bit數(shù)據(jù)根據(jù)編碼列表分別解碼成3 bit和5 bit,在解碼過程中判斷是否有誤碼產(chǎn)生有則報(bào)錯(cuò),無則并行輸出。圖4給出了1OB/8B解碼模塊的邏輯框圖和程序設(shè)計(jì)流程如圖4所示。

3 系統(tǒng)仿真結(jié)果分析

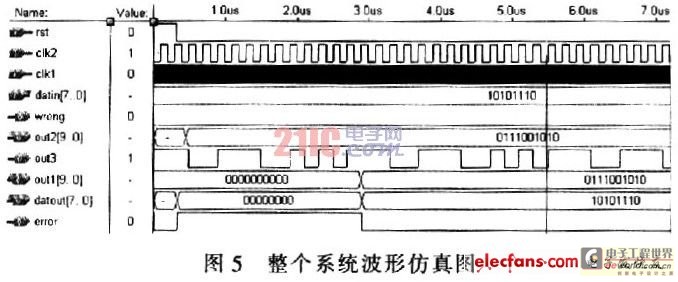

待完成整套的8B/10B編解碼器模塊連接后,對(duì)整體程序進(jìn)行仿真驗(yàn)證,其結(jié)果如圖5所示,其中clkl為編碼和解碼模塊的時(shí)鐘引腳,elk2為1OB串并轉(zhuǎn)換和10B并串轉(zhuǎn)換模塊的時(shí)鐘引腳,rst為整個(gè)系統(tǒng)的異步復(fù)位引腳,datin[7..0]為待傳輸?shù)? bit并行數(shù)據(jù),datout[7..0]為傳輸完成的8 bit并行數(shù)據(jù),error為解碼端誤碼檢測(cè)報(bào)警引腳,wrong為編碼端出錯(cuò)報(bào)警引腳。還有3個(gè)引腳是系統(tǒng)不必要的但是為方便調(diào)試而引出的,outl[9..0]為10B串并轉(zhuǎn)換完成的10B并行信號(hào),out3為10B并串轉(zhuǎn)換完成的10B串行信號(hào),out2[9..0]為8B/10B編碼完成的10B并行信號(hào)。

由圖5可看出:輸入數(shù)據(jù)datin為“10101110”,經(jīng)過8B/10B編碼完成的數(shù)據(jù)out2為“0111001010”,8B/10B編碼模塊出錯(cuò)報(bào)警引腳為“0”,10B并串轉(zhuǎn)換輸出的串行數(shù)據(jù)out3為“00111001010111”,10B串并轉(zhuǎn)換輸出的并行數(shù)據(jù)outl為“0111001010”,1OB/8B解碼完成的輸出數(shù)據(jù)datout為“10101llO”,結(jié)合整個(gè)系統(tǒng)的工作過程和編碼列表不難看出系統(tǒng)正確的完成了編碼和解碼的功能,能滿足設(shè)計(jì)任務(wù)的需要。

4 結(jié)束語(yǔ)

本文提出一種利用FPGA實(shí)現(xiàn)8B/10B編碼和10B/8B解碼設(shè)計(jì)的方法,介紹了8B/10B編解碼技術(shù),實(shí)現(xiàn)了8B/10B的正常編解碼和接口串并、并串轉(zhuǎn)換的設(shè)計(jì),在FPGA的控制下能實(shí)現(xiàn)數(shù)據(jù)的傳輸,滿足了實(shí)際設(shè)備中所提出的要求。