關(guān)鍵字:工業(yè)電機 最大效率

RIO架構(gòu)目前已被用于多款系統(tǒng)中,如EUROelectronics等公司的系統(tǒng)。借助該架構(gòu),從產(chǎn)品原型設(shè)計到最終機械設(shè)備完成,EUROelectronics只用了3個月的時間。

縮短機械設(shè)計時間

無刷DC和永磁同步AC電機(PMSM)二者通常組成無刷DC電機(BLDC),其集成式控制非常復(fù)雜,是一個挑戰(zhàn)。許多機械制造商都缺乏構(gòu)建嵌入式控制器方面的軟硬件設(shè)計經(jīng)驗,難以讓嵌入式控制器在各種類型的模擬和數(shù)字傳感器上實時執(zhí)行閉環(huán)控制。

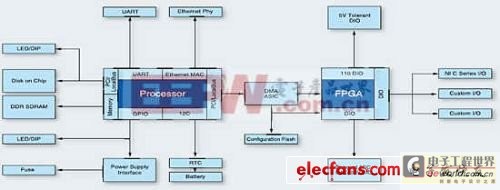

為了縮短嵌入式機械制造商的最終設(shè)計時間,本文介紹的方案在CompactRIO產(chǎn)品中集成了某種形式的RIO架構(gòu)。這種基于FPGA的配置包括基于Virtex-5 LX85到Spartan-3的系統(tǒng),以及基于Virtex-II 1M門的背板,配合基于PowerPC 603e的處理器,能夠滿足多種頻率和性能需求,如圖1所示。

圖1 在CompactRIO產(chǎn)品中集成了某種形式的RIO架構(gòu)

在RIO框架中集成配置軟件實用程序和動態(tài)I/O重構(gòu)功能可節(jié)約設(shè)置時間,而且終端應(yīng)用編程人員和數(shù)字設(shè)計工程師還能重復(fù)使用有關(guān)資源。配置軟件能自動檢測系統(tǒng)中安裝的定制硬件。I/O外設(shè)的集成式診斷測試可確保I/O器件正常工作。

如果不安裝I/O電路,驅(qū)動程序軟件及相關(guān)API不能適當(dāng)執(zhí)行或返回具體器件的故障,就會出現(xiàn)問題。為解決上述問題,軟件開發(fā)人員通常會創(chuàng)建模擬子例程,臨時替代應(yīng)用中的I/O電路代碼。這種方法難以立即開始應(yīng)用開發(fā),而且?guī)缀醪荒苷{(diào)試代碼。RIO中間件驅(qū)動程序架構(gòu)包括相關(guān)功能,可將模擬代碼直接集成到函數(shù)驅(qū)動程序中,從而簡化代碼的重復(fù)使用與故障調(diào)試。

圖2 嵌入式中間件軟件設(shè)計分級圖

圖2所示為嵌入式中間件軟件設(shè)計分級圖。這種中間件驅(qū)動程序和系統(tǒng)服務(wù)在成千上萬種已經(jīng)部署的機械設(shè)計應(yīng)用中都證實了自己的功能。并行和多線程安全型嵌入式中間件驅(qū)動程序是RIO的有機組成部分。機械制造商可同時從多個線程調(diào)用多線程安全型和可再入函數(shù),同時還能確保正常工作,避免阻塞現(xiàn)象,這對并行代碼的編寫和性能優(yōu)化都是非常重要的特性。不具備可再入執(zhí)行功能的驅(qū)動程序會影響性能,更糟的是還會導(dǎo)致崩潰。代碼必須等其他線程使用完每個函數(shù)后才能訪問函數(shù)。可再入性可避免代碼中任何不必要的依賴性。

BLDC和PMSM的定子纏繞方式有別。BLDC的定子旋轉(zhuǎn)時其纏繞方式可生成梯形反電勢電壓,而PMSM的電壓則為正弦曲線。

BLDC的成本高于AC電感電機,但在用高級算法控制情況下其節(jié)能性和性能更高。此外,BLDC還具有較高的可擴展性,能滿足極高功率和極高速應(yīng)用的需求。

關(guān)鍵字:工業(yè)電機 最大效率

顧名思義,無刷DC電機工作時是不需要電刷的。這就是說,電刷所起的轉(zhuǎn)換作用必須以電子方式實現(xiàn)。定子線圈順序加電,BLDC電機就能轉(zhuǎn)動了。要計算在某一時刻哪個線圈加電,必須了解定子的位置,這通常可通過在定子中嵌入的三個霍爾效應(yīng)感應(yīng)器來檢測。綜合這三個感應(yīng)器信號,控制電子產(chǎn)品可確定轉(zhuǎn)換的確切順序。

由于無刷電機的轉(zhuǎn)子使用永磁而非無源線圈,其本身提供的功率相對于尺寸、重量相當(dāng)?shù)碾姼须姍C而言要高。不過,高效運行的關(guān)鍵在于FPGA控制器。FPGA算法控制的效率高于微處理器。可以使用多種控制系統(tǒng)算法,包括梯形、正弦和場定向算法(FOC)。

梯形或六步控制是最簡單同時也是性能最差的方法。就六步轉(zhuǎn)換的每一步而言,電機驅(qū)動會在兩個線圈之間形成電流通路,而第三個電機不連接。不過,轉(zhuǎn)矩紋波會產(chǎn)生震動、噪聲和機械磨損,并大幅降低伺服性能。

FOC也稱作矢量控制,能在較高電機速度下提高效率,在正弦控制技術(shù)基礎(chǔ)上更進(jìn)一步。FOC相對于其他控制技術(shù)而言,單位功率輸入可實現(xiàn)最大轉(zhuǎn)矩,而且在負(fù)載變化時能精確控制速度,響應(yīng)速度快。FOC技術(shù)通過完美保持定子和轉(zhuǎn)子磁通,即便在瞬態(tài)過程也能確保最佳效率。

探討FOC

了解FOC工作原理的方法之一是在腦海中形成一幅完整的坐標(biāo)參考系轉(zhuǎn)換過程畫面。假設(shè)從定子角度來設(shè)想AC電機的工作,可以看到,當(dāng)正弦輸入電流施加到定子時,時變信號會產(chǎn)生旋轉(zhuǎn)磁通。轉(zhuǎn)子速度與旋轉(zhuǎn)磁通矢量存在一種函數(shù)關(guān)系。

現(xiàn)在,再從電機內(nèi)部來看,假設(shè)以等同于定子電流產(chǎn)生的旋轉(zhuǎn)磁通矢量的速度沿離心器運行,在穩(wěn)定狀態(tài)下從這個角度來觀察電機,可發(fā)現(xiàn)定子電流好像為常量,且旋轉(zhuǎn)磁通矢量為固定的。歸根結(jié)底,希望控制定子電流,以獲得所需的轉(zhuǎn)子電流。通過坐標(biāo)參考系轉(zhuǎn)換,可通過簡單的PI控制回路控制定子電流,如DC值。

FOC算法在后臺發(fā)揮作用,消除時間和速度的依賴性,能直接獨立控制磁通量和轉(zhuǎn)矩。通過數(shù)學(xué)公式(Clarke及Park變換),可將電機的電子狀態(tài)轉(zhuǎn)換為時間不變性旋轉(zhuǎn)兩軸坐標(biāo)系。

空間矢量脈沖寬度調(diào)制(PWM)的高效控制電力電子技術(shù)能最大化電機電源電壓的利用率,同時最小化諧波損耗。但諧波會在電機鐵芯中形成消耗能量的渦流,從而大幅降低電機效率。

最重要的是,設(shè)計人員既可對AC電感與無刷DC電機采用FOC技術(shù),以提高其效率和性能,也可將該技術(shù)應(yīng)用于現(xiàn)有電機,升級控制系統(tǒng)。事實上,設(shè)計人員可通過FOC等矢量控制技術(shù)來改進(jìn)AC電感電機,實現(xiàn)類似于伺服電機的性能。

FPGA解決FOC面臨的挑戰(zhàn)

實施FOC需要功能強大的計算器件。針對上述要求,F(xiàn)PGA無疑是電機控制的最佳選擇。FOC系統(tǒng)必須持續(xù)以10kHz~100kHz的速度重復(fù)計算矢量控制算法。此外,還需在不影響控制算法時序的情況下并行執(zhí)行高速PWM輸出等其他IP模塊。利用FPGA自身的并行執(zhí)行功能和硬件可靠性,F(xiàn)PGA能以高達(dá)數(shù)十萬赫茲的回路速度執(zhí)行控制算法,而且還有余力來處理通信,為主機微處理器上的用戶接口應(yīng)用提供數(shù)據(jù)。此外,F(xiàn)PGA還具有可重構(gòu)性,因此客戶能隨時根據(jù)需要調(diào)整控制算法。

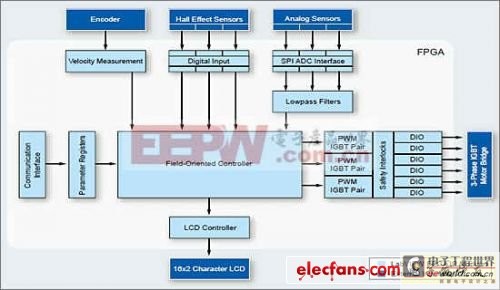

圖3所示為FOC實施方案的系統(tǒng)圖。除實際控制算法之外,F(xiàn)PGA還并行執(zhí)行IP模塊,以讀取3個霍爾效應(yīng)傳感器、1個編碼器以及3個其它模擬傳感器的值,同時生成PWM信號驅(qū)動外部電子器件給電機供電。如欲與主機處理器及簡單用戶接口通信,可并行執(zhí)行其他IP模塊。

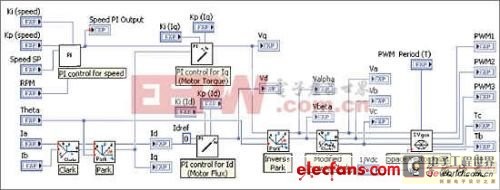

圖4所示為基于FPGA的FOC算法實施LabVIEW FPGA的情況。Clarke變換將120°相移三軸坐標(biāo)系(Ia, Ib, Ic)轉(zhuǎn)變?yōu)閮奢S直角坐標(biāo)系(Ia, Ib)。接著,Park變換將固定的坐標(biāo)系(Ia, Ib)轉(zhuǎn)換為去耦兩軸旋轉(zhuǎn)坐標(biāo)系(Id和Iq),簡單的PI控制器就能控制上述旋轉(zhuǎn)坐標(biāo)。FOC系統(tǒng)利用逆變換(Park變換和Clarke變換)將其還原到定子線圈的固定AC三相坐標(biāo)系。

圖4 基于FPGA的FOC算法實施LabVIEW FPGA的情況

在評估控制系統(tǒng)的升級時,機械設(shè)計人員通常會低估耗電成本問題,而從機電的整個生命周期角度來看,耗電成本往往比硬件購置成本高很多。NI致力于借助基于賽靈思FPGA技術(shù)的商用硬件解決方案成品推出具有高計算性能的高靈活性嵌入式控制器。通過二者的強強聯(lián)合,能滿足客戶最苛刻的要求,即FOC性能要求。