0 引言

隨著計算機(jī)技術(shù)與通信技術(shù)的持續(xù)發(fā)展,人們對高帶寬需求不斷增加,接入DDN(Digital Data Network)網(wǎng)、幀中繼網(wǎng)等高速通信網(wǎng)的應(yīng)用也越來越普遍。E1是我國電信傳輸網(wǎng)一次群使用的傳輸標(biāo)準(zhǔn),速率是2.048 Mb/s。實(shí)現(xiàn)多路接口與E1協(xié)議的相互轉(zhuǎn)換,將可以把多種設(shè)備同時連接至高速的E1線路。本文基于FPGA(Field Programmable Gate Array)、嵌入式微處理器設(shè)計了一個多路接口與E1的協(xié)議轉(zhuǎn)換器,實(shí)現(xiàn)RS 232,RS 449,V.35等接口數(shù)據(jù)在E1線路上的高速傳輸。

1 系統(tǒng)原理

1.1 系統(tǒng)描述

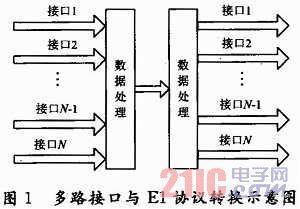

多路接口與E1協(xié)議轉(zhuǎn)換示意圖如圖1所示。在發(fā)送端,將多路接口數(shù)據(jù)按照一定順序合并成一路符合E1協(xié)議的數(shù)據(jù)在E1信道上進(jìn)行傳輸,在接收端,將接收到的E1信號再按發(fā)送端順序分成多路接口數(shù)據(jù)。

1.2 多路接口數(shù)據(jù)映射到E1幀的方法

E1是一種典型的時分復(fù)用結(jié)構(gòu),一個E1時分復(fù)用幀劃分為32個相等的時隙,編號為CH0~CH31,其中時隙CH0用作幀同步用,時隙CH16用來傳送信令。其余的時隙用來傳送有效數(shù)據(jù)。

通過將不同的接口數(shù)據(jù)插入不同的數(shù)據(jù)時隙,把多路接口數(shù)據(jù)編成一個E1數(shù)據(jù)幀,實(shí)現(xiàn)多路接口與E1的協(xié)議轉(zhuǎn)換。

將多路接口數(shù)據(jù)映射到E1時隙中,需要根據(jù)每路接口的速率進(jìn)行時隙分配,也就是將E1的一個或多個時隙分配給一路接口使用,分配的時隙速率不小于接口速率(每個時隙的速率相當(dāng)于64 Kb/s),DTE(Data Terminal Equipment)與DCE(Data Communications Equipment)設(shè)備端時隙分配設(shè)置必須一致。由于協(xié)議轉(zhuǎn)換器沒有自適應(yīng)接口速率的功能,因此時隙的分配通過一個軟件界面由使用者完成。

為了實(shí)現(xiàn)對時隙的分配,設(shè)置30個4位的時隙分配寄存器。CPU根據(jù)使用者的時隙分配設(shè)置,生成30個數(shù)據(jù)時隙地址并寫入對應(yīng)時隙分配寄存器。數(shù)據(jù)時隙地址表示的是該數(shù)據(jù)時隙傳送的是哪個接口的數(shù)據(jù)。在發(fā)送端,根據(jù)該地址從相應(yīng)接口讀取數(shù)據(jù)插入對應(yīng)時隙;在接收端,根據(jù)該地址將相應(yīng)時隙數(shù)據(jù)送往對應(yīng)接口。表1為數(shù)據(jù)時隙地址與接口對應(yīng)關(guān)系表,空閑表示該時隙空置沒有使用。

系統(tǒng)將E1時隙分配給多路接口使用,當(dāng)有時隙沒有被分配時,就會產(chǎn)生空時隙。在本設(shè)計中,系統(tǒng)可支配的最小單位是E1時隙,也就是說,系統(tǒng)可以將一個數(shù)據(jù)時隙分配給一路接口使用,也可以將多個數(shù)據(jù)時隙分配給一路接口使用,當(dāng)一路接口數(shù)據(jù)不能完全填滿一個或多個時隙時,將會產(chǎn)生半空時隙。比如一個100 Kb/s的接口,占用兩個時隙,將會產(chǎn)生28 Kb/s的空時隙。

對于沒有使用的空閑時隙,系統(tǒng)可以根據(jù)時隙分配寄存器的值識別空閑時隙。在發(fā)送端,默認(rèn)發(fā)送全“1”數(shù)據(jù),在接收端,拋棄該無用數(shù)據(jù);對于一路接口數(shù)據(jù)不能完全填滿一個或多個數(shù)據(jù)時隙產(chǎn)生的半空時隙,采取循環(huán)發(fā)空包的方法來填充半空時隙,空包格式固定為“000 01111”。在接收端,檢測到這樣的空包數(shù)據(jù),丟棄不用。

下面主要實(shí)現(xiàn)V.35,RS 449,RS 232三路接口與E1協(xié)議轉(zhuǎn)換的設(shè)計。通過三路接口與E1協(xié)議轉(zhuǎn)換的實(shí)現(xiàn),驗(yàn)證多路接口同時與E1協(xié)議轉(zhuǎn)換的可行性。

1.3 系統(tǒng)硬件原理框圖與模塊功能描述

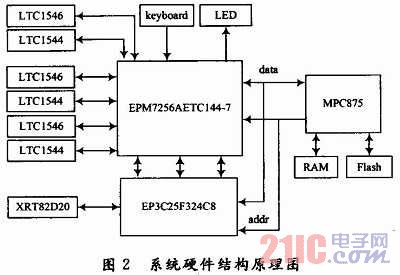

系統(tǒng)硬件原理框圖如圖2所示,主要由接口芯片、FPGA、CPLD、微處理器構(gòu)成。

LTC1546/LTC1544:多功能接口芯片LTC1546,LTC1544,二者結(jié)合,構(gòu)成全功能的多協(xié)議接口界面,支持RS232,RS449,EIA530,EIA-530-A,V.35,V.36,X.21協(xié)議,協(xié)議的選擇可完全由軟件進(jìn)行。

MPC875:飛思卡爾MPC875嵌入式CPU,基于POWERPC架構(gòu),主頻高達(dá)133 MHz,8 KB指令cache,8 KB數(shù)據(jù)cache,總線頻率最高可達(dá)80 MHz。

EP3C25F324C8:Altera公司的CycloneⅢ系列FPGA,性價比高,資源豐富。

EPM7256 AETCl44-7:A1tera公司MAX7000AE系列CPLD,支持多種接口電平。由于LTC1546,LTC1544接口電平為5 V,F(xiàn)PGA不支持這樣的接口電壓,這里使用CPLD作接口電路。

XRT82D20:RXAR公司的E1線路接口芯片,支持單路E1,具有HDB3編碼、時鐘恢復(fù)、線路驅(qū)動等功能,75 Ω或者120 Ω阻抗匹配。

keyboard:4×4鍵盤,用來接收時隙分配設(shè)置輸入。

LED:LED指示燈,共30個,用來指示30個數(shù)據(jù)時隙的使用情況:當(dāng)LED燈點(diǎn)亮?xí)r,表示該時隙已經(jīng)使用;LED燈不亮,表示該時隙為空閑。

2 關(guān)鍵模塊設(shè)計

2.1 與CPU通信FPGA端硬件電路設(shè)計

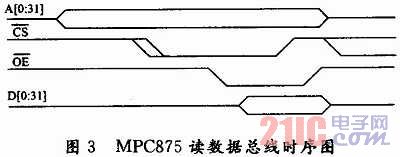

當(dāng)FPGA與CPU通信時,由于CPU總線特殊的時序關(guān)系,F(xiàn)PGA端須做相應(yīng)的處理才能保證讀寫數(shù)據(jù)的穩(wěn)定性。圖3為MPC875讀數(shù)據(jù)總線時序圖。其中:![]() 為片選信號,

為片選信號,![]() 為讀信號,A[0:31]為地址信號,D[0:31]為數(shù)據(jù)信號。圖4為MPC875寫數(shù)據(jù)總線時序圖,

為讀信號,A[0:31]為地址信號,D[0:31]為數(shù)據(jù)信號。圖4為MPC875寫數(shù)據(jù)總線時序圖,![]() 為寫信號,其余信號與讀總線相同。

為寫信號,其余信號與讀總線相同。

當(dāng)CPU讀取FPGA中數(shù)據(jù)時,先給出地址信號,然后使能片選![]() 、讀信號

、讀信號![]() ,這時如果數(shù)據(jù)總線上有數(shù)據(jù),CPU讀入數(shù)據(jù)。但MPC875總線頻率高達(dá)80 MHz,為了CPU能穩(wěn)定的讀取到數(shù)據(jù),這里將片選信號與讀信號相“與”,然后擴(kuò)寬3倍得到總線可用信號,在總線可用信號有效期間,數(shù)據(jù)總線上總有數(shù)據(jù),這樣,可以保證CPU能穩(wěn)定的讀到數(shù)據(jù)。

,這時如果數(shù)據(jù)總線上有數(shù)據(jù),CPU讀入數(shù)據(jù)。但MPC875總線頻率高達(dá)80 MHz,為了CPU能穩(wěn)定的讀取到數(shù)據(jù),這里將片選信號與讀信號相“與”,然后擴(kuò)寬3倍得到總線可用信號,在總線可用信號有效期間,數(shù)據(jù)總線上總有數(shù)據(jù),這樣,可以保證CPU能穩(wěn)定的讀到數(shù)據(jù)。

當(dāng)CPU寫入數(shù)據(jù)時,CPU先給出地址信號,然后給出片選及寫信號,在寫信號有效期間,CPU穩(wěn)定的給出數(shù)據(jù)。因此,在片選及寫信號有效時,鎖存數(shù)據(jù)總線上的數(shù)據(jù)即可。

2.2 CPLD硬件接口電路設(shè)計

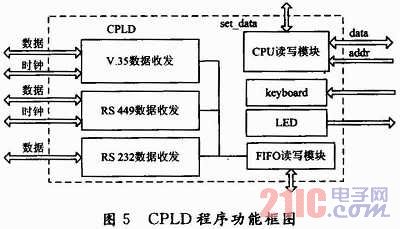

CPLD主要完成V.35,RS 449,RS 232數(shù)據(jù)收發(fā);keyboard,LED控制;FIFO讀寫等功能。功能框圖如圖5所示。

CPU通過CPLD對接口芯片進(jìn)行模式選擇。V.35,RS 449為同步平衡接口,常用接口速率為N×64 Kb/s(N=1~32)。時鐘、數(shù)據(jù)信號為兩線平衡傳輸,控制信號為不平衡傳輸。發(fā)送數(shù)據(jù)時,將與之對應(yīng)的時鐘一并輸出。在接收數(shù)據(jù)時,用接口時鐘采樣數(shù)據(jù)。

RS 232為不平衡傳輸。幀格式固定為:1位開始位、8位數(shù)據(jù)位、結(jié)束位。結(jié)束位有三種:1位、1.5位、2位。開始位固定為“0”,停止位固定為“1”。通信雙方在開始通信前必須約定好串行傳輸?shù)膮?shù)(傳輸速度、幀格式)。在發(fā)送端,首先通過分頻產(chǎn)生需要的串行波特率,然后按照幀格式以約定好的速率發(fā)送。在接收端,使用8倍于波特率的時鐘對接收到的信號進(jìn)行過采樣,經(jīng)過濾波后如果為低電平信號,即認(rèn)為是開始位,然后按照約定好的速率接收數(shù)據(jù)。

在接收數(shù)據(jù)時,F(xiàn)IFO讀寫模塊將串行接收數(shù)據(jù)變成8位并行,同時,將與接收數(shù)據(jù)同步的時鐘8分頻,用此時鐘將8位并行數(shù)據(jù)寫入與該接口對應(yīng)的FIFO;在發(fā)送數(shù)據(jù)時,將發(fā)送時鐘8分頻,用此時鐘從與該接口對應(yīng)的FIFO讀取數(shù)據(jù),同時將8位并行數(shù)據(jù)串行輸出。

keyboard為4×4掃描式矩陣鍵盤,具有16個鍵。由硬件程序自動掃描鍵盤,輸入數(shù)據(jù)觸發(fā)中斷,CPU讀取數(shù)據(jù)。LED輸出由CPU寫入相應(yīng)的顯示寄存器,然后硬件程序?qū)⑾嚓P(guān)信號輸出點(diǎn)亮LED。

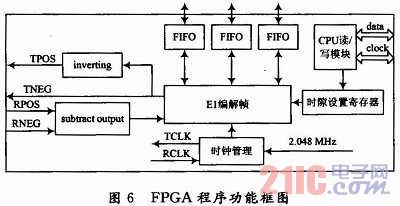

2.3 FPGA硬件電路設(shè)計

FPGA主要根據(jù)時隙的分配設(shè)置,在時鐘系統(tǒng)的管理控制下,完成E1的編解幀功能。功能框圖如圖6所示。

CPU根據(jù)設(shè)置向時隙分配寄存器寫入相應(yīng)的數(shù)據(jù)。在發(fā)送數(shù)據(jù)時,E1編解幀模塊根據(jù)時隙分配設(shè)置,從相應(yīng)的FIFO讀取數(shù)據(jù),寫入該時隙。對于沒有使用的空時隙,按照空時隙處理辦法填入無效數(shù)據(jù)。發(fā)送時鐘為FPGA外接的2.048 MHz時鐘。由于XRT82D20為數(shù)據(jù)差分輸入,因此將編解幀模塊輸出的數(shù)據(jù)TPOS進(jìn)行反向得到TNEG,平衡輸出。TCLK為發(fā)送時鐘。

在接收時,XRT82D20數(shù)據(jù)差分輸入RPOS,RNEG,將兩個信號相減得到輸入數(shù)據(jù)信號,RCLK為時鐘輸入。在輸入時鐘的控制下,E1編解幀模塊將數(shù)據(jù)解幀。同時,根據(jù)時隙分配設(shè)置,將各個時隙的數(shù)據(jù)送入不同的接口FIFO。

3 軟件主程序流程圖

MPC875主要完成接口芯片初始化設(shè)置、時隙分配設(shè)置輸入、狀態(tài)顯示等功能。軟件主程序流程圖如圖7所示。

上電以后,CPU進(jìn)行初始化設(shè)置。延遲1 ms進(jìn)行內(nèi)存地址分配:每個自定義寄存器及I/O均分配一個內(nèi)存地址,CPU操作時讀寫相應(yīng)地址即可;接著進(jìn)行LTC1546/LTC1544模式選擇,將三組接口分別配置為V.35,RS 449,RS 232;然后查詢時隙分配設(shè)置輸入,如果已經(jīng)輸入時隙分配設(shè)置,則讀取時隙設(shè)置數(shù)據(jù),否則,等待時隙設(shè)置輸入;協(xié)議轉(zhuǎn)換器初始化設(shè)置完畢,每隔100 ms進(jìn)行一次線路運(yùn)行狀態(tài)告警顯示。

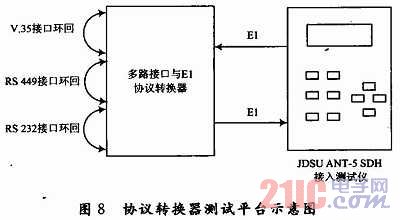

4 協(xié)議轉(zhuǎn)換器測試

4.1 測試平臺搭建

測試平臺由JDSU ANT-5 SDH接入測試儀,協(xié)議轉(zhuǎn)換器,示意圖如圖8所示。JDSU ANT-5手持型SDH/PDH傳輸分析儀,內(nèi)置所有必要的接口:從T1Bantam、E1平衡與E1非平衡,到STM-16/OC48光接口;測試速率從1.544 Mb/s~2.5 Gb/s;大屏幕、簡單圖形化界面、中文菜單,易于使用。

首先進(jìn)行時隙分配設(shè)置,將1到15時隙分配給V.35接口,17到30時隙分配給RS 449接口,31時隙分配給RS 232接口。由JDSU ANT-5 SDH接入測試儀發(fā)出的2 MHz信號,進(jìn)入?yún)f(xié)議轉(zhuǎn)換器,然后分別將V.35,RS 449,RS 232接口環(huán)回,再將輸出的E1信號接入測試儀,在測試儀中測試環(huán)回信號的各種特性。

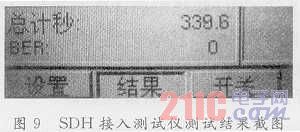

4.2 測試結(jié)果

依照上述測試平臺進(jìn)行協(xié)議轉(zhuǎn)換器功能測試,測試結(jié)果顯示,誤碼率為0,說明協(xié)議轉(zhuǎn)換器功能正常。JDSU ANT-5 SDH接入測試儀測試截圖如圖9所示。其中BER為誤碼率。

5 結(jié)語

本文提出了一種多路接口與E1的協(xié)議轉(zhuǎn)換設(shè)計方法,并具體介紹了時隙分配及調(diào)度、空時隙處理等技術(shù)難點(diǎn)。通過實(shí)現(xiàn)V.35,RS449,RS 232三路接口與E1的協(xié)議轉(zhuǎn)換,證明該方案是可行的。另外,本設(shè)計具有良好的擴(kuò)展性,可以方便的根據(jù)具體應(yīng)用添加或去除接口,也可以在本設(shè)計的基礎(chǔ)上進(jìn)行二次開發(fā),完成更多的功能。