1 前言

I2C總線是具備多CPU系統(tǒng)所需的包括仲裁和高低速設(shè)備同步等功能的高性能串行總線。它以?xún)筛B線實(shí)現(xiàn)完善的全雙工數(shù)據(jù)傳送,是各種總線中使用信號(hào)線根數(shù)最少,并具有自動(dòng)尋址、多主機(jī)時(shí)鐘同步和仲裁等功能的總線。

目前世界上采用的I2C總線有兩種規(guī)范,它們分別是由荷蘭飛利浦公司和日本索尼公司提出的。現(xiàn)在廣泛采用的是飛利浦公司的I2C總線技術(shù)規(guī)范,它已成為被電子行業(yè)認(rèn)可的總線標(biāo)準(zhǔn)。

由于I2C總線具有標(biāo)準(zhǔn)的規(guī)范及眾多帶I2C接口的外圍器件,使得使用I2C總線設(shè)計(jì)計(jì)算機(jī)系統(tǒng)變得十分方便、靈活,體積也小,因此在各類(lèi)實(shí)際應(yīng)用中得到廣泛使用。

2 I2C總線的基本原理

2.1 I2C總線基本結(jié)構(gòu)

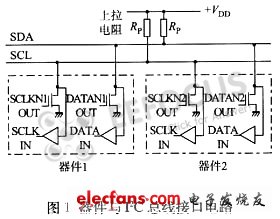

I2C總線系統(tǒng)結(jié)構(gòu)靈活,易于模塊化、標(biāo)準(zhǔn)化設(shè)計(jì)。I2C總線只有兩根信號(hào)線,一根是數(shù)據(jù)線SDA,另一根是時(shí)鐘線SCL。所有進(jìn)入I2C總線系統(tǒng)中的器件都帶有I2C總線接口,符合I2C總線電氣規(guī)范的特性;而且采用純軟件尋址方法,無(wú)需器件片選線的連接。CPU不僅能通過(guò)指令將某個(gè)功能器件掛靠或摘離總線,還可對(duì)其工作狀況進(jìn)行檢測(cè),從而實(shí)現(xiàn)對(duì)硬件系統(tǒng)即簡(jiǎn)單又靈活的擴(kuò)展與控制。各器件供電可不同,但需共地。另外,SDA、SCL需分別接上拉電阻。

SDA、SCL都是雙向的,輸出電路用于向總線上發(fā)送數(shù)據(jù),輸入電路用于接收總線上的數(shù)據(jù)。當(dāng)總線空閑時(shí),兩根線都是高電平。連接總線的器件的輸出端電路必須是集電極開(kāi)路輸出或開(kāi)漏輸出,以具有線“與”功能。I2C總線的數(shù)據(jù)傳送速率在標(biāo)準(zhǔn)模式下可達(dá)100kbit/s,快速模式下可達(dá)400kbit/s,高速模式下則可達(dá)3.4Mbit/s。

I2C總線接口電路結(jié)構(gòu)如圖1所示。

2.2 I2C總線數(shù)據(jù)傳送

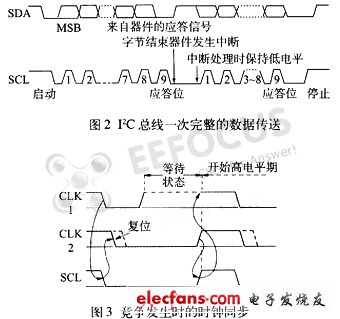

I2C總線數(shù)據(jù)傳輸時(shí)必須遵循規(guī)定的數(shù)據(jù)傳送格式,如圖2所示為一次完整的數(shù)據(jù)傳送格式。啟動(dòng)信號(hào)表明一次傳送的開(kāi)始,其后為尋址字節(jié),該尋址字節(jié)由高7位地址和最低1位方向位組成:方向位為“0”表明寫(xiě)操作,“1”表明讀操作;在尋址字節(jié)后是由方向位指定讀、寫(xiě)操作的數(shù)據(jù)字節(jié)與應(yīng)答位;在數(shù)據(jù)傳送完成后為停止信號(hào)。在“啟動(dòng)”與“停止”之間傳送的數(shù)據(jù)字節(jié)數(shù)從理論上來(lái)說(shuō)沒(méi)有限制,但每個(gè)字節(jié)必須為8位,而且每個(gè)傳送的字節(jié)后面必須跟一個(gè)應(yīng)答位。

當(dāng)SCL為高電平時(shí),SDA由高電平跳變?yōu)榈碗娖剑x為啟動(dòng)信號(hào);當(dāng)SCL為低電平時(shí),SDA由低電平跳變?yōu)楦唠娖剑x為停止信號(hào)。

在SCL為高電平時(shí),SDA上數(shù)據(jù)需保持穩(wěn)定方被認(rèn)為有效;只有在SCL為低電平時(shí),才允許SDA電平狀態(tài)變化。

2.3時(shí)鐘信號(hào)的同步

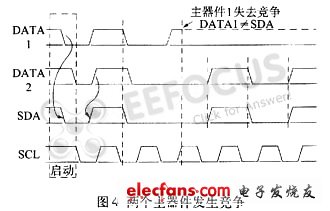

在I2C總線上傳送信息時(shí)的時(shí)鐘同步信號(hào)是由掛接在SCL線上的所有器件的邏輯“與”完成的。SCL線上由高電平到低電平的跳變將影響到這些器件,一旦某個(gè)器件的時(shí)鐘信號(hào)下跳為低電平,將使SCL線一直保持低電平,使SCL線上的所有器件開(kāi)始低電平期。此時(shí),低電平周期短的器件的時(shí)鐘由低至高的跳變并不能影響SCL線的狀態(tài),于是這些器件將進(jìn)入高電平等待的狀態(tài)。當(dāng)所有器件的時(shí)鐘信號(hào)都上跳為高電平時(shí),低電平期結(jié)束,SCL線被釋放返回高電平,即所有的器件都同時(shí)開(kāi)始它們的高電平期。其后,第一個(gè)結(jié)束高電平期的器件又將SCL線拉成低電平。這樣就在SCL線上產(chǎn)生一個(gè)同步時(shí)鐘。可見(jiàn),時(shí)鐘低電平時(shí)間由時(shí)鐘低電平期最長(zhǎng)的器件確定,而時(shí)鐘高電平時(shí)間由時(shí)鐘高電平期最短的器件確定。

2.4 總線競(jìng)爭(zhēng)的仲裁

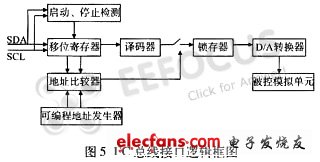

總線上可能掛接有多個(gè)器件,有時(shí)會(huì)發(fā)生兩個(gè)或多個(gè)主器件同時(shí)想占用總線的情況,這種情況叫做總線競(jìng)爭(zhēng)。I2C總線具有多主控能力,可以對(duì)發(fā)生在SDA線上的總線競(jìng)爭(zhēng)進(jìn)行仲裁,其仲裁原則是這樣的:當(dāng)多個(gè)主器件同時(shí)想占用總線時(shí),如果某個(gè)主器件發(fā)送高電平,而另一個(gè)主器件發(fā)送低電平,則發(fā)送電平與此時(shí)SDA總線電平不符的那個(gè)器件將自動(dòng)關(guān)閉其輸出級(jí)。總線競(jìng)爭(zhēng)的仲裁是在兩個(gè)層次上進(jìn)行的。首先是地址位的比較,如果主器件尋址同一個(gè)從器件,則進(jìn)入數(shù)據(jù)位的比較,從而確保了競(jìng)爭(zhēng)仲裁的可靠性。由于是利用I2C總線上的信息進(jìn)行仲裁,因此不會(huì)造成信息的丟失。

3 I2C總線接口邏輯的構(gòu)成

3.1 I2C總線接口電路的結(jié)構(gòu)

I2C總線接口邏輯框圖如圖5所示。

在電路設(shè)計(jì)中,各功能塊的硬件實(shí)現(xiàn)介紹如下。

啟動(dòng)、停止檢測(cè)電路應(yīng)用兩個(gè)D觸發(fā)器來(lái)分別響應(yīng)SDA在SCL為高電平時(shí)的電平跳變。

移位寄存器電路由9個(gè)D觸發(fā)器串聯(lián)成9級(jí)移位寄存器,包括8位字節(jié)和1位應(yīng)答位,實(shí)現(xiàn)SDA上數(shù)據(jù)的串并行轉(zhuǎn)換。寄存器復(fù)位值為“111111110”,接收8位字節(jié)后為“0D7D6D5D4D3D2D1D0”,即應(yīng)答位為“0”,在第9個(gè)時(shí)鐘時(shí)輸出低電平作為應(yīng)答信號(hào)。

可編程地址發(fā)生器電路生成器件地址,7位器件地址由器件編號(hào)地址(高4位)和引腳地址(低3位)組成。通過(guò)改變器件引腳的連接方式,就可改變器件地址,因此使應(yīng)用方便靈活。

地址比較器電路由門(mén)電路組成布爾代數(shù)式邏輯,對(duì)尋址字節(jié)進(jìn)行判斷。若地址正確則將RS觸發(fā)器置“1”,使能譯碼器輸出。

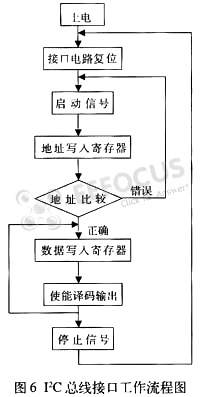

3.2 I2C總線接口工作流程

I2C總線接口工作流程如圖6所示。

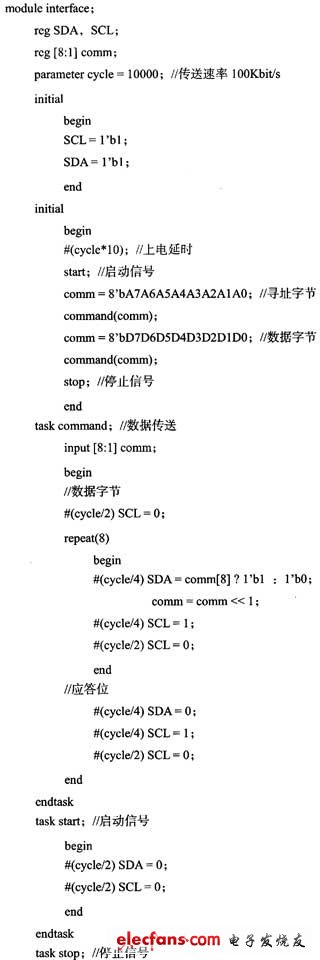

3.3 Verilog仿真程序

4 結(jié)束語(yǔ)

目前采用I2C技術(shù)的單片機(jī)以及外圍器件已廣泛應(yīng)用于家用電器、通訊設(shè)備及各類(lèi)電子產(chǎn)品中,而且應(yīng)用范圍將會(huì)越來(lái)越廣。