在這篇《電源設(shè)計(jì)小貼士》中,我們將研究在同步降壓功率級(jí)中如何對(duì)傳導(dǎo)功耗進(jìn)行折中處理,而其與占空比和 FET 電阻比有關(guān)。進(jìn)行這種折中處理可得到一個(gè)用于 FET 選擇的非常有用的起始點(diǎn)。通常,作為設(shè)計(jì)過程的一個(gè)組成部分,您會(huì)有一套包括了輸入電壓范圍和期望輸出電壓的規(guī)范,并且需要選擇一些 FET。另外,如果您是一名 IC 設(shè)計(jì)人員,則您還會(huì)有一定的預(yù)算,其規(guī)定了 FET 成本或者封裝尺寸。這兩種輸入會(huì)幫助您選擇總 MOSFET 芯片面積。之后,這些輸入可用于對(duì)各個(gè) FET 面積進(jìn)行效率方面的優(yōu)化。

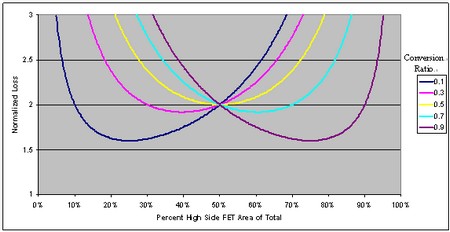

圖 1 傳導(dǎo)損耗與 FET 電阻比和占空比相關(guān)

首先,F(xiàn)ET 電阻與其面積成反比例關(guān)系。因此,如果為 FET 分配一定的總面積,同時(shí)您讓高側(cè)面積更大(旨在降低其電阻),則低側(cè)的面積必須減小,而其電阻增加。其次,高側(cè)和低側(cè) FET 導(dǎo)電時(shí)間的百分比與 VOUT/VIN 的轉(zhuǎn)換比相關(guān),其首先等于高側(cè)占空比 (D)。高側(cè) FET 導(dǎo)通 D 百分比時(shí)間,而剩余 (1-D) 百分比時(shí)間由低側(cè) FET 導(dǎo)通。圖 1 顯示了標(biāo)準(zhǔn)化的傳導(dǎo)損耗,其與專用于高側(cè) FET 的 FET 面積百分比(X 軸)以及轉(zhuǎn)換因數(shù)(曲線)相關(guān)。很明顯,某個(gè)設(shè)定轉(zhuǎn)換比率條件下,可在高側(cè)和低側(cè)之間實(shí)現(xiàn)最佳芯片面積分配,這時(shí)總傳導(dǎo)損耗最小。低轉(zhuǎn)換比率條件下,請(qǐng)使用較小的高側(cè) FET。反之,高轉(zhuǎn)換比率時(shí),請(qǐng)?jiān)陧敳渴褂酶嗟?FET。面積分配至關(guān)重要,因?yàn)槿绻敵鲈黾又?3.6V,則針對(duì) 12V:1.2V 轉(zhuǎn)換比率(10% 占空比)進(jìn)行優(yōu)化的電路,其傳導(dǎo)損耗會(huì)增加 30%,而如果輸出進(jìn)一步增加至 6V,則傳導(dǎo)損耗會(huì)增加近 80%。最后,需要指出的是,50% 高側(cè)面積分配時(shí)所有曲線都經(jīng)過同一個(gè)點(diǎn)。這是因?yàn)閮蓚€(gè) FET 電阻在這一點(diǎn)相等。

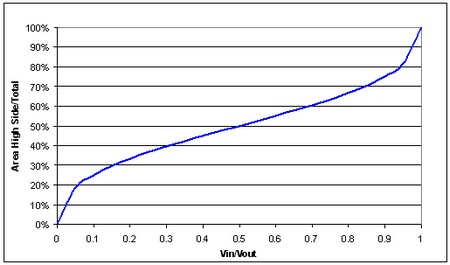

圖 2 存在一個(gè)基于轉(zhuǎn)換比率的最佳面積比

注意:電阻比與面積比成反比

通過圖 1,我們知道 50% 轉(zhuǎn)換比率時(shí)出現(xiàn)最佳傳導(dǎo)損耗極值。但是,在其他轉(zhuǎn)換比率條件下,可以將損耗降至這一水平以下。附錄 1 給出了進(jìn)行這種優(yōu)化的數(shù)學(xué)計(jì)算方法,而圖 2 顯示了其計(jì)算結(jié)果。即使在極低的轉(zhuǎn)換比率條件下,F(xiàn)ET 芯片面積的很大一部分都應(yīng)該用于高側(cè) FET。高轉(zhuǎn)換比率時(shí)同樣如此;應(yīng)該有很大一部分面積用于低側(cè)。這些結(jié)果是對(duì)這一問題的初步研究,其并未包括如高側(cè)和低側(cè)FET之間的各種具體電阻值,開關(guān)速度的影響,或者對(duì)這種芯片面積進(jìn)行封裝相關(guān)的成本和電阻等諸多方面。但是,它為確定 FET 之間的電阻比提供了一個(gè)良好的開端,并且應(yīng)會(huì)在FET選擇方面實(shí)現(xiàn)更好的整體折中。

下次,我們將討論如何確定 SEPIC 所用耦合電感的漏電感要求,敬請(qǐng)期待。本文及其他電源解決方案的更多詳情,請(qǐng)?jiān)L問:www.ti.com.cn/power。

附錄:圖 2 的推導(dǎo)過程

定義:

占空比:

MOSFET 指定電阻 (歐姆*面積):

總面積:A

高側(cè) FET 面積:

高側(cè) FET 電阻:

低側(cè) FET 電阻:

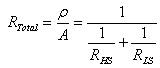

有效 FET 電阻:

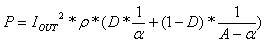

總傳導(dǎo)損耗求解過程 (用于圖 1):

利用 α 相關(guān)導(dǎo)數(shù):

將高側(cè)面積比總 FET 面積定義為 . (注意:其為電阻比的倒數(shù)。) 讓上面的方程式等于零,然后代入。

經(jīng)過大量的代數(shù)計(jì)算后得到:

結(jié)果如圖 2 所示。