1 引言

雷達恒虛警(CFAR-Constant False Alarm Rate)在雷達系統(tǒng)中有著重要的作用和地位。恒虛警處理可以避免雜波變化影響的檢測閾值,提高雷達在各種干擾情況下的檢測能力。

美國模擬器件公司(ADD的ADSP-TS201處理器具有高速運算能力、可時分復(fù)用、并行處理、數(shù)據(jù)吞吐率高等特點。該處理器片內(nèi)集成大容量存儲器,性價比高,并兼有ASIC和FPGA的信號處理性能、指令集處理器的高度可編程性與靈活性,適用于高性能、大存儲量的信號處理和圖像應(yīng)用。本文主要討論基于ADSP-TS201的恒虛警實現(xiàn)方法。

2 ADSP-TS201簡介

ADSP-TS201采用超級哈佛結(jié)構(gòu),靜態(tài)超標量操作適合多處理器模式運算,可直接構(gòu)成分布式并行系統(tǒng)和共享存儲式并行系統(tǒng)。ADSP-TS201的主要性能指標如下:

最高工作主頻600 MHz(1.67 ns指令周期);

支持IEEE浮點格式32 bit數(shù)據(jù)和40 bit擴展精度浮點格式。同時支持8/16/32/64 bit的定點數(shù)據(jù)格式;

允許128 bit的數(shù)據(jù)、指令和I/O端口訪問,內(nèi)部存儲器帶寬33.6 GB/s;

32 bit的地址總線提供4 G的統(tǒng)一尋址空間;

14通道的DMA控制器支持硬件和軟件中斷,支持優(yōu)先級中斷和嵌套中斷;

4個全雙工LINK端口支持最達500 MB/s的傳輸速度;

JTAG仿真接口允許多片DSP仿真。

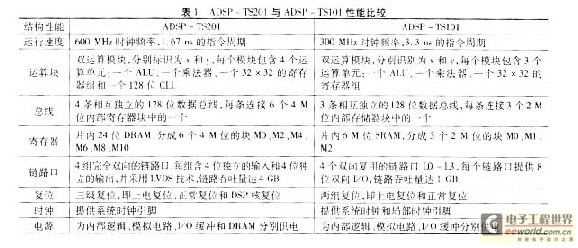

3 ADSP-TS201與TS101性能比較

ADSP-TS201與ADSP-TS101相比,主要在運行速度、存儲器結(jié)構(gòu)和鏈路口結(jié)構(gòu)上有差別,如表1所列。通過比較可以看出ADSP-TS201的性能比較好,故選用ADSP-TS201實現(xiàn)雷達恒虛警檢測。

4恒虛警檢測原理

4.1選大單元平均CFAR(GO-CFAR)

云雨雜波和低分辨率雷達的海浪和地物雜波的包絡(luò)服從瑞利分布,其概率密度函數(shù)為:

門限VT一旦確定,背景噪聲(干擾)和雜波干擾會使虛警概率增加,因此恒虛警處理十分必要。雜波干擾環(huán)境通常采用單元平均恒虛警。實際工程中為了消除雜波邊緣內(nèi)側(cè)虛警顯著增大,采用選大單元平均恒虛警。

選大單元平均CFAR通過兩側(cè)2L個距離單元數(shù)據(jù)平均值估算雜波功率,用雜波功率對所檢測的距離單元數(shù)據(jù)進行歸一化并乘以門限,作為檢測門限。檢測門限與檢測單元比較,超過門限判斷為有目標,低于門限判斷為無目標。

4.2雜波圖

雜波圖可認為是CFAR中的一種,采用參考樣本估計雜波電平。將雷達周圍的二維平面劃分成許多方位距離單元,再將每個方位距離單元的接收信號存入存儲器,每個存儲單元對應(yīng)一個方位距離單元。一個雜波圖單元可以由一個或幾個分辨單元組成。按照不同的距離和不同的波位計算并存儲雜波圖,利用雜波圖數(shù)據(jù)設(shè)置門限并與雷達回波相比較,檢測低速目標。

雜波圖分為動態(tài)雜波圖和靜態(tài)雜波圖。靜態(tài)雜波圖是在雷達建站時或者定期對雷達周圍的雜波環(huán)境進行測量,靜態(tài)雜波圖對雷達回波信號按照特定公式進行歸一化處理,一般用于接收機控制增益。而動態(tài)雜波圖隨著天線掃描,每個方位單元存儲的信號遞歸更新,天線多圈掃描后,幅度雜波圖存儲相應(yīng)方位距離單元的雜波均值。檢測門限為相應(yīng)方位距離單元雜波均值與門限之積。如果被檢測信號大于門限,則判為有目標,否則判為無目標。

5 恒虛警在ADSP-TS201上的實現(xiàn)

5.1運算量、存儲量分析及時間估計

首先分析選大單元平均CFAR的運算量和時間。以某一重復(fù)頻率為例(重復(fù)頻率為184μs,無模糊距離為27.6 km),整個距離的數(shù)據(jù)量約為3.6

K個32 bit的字。處理一幀數(shù)據(jù)的時間約185.5

ms。經(jīng)多普勒補償后數(shù)據(jù)量翻倍,實際處理一幀數(shù)據(jù)(定浮點轉(zhuǎn)換、取模、CFAR)的時間約為314.5

ms。因此僅用一片ADSP-TS201是無法實現(xiàn)的。

然后分析雜波圖的存儲量。將雷達周圍的二維平面劃分為6個掃描區(qū),每個掃描區(qū)有91個波位,每個波位存10層(前后各5層)雜波數(shù)據(jù)。若一個雜波圖單元由2個分辨單元組成,則一個雜波圖單元存儲16

bit,一個掃描區(qū)最大存儲量約為30 M,ADSP-TS201內(nèi)存不能存儲雜波圖數(shù)據(jù)。

5.2硬件實現(xiàn)

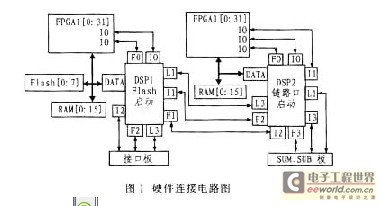

采用兩片ADSP-TS201實現(xiàn)硬件設(shè)計,每個處理器都連接一個32 MB×16 bit的SDRAM。硬件連接圖如圖1所示。

圖中,L表示鏈路口;F表示FLAG引腳;I表示外部中斷引腳;IO表示輸入輸出引腳;DATA表示數(shù)據(jù)口。

DSP1與Flash相連接用于啟動,DSP2與FPGA連接用于接收來自FPGA脈壓后的復(fù)數(shù)數(shù)據(jù)。兩個處理器之間的點對點通信是通過鏈路口互聯(lián)實現(xiàn)的,每個鏈路口以雙向全雙工方式工作。兩個DSP各自連接SDRAM用于存儲雜波圖數(shù)據(jù)。DSP1采用EPROM加載方式,DSP2通過鏈路口加載。

5.3軟件實現(xiàn)

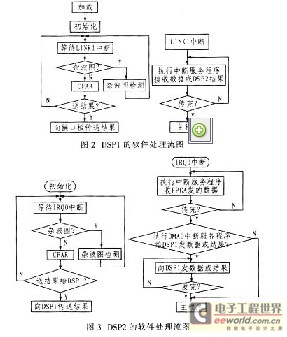

軟件設(shè)計主要實現(xiàn):定浮點轉(zhuǎn)換、取模、雜波圖檢測以及CFAR處理。每部分程序都是一個子程序,便于調(diào)用、調(diào)試。考慮到實時性要求,程序采用匯編語言,片內(nèi)利用ADSP-TS201的X,Y雙運算塊并行運算。由于選大單元平均CFAR處理要對兩側(cè)L個臨近單元求和,取模可直接求和,把取模和CFAR用一個子程序完成,減少了讀取數(shù)據(jù)的時間。圖2、圖3分別為DSP1、DSP2的軟件處理流圖。

DSP1主要完成加載,頻率通道號為奇數(shù)行數(shù)據(jù)的雜波圖檢測和CFAR,并將一幀數(shù)據(jù)檢測到的目標信息發(fā)送給接口板。DSP1的鏈路口3與接口板相連,將合并后的結(jié)果送給接口板用于模糊。

DSP2接收來自FPGA脈壓后的數(shù)據(jù),將頻率通道號為奇數(shù)的數(shù)據(jù)發(fā)送至DSP1,偶數(shù)行數(shù)據(jù)DSP2自行處理。一幀數(shù)據(jù)處理結(jié)束,DSP2將檢測到的目標信息送至DSP1,經(jīng)DSP1合并后再送出。

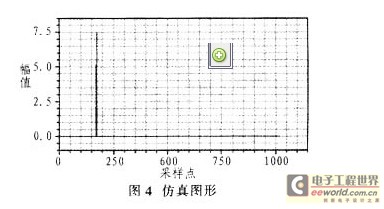

6系統(tǒng)仿真結(jié)果

軟硬件設(shè)計完成后,進行功能測試。圖4是背景雜波服從瑞利分布時,采用ADSP-TS201匯編語言對整個雷達目標恒虛警檢測過程仿真得到的結(jié)果。采樣點數(shù)為1

024點。需要指出的是,恒虛警檢測算法會帶來不同程度的恒虛警損失,與鄰近單元的個數(shù)L和積累周期數(shù)有關(guān),因此在實現(xiàn)時要盡量減小恒虛警損失。

7 結(jié)束語

介紹了在ADSP-TS201上實現(xiàn)雜波背景中雷達目標的恒虛警檢測方法,具體討論了實現(xiàn)過程中軟硬件設(shè)計,并給出了系統(tǒng)仿真結(jié)果。