數(shù)字信號(hào)處理器DSP是一種具有特殊結(jié)構(gòu)的微處理器,它專門為實(shí)現(xiàn)數(shù)字信號(hào)處理的各種算法而設(shè)計(jì),因而在硬件結(jié)構(gòu)上具有特殊性。TS201是ADI公司TigerSHARC系列中集成了定點(diǎn)和浮點(diǎn)計(jì)算功能的高速DSP。該處理器廣泛應(yīng)用于視頻、通信市場(chǎng)和國(guó)防軍事裝備中,適合于大數(shù)據(jù)量實(shí)時(shí)處理的應(yīng)用領(lǐng)域。

TigerSHARC系列DSP引導(dǎo)程序的加載方法非常靈活,可根據(jù)實(shí)際系統(tǒng)的需求靈活選用。某雷達(dá)信號(hào)處理機(jī)采用6U板形,CPCI總線采用歐洲卡尺寸標(biāo)準(zhǔn),通過(guò)CPCI總線與主機(jī)進(jìn)行數(shù)據(jù)通信。針對(duì)該信號(hào)處理機(jī)硬件系統(tǒng),本文提出一種引導(dǎo)方案,該方案采用CPCI總線向板卡傳輸引導(dǎo)代碼,進(jìn)而依靠FPGA通過(guò)鏈路口引導(dǎo)DSP自啟動(dòng)。

1 ADSP-TS201引導(dǎo)模式

DSP的引導(dǎo)就是在DSP系統(tǒng)復(fù)位的情況下從DSP外部存儲(chǔ)器裝載算法程序代碼的過(guò)程。TS201支持兩種引導(dǎo)模式:主引導(dǎo)(Master Boot)模式和從引導(dǎo)(S|ave Boot)模式。

在主引導(dǎo)模式下,TS201作為主動(dòng)方,用外部口輸出地址,讀引導(dǎo)方式選擇(![]() )等控制信號(hào),從EPROM或FLASH中加載代碼。在從引導(dǎo)模式下,TS201作為被動(dòng)方,不向外部輸出控制信號(hào),外部主機(jī)或其他設(shè)備向TS201的主機(jī)或鏈路口傳送要加載的代碼,TS201僅啟動(dòng)若干DMA通道,并執(zhí)行第一個(gè)DMA所接收的加載核。

)等控制信號(hào),從EPROM或FLASH中加載代碼。在從引導(dǎo)模式下,TS201作為被動(dòng)方,不向外部輸出控制信號(hào),外部主機(jī)或其他設(shè)備向TS201的主機(jī)或鏈路口傳送要加載的代碼,TS201僅啟動(dòng)若干DMA通道,并執(zhí)行第一個(gè)DMA所接收的加載核。

另外,F(xiàn)S201還可以選擇一種“非引導(dǎo)”模式,或利用TS201的(仿真器)USB-ICE加載程序,這種方式可直接將程序加載到TS201內(nèi)部的RAM或外部的RAM中,DSP直接從RAM中運(yùn)行程序,常用于DSP的調(diào)試過(guò)程。

通過(guò)對(duì)TS201的![]() 引腳的設(shè)置,可將DSP的引導(dǎo)過(guò)程設(shè)置成主引導(dǎo)模式或從引導(dǎo)模式。在DSP復(fù)位期間,如果

引腳的設(shè)置,可將DSP的引導(dǎo)過(guò)程設(shè)置成主引導(dǎo)模式或從引導(dǎo)模式。在DSP復(fù)位期間,如果![]() 引腳為低電平,則選擇主引導(dǎo)模式,DSP從外部EPROM或FLASH中加載程序;若

引腳為低電平,則選擇主引導(dǎo)模式,DSP從外部EPROM或FLASH中加載程序;若![]() 引腳為高電平,則進(jìn)入從引導(dǎo)模式,DSP為空閑狀態(tài),等待主機(jī)或鏈路口加載程序。兩種引導(dǎo)模式都有相同的加載過(guò)程,具體步驟如下:

引腳為高電平,則進(jìn)入從引導(dǎo)模式,DSP為空閑狀態(tài),等待主機(jī)或鏈路口加載程序。兩種引導(dǎo)模式都有相同的加載過(guò)程,具體步驟如下:

(1)TS201自動(dòng)啟動(dòng)一個(gè)DMA,自動(dòng)把256個(gè)字(32位)傳送到內(nèi)部存儲(chǔ)器的地址0x00~0xFF。

(2)TS201執(zhí)行上述256個(gè)字的指令(加載核),加載核啟動(dòng)其他DMA,把后續(xù)指令和數(shù)據(jù)加載到內(nèi)部和/或外部存儲(chǔ)器中。

(3)加載核自我覆蓋,執(zhí)行DSP算法程序。

本系統(tǒng)引導(dǎo)方案采用從引導(dǎo)模式,通過(guò)CPCI總線將代碼從主機(jī)傳至FPGA中,再利用FPGA經(jīng)過(guò)鏈路口啟動(dòng)DSP。

2 某雷達(dá)信號(hào)處理機(jī)的引導(dǎo)設(shè)計(jì)方案

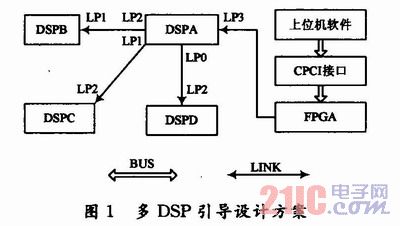

基于某雷達(dá)信號(hào)處理機(jī)硬件處理平臺(tái),采用如圖1所示的多DSP引導(dǎo)設(shè)計(jì)方案。

4片DSP的算法程序代碼(.LDR文件)通過(guò)上位機(jī)軟件傳輸?shù)紽PGA中,F(xiàn)PGA通過(guò)與DSPA的鏈路口給DSPA加載程序。DSPA加載成功后,分別引導(dǎo)DSPB,DSPC,DSPD啟動(dòng)。

采用這種方式加載DSP的優(yōu)點(diǎn):調(diào)試DSP時(shí)可以不使用JTAG仿真器;同時(shí)當(dāng)DSP自啟動(dòng)時(shí),可以不采用FLASH或E2PROM存放程序代碼,對(duì)于DSP程序的大小沒有限制,也節(jié)約了電路板的空間及其硬件設(shè)計(jì)復(fù)雜度。

采用這種方式加載DSP的難點(diǎn):CPCI總線與FPGA數(shù)據(jù)傳輸無(wú)誤及FPGA與TS201鏈路口通信,這兩個(gè)難點(diǎn)在實(shí)際工程中都已經(jīng)解決。CPCI總線與FPGA接口可以采用PLX9656芯片完成數(shù)據(jù)傳輸,所以這種加載模式的設(shè)計(jì)是可行的。

2.1 自動(dòng)引導(dǎo)程序設(shè)計(jì)思路

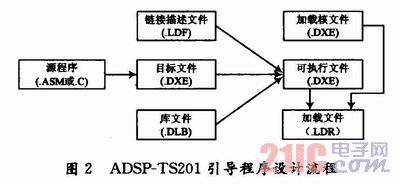

為了設(shè)計(jì)加載(自動(dòng)引導(dǎo))程序,首先必須了解ADSP-TS201的軟件設(shè)計(jì)流程,其流程圖如圖2所示。

其中,鏈接描述文件(.LDF)定義了整個(gè)系統(tǒng)的存儲(chǔ)器配置和程序中數(shù)據(jù)及代碼的具體存放位置。加載核文件(.DEX)是指加載引導(dǎo)核程序,其功能是將用戶工程所編譯成功的可執(zhí)行文件(.DXE)合成一個(gè)鏈路口加載方式的輸出文件(.LDR)。該加載輸出文件用來(lái)定義加載過(guò)程中TS201的內(nèi)部和外部存儲(chǔ)器如何被初始化。

在VisualDSP++安裝目錄的ldr子目錄下,ADI公司提供了標(biāo)準(zhǔn)加載核文件和相應(yīng)的源程序(.ASM)和鏈接描述文件。一般可直接使用提供的標(biāo)準(zhǔn)加載核文件或?qū)ζ湎鄳?yīng)的源程序進(jìn)行簡(jiǎn)單修改,重新編譯鏈接生成的加載核文件。加載文件是由引導(dǎo)加載器(elfloader)將可執(zhí)行文件進(jìn)行一定的格式變化,并在起始位置附加上加載核文件生成的。

由于TS201有三種引導(dǎo)方式(不考慮非引導(dǎo)模式),ADI公司相應(yīng)地提供了三種不同的加載和文件,分另0為:TS201_prom.dxe,TS201_li-nk.dxe,TS201_host.dxe。三個(gè)程序的核心思想和功能完全一致,只是由于使用的加載端口和方式不同,在具體代碼實(shí)現(xiàn)上稍有差異。由于本系統(tǒng)采用鏈路口啟動(dòng),同時(shí)對(duì)于DSPA,DSPB,DSPC,DSPD都采用不同的鏈路口啟動(dòng),因此采用鏈路口加載核文件,需要對(duì)加載核文件稍作修改,滿足不用鏈路口啟動(dòng)的需求。

2.2 本信號(hào)處理機(jī)的復(fù)位引導(dǎo)設(shè)計(jì)流程

如圖1所示,4片DSP要運(yùn)行的程序最終通過(guò)上位機(jī)讀取后,通過(guò)CPCI總線傳至FPGA,4片DSP為鏈路口引導(dǎo)模式。DSP復(fù)位后,DSPA從FPGA加載程序,DSPA加載完成后,再分別通過(guò)鏈路口加載DSPB,DSPC,DSPD。加載完成后,4片DSP正常執(zhí)行各自的程序。

結(jié)合以上各部分的分析,可以看出要實(shí)現(xiàn)該信號(hào)處理機(jī)中4片DSP的正確引導(dǎo),所需的工作由以下幾步組成:

(1)由DSPB要執(zhí)行的程序(DSPB.dxe),結(jié)合鏈路口的加載核程序生成DSPB的加載文件(DSPB_bin.ldr)。需要注意的是,該鏈路口加載核程序不能直接使用提供的標(biāo)準(zhǔn)鏈路口加載程序,必須將提供的鏈路口加載核文件(TS201_link.a(chǎn)sm)中的LINK常數(shù)改為1(#define LINK 1),即DSPB由鏈路口1引導(dǎo)。

(2)與(1)類似,生成DSPC的加載文件(DSPC_bin.ldr),只是需要把鏈路口加載核文件(TS201_link.a(chǎn)sm)中的LINK常數(shù)改為2(#define LINK 2),即DSPC由鏈路口2引導(dǎo)。同樣DSPD由鏈路口2加載,同樣生成DSPD的加載文件(DSPD_bin.ldr)。

(3)由于DSPA要通過(guò)鏈路口來(lái)對(duì)DSPB,DSPC,DSPD進(jìn)行程序引導(dǎo),所以在進(jìn)行DSPA編程時(shí),需要在程序的最開始添加給后面所有ADSPTS2 01的引導(dǎo)程序。而每片ADSP-TS201的程序都由引導(dǎo)碼和用戶程序構(gòu)成,所以在DSPA給其余DSP傳輸程序時(shí)將傳輸完整.1dr文件的數(shù)據(jù)。

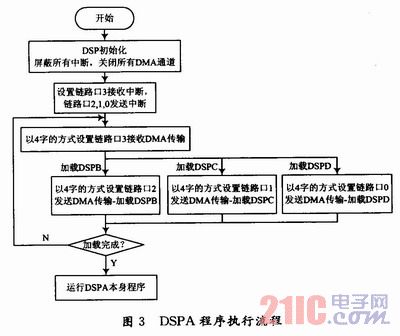

DSPA程序流程圖如圖3所示。

(1)DSPA關(guān)閉所有中斷,所有鏈路口和所有DMA通道,進(jìn)行初始化;

(2)開啟鏈路口3,2,1,0,設(shè)置鏈路口3接收中斷,鏈路口2,1,O發(fā)送中斷;

(3)設(shè)置鏈路口3通過(guò)DMA模式接收128 b數(shù)據(jù);

(4)判斷目前加載的DSP,設(shè)置相應(yīng)的鏈路口,發(fā)送接收到的128 b數(shù)據(jù);

(5)判斷DSPB,DSPC,DSPD是否加載完成,否則繼續(xù)通過(guò)鏈路口3接收數(shù)據(jù),直到DSP都加載完成;

(6)加載完成后,DSPA運(yùn)行自身DSP程序。

3 系統(tǒng)測(cè)試結(jié)果

上述引導(dǎo)設(shè)計(jì)在某雷達(dá)信號(hào)處理機(jī)中得到驗(yàn)證,通過(guò)上位機(jī)軟件,能靈活地加載引導(dǎo)代碼,使得調(diào)試更加便捷。測(cè)試上位機(jī)軟件如圖4所示。

修改雷達(dá)系統(tǒng)的數(shù)字信號(hào)處理算法,成功地將算法代碼加載到信號(hào)處理機(jī)中,從而驗(yàn)證引導(dǎo)設(shè)計(jì)方案正確可行。

4 結(jié)語(yǔ)

本文以某雷達(dá)信號(hào)處理機(jī)為平臺(tái),設(shè)計(jì)實(shí)現(xiàn)了基于CPCI總線的鏈路口多DSP引導(dǎo)方案,介紹了軟件設(shè)計(jì)流程及引導(dǎo)方案思想,最后成功驗(yàn)證了本引導(dǎo)方案的正確性和可行性。本引導(dǎo)方案不使用FLASH或E2PROM存放代碼,使多DSP的軟件編寫更加靈活,調(diào)試更加方便,同時(shí)使得硬件電路設(shè)計(jì)更加簡(jiǎn)潔。