集成電路設(shè)計(jì)過(guò)程中,驗(yàn)證占據(jù)了設(shè)計(jì)工作量的70%。驗(yàn)證的精確程度直接影響流片后邏輯功能的正確率,直接關(guān)系到芯片設(shè)計(jì)的成敗。另一方面,提高驗(yàn)證工作的效率,將對(duì)縮短整個(gè)芯片的設(shè)計(jì)周期、減少產(chǎn)品上市時(shí)間具有非常重要的意義。

隨著集成電路進(jìn)入數(shù)百萬(wàn)門(mén)ASIC、可復(fù)用的知識(shí)產(chǎn)權(quán)和系統(tǒng)芯片的時(shí)代,對(duì)驗(yàn)證環(huán)境的開(kāi)發(fā)以及使用效率、模塊化、層次化、可配置性和可復(fù)用性提出了更高的要求。本文以一款八通道多協(xié)議的串行通信控制器芯片為載體,介紹了基于總線(xiàn)功能模型的功能驗(yàn)證方法,該方法具有一定通用性。

1 芯片簡(jiǎn)介、驗(yàn)證計(jì)劃及驗(yàn)證策略

1.1 芯片簡(jiǎn)介

八通道串行通信控制器(以下稱(chēng)通信控制器)用于實(shí)現(xiàn)高級(jí)鏈路控制協(xié)議的高速串行通信。該芯片支持同步協(xié)議、異步協(xié)議、HDLC/SDLC等協(xié)議,可以在Intel總線(xiàn)模式和Motorola總線(xiàn)模式下使用,是為電信業(yè)務(wù)特別優(yōu)化的串行通信控制器,廣泛用于時(shí)分復(fù)用通信應(yīng)用系統(tǒng),如時(shí)分分組交換網(wǎng)絡(luò),局域網(wǎng)網(wǎng)關(guān)、網(wǎng)橋等。

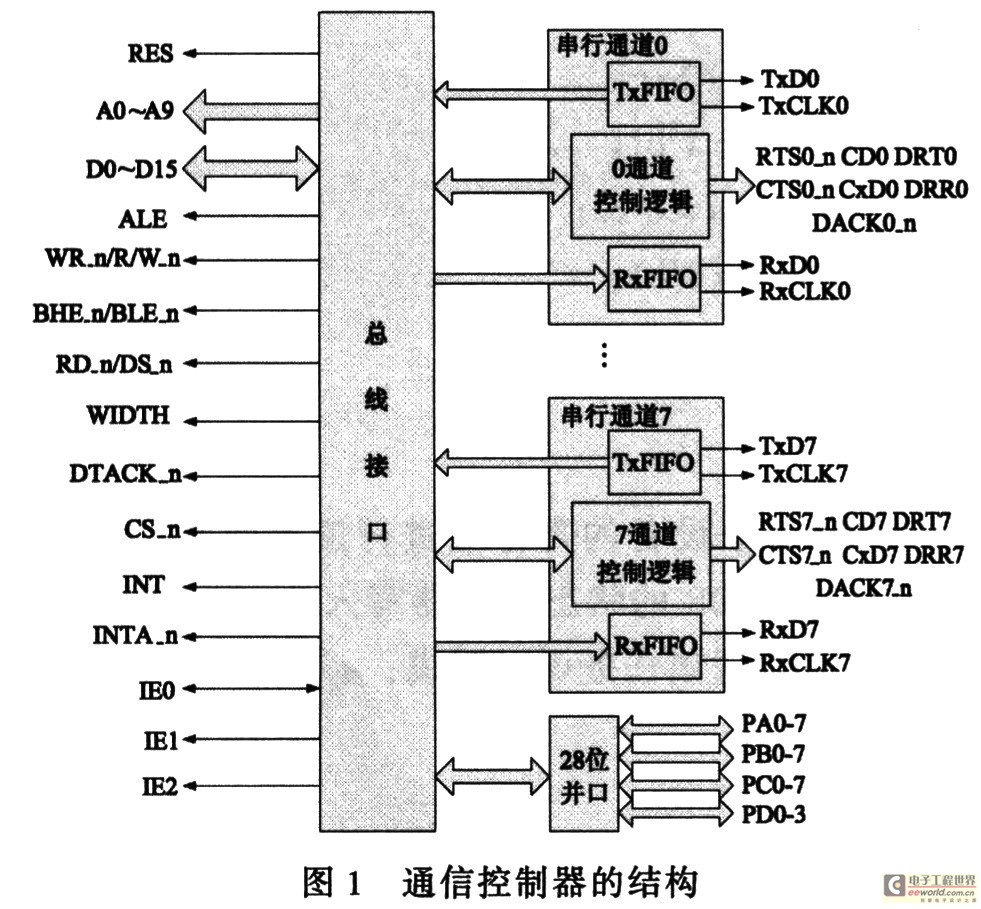

該通信控制器的總體結(jié)構(gòu)如圖1所示,按照功能原理,其硬件結(jié)構(gòu)可分為兩個(gè)組成部分:總線(xiàn)接口和串行通道控制電路。總線(xiàn)接口包括16位數(shù)據(jù)總線(xiàn)(DO~D15)、9位地址總線(xiàn)(A0~A8)、控制輸入信號(hào)、終端請(qǐng)求輸出信號(hào)、直接內(nèi)存存取(direct memory access,DMA)接口信號(hào)以及地址鎖存允許(address latch enable,ALE)信號(hào);串行通道控制電路包括8個(gè)相同的、獨(dú)立的全雙工串行接口(串行通道0~7)。每個(gè)通道又包括控制邏輯和接收發(fā)送FIFO。控制邏輯主要是波特率發(fā)生器(BRG),數(shù)字鎖相環(huán)(DPLL),時(shí)隙分配電路(TSA),協(xié)議控制電路,定時(shí)器和編解碼電路等模塊。同時(shí),該通信控制器具有一個(gè)28位的可配置輸入、輸出全局端口(PA0-7,PB0-7,PC0-7,PDO-3)。

1.2 驗(yàn)證策略分析及驗(yàn)證計(jì)劃制定

該芯片的驗(yàn)證難點(diǎn)在于,通信控制器支持的協(xié)議多,功能復(fù)雜,各種劃分方式以及功能的排列組合數(shù)量非常多。具體而言,通信控制器有8個(gè)通道,每個(gè)通道有32個(gè)8位配置寄存器,平均每個(gè)配置寄存器約有10種配置值,寄存器配置排列組合的數(shù)量更是驚人。

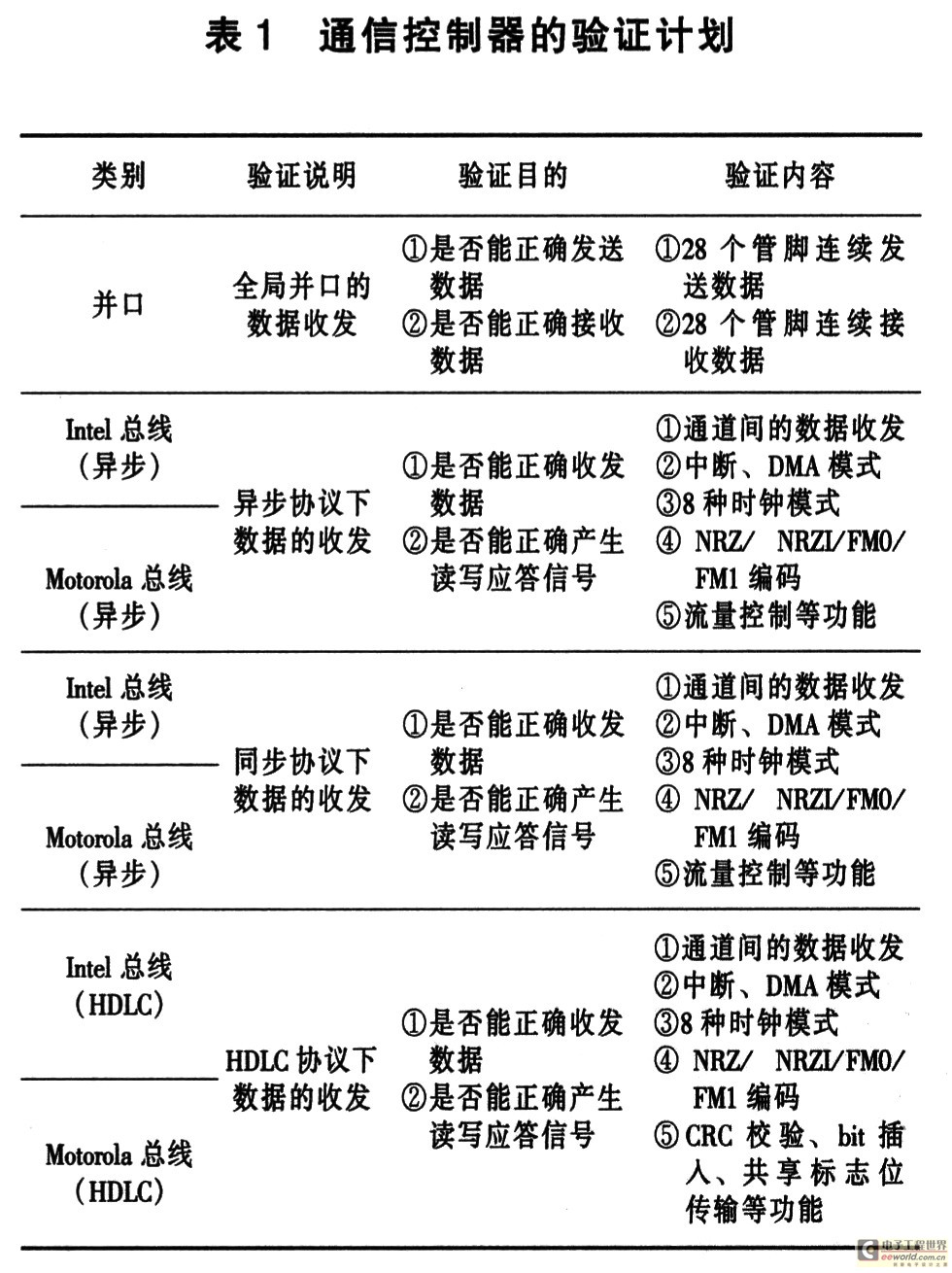

針對(duì)上述難點(diǎn),所采取的驗(yàn)證策略是,芯片的功能驗(yàn)證分類(lèi)按數(shù)據(jù)傳送協(xié)議將驗(yàn)證分為異步、同步、HDLC和并口四類(lèi),每一類(lèi)按照總線(xiàn)接口又分為Intel總線(xiàn)和Motorola總線(xiàn),再按照數(shù)據(jù)傳送類(lèi)型分為中斷模式和DMA模式,基于該分類(lèi)方法驗(yàn)證通信控制器的各項(xiàng)可配置功能,如CRC檢驗(yàn)、奇偶校驗(yàn)、流量控制等。

在驗(yàn)證層次上,由于組成通信控制器芯片的8個(gè)通道是獨(dú)立的、相同的,故采取先在子系統(tǒng)級(jí)驗(yàn)證一個(gè)單通道的數(shù)據(jù)傳送,繼而再驗(yàn)證全芯片8個(gè)通道的數(shù)據(jù)傳送的層次化驗(yàn)證方法,而如果每一個(gè)層次都需要構(gòu)造一個(gè)測(cè)試平臺(tái),任務(wù)就非常復(fù)雜。本文采取在兩個(gè)層次采用統(tǒng)一的驗(yàn)證環(huán)境的方法,從而降低了驗(yàn)證的復(fù)雜度,大大提高驗(yàn)證效率,縮短整個(gè)芯片的設(shè)計(jì)周期。開(kāi)始驗(yàn)證之前首先需要制定一個(gè)完整的驗(yàn)證計(jì)劃。驗(yàn)證計(jì)劃的制定要針對(duì)設(shè)計(jì)中可能出現(xiàn)的問(wèn)題,并涵蓋設(shè)計(jì)要實(shí)現(xiàn)的所有功能。通信控制器需要驗(yàn)證各種數(shù)據(jù)傳輸操作和一些其他功能。表1列出了該通信控制器的部分驗(yàn)證計(jì)劃,完整的驗(yàn)證計(jì)劃遠(yuǎn)比表1龐大,限于篇幅在此不一一給出。

2 驗(yàn)證方案

2.1 采用總線(xiàn)功能模型構(gòu)造驗(yàn)證平臺(tái)

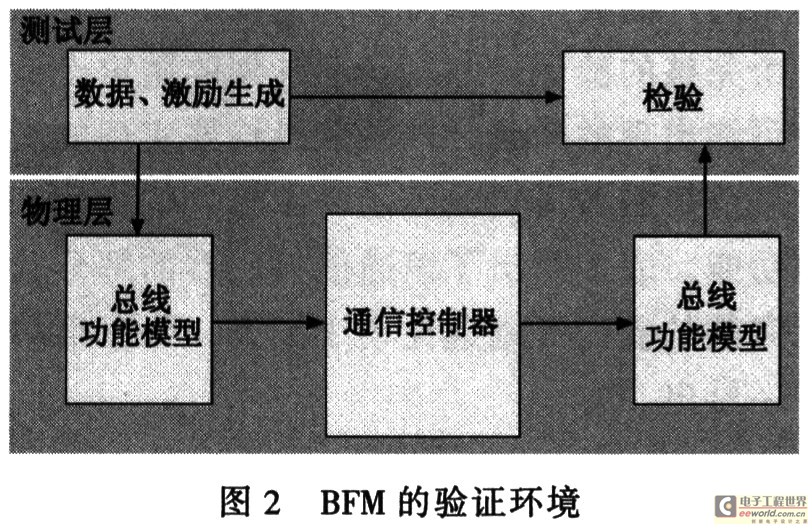

總線(xiàn)功能模型(BFM)是近年在測(cè)試平臺(tái)中廣泛采用的一種能提高驗(yàn)證重用效率的激勵(lì)生成方法。總線(xiàn)功能模型的作用是通過(guò)封裝低層總線(xiàn)的時(shí)序,向高層提供一個(gè)調(diào)用接口。總線(xiàn)功能模型的構(gòu)建有狀態(tài)機(jī)和任務(wù)庫(kù)兩種方式。通信控制器的驗(yàn)證采用了任務(wù)庫(kù)的方式來(lái)進(jìn)行總線(xiàn)功能模型設(shè)計(jì)。采用模塊的封裝方式把內(nèi)部操作的細(xì)節(jié)封裝起來(lái),通過(guò)“模塊名,任務(wù)名”的方式復(fù)用模塊,從而建立結(jié)構(gòu)化的testbench。基于總線(xiàn)功能模型的驗(yàn)證環(huán)境如圖2所示。

驗(yàn)證環(huán)境的下層是BFM和通信控制器邏輯電路組成的物理層。在這一層,BFM與通信控制器的引腳連接,根據(jù)總線(xiàn)協(xié)議驅(qū)動(dòng)總線(xiàn)信號(hào),同時(shí)將這種驅(qū)動(dòng)行為抽象成能夠被上層調(diào)用的任務(wù)(task)。上層是testcase組成的測(cè)試層,testcase根據(jù)所驗(yàn)證的功能產(chǎn)生測(cè)試數(shù)據(jù),通過(guò)調(diào)用下層提供的任務(wù),將產(chǎn)生的測(cè)試數(shù)據(jù)激勵(lì)輸入到被測(cè)電路中并監(jiān)測(cè)數(shù)據(jù)處理結(jié)果。可以看出,BFM通過(guò)對(duì)總線(xiàn)信號(hào)的時(shí)序進(jìn)行抽象和封裝,使測(cè)試環(huán)境有了層次化的結(jié)構(gòu)特點(diǎn)。這種層次化的特點(diǎn)能提高測(cè)試環(huán)境的開(kāi)發(fā)效率和可重用性,從而滿(mǎn)足驗(yàn)證通信控制器的如下要求。

首先,驗(yàn)證環(huán)境層次化的結(jié)構(gòu)保證了在各個(gè)層次的驗(yàn)證模塊開(kāi)發(fā)可以同時(shí)進(jìn)行,提高開(kāi)發(fā)效率。BFM將通信控制器測(cè)試環(huán)境的開(kāi)發(fā)強(qiáng)度和復(fù)雜程度分散到了物理層和測(cè)試層兩個(gè)不同的抽象層。在物理層,BFM專(zhuān)注于實(shí)現(xiàn)Intel總線(xiàn)或者M(jìn)otorola總線(xiàn)的各個(gè)時(shí)序操作;在測(cè)試層,testcase專(zhuān)注于針對(duì)通信控制器待驗(yàn)證的功能來(lái)設(shè)計(jì)測(cè)試向量。上層的testease和下層的BFM在定義了任務(wù)接口后,物理層和測(cè)試層的測(cè)試模塊可以進(jìn)行同時(shí)并行開(kāi)發(fā)。其次,由于testease和BFM處于兩個(gè)不同層次,所以可以在各自的層次上實(shí)現(xiàn)復(fù)用。處于上層的testcase,可以在后仿真階段直接復(fù)用;而處于下層的BFM不僅可以復(fù)用在后仿真階段,在引腳接口信號(hào)通信協(xié)議相類(lèi)似的項(xiàng)目開(kāi)發(fā)中亦可重用。

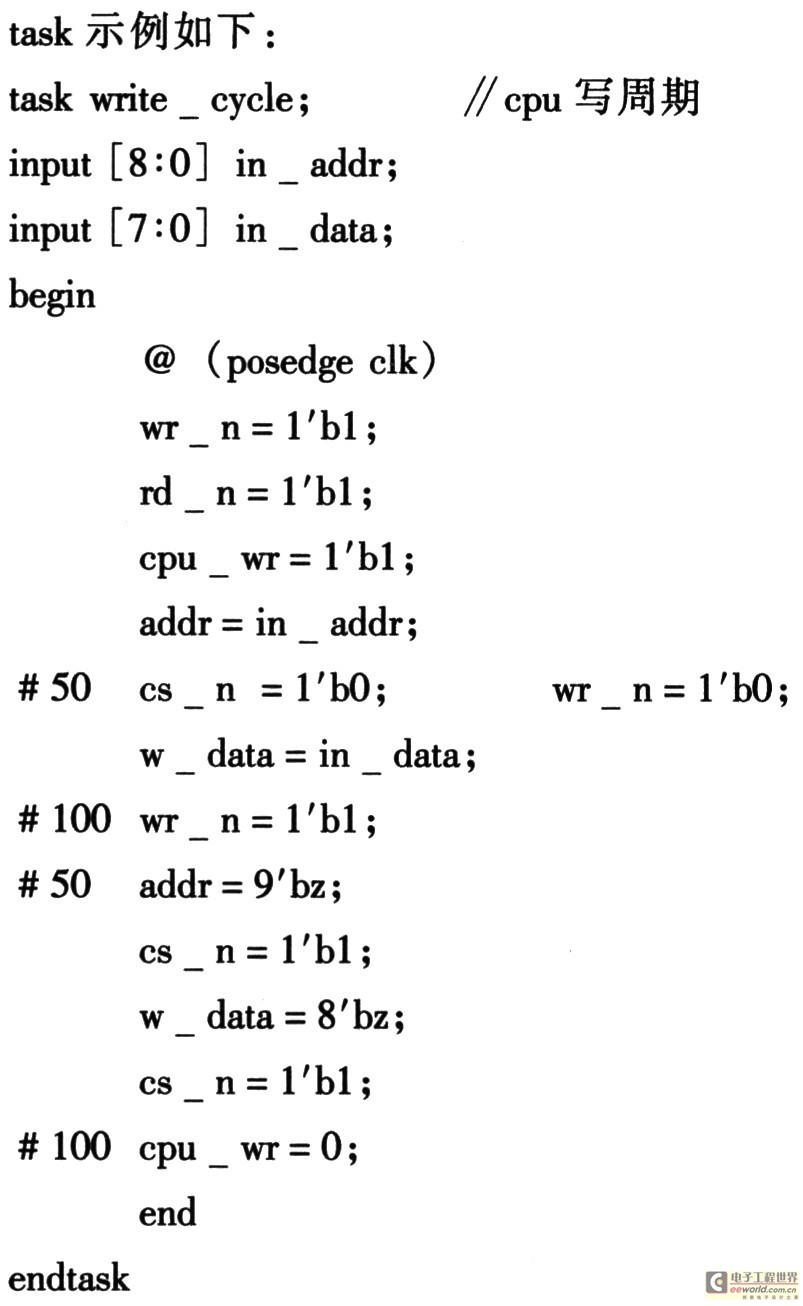

驗(yàn)證平臺(tái)總線(xiàn)功能模型中一個(gè)cpu寫(xiě)周期的

在對(duì)某個(gè)設(shè)備的寄存器進(jìn)行讀操作時(shí),譬如,向地址為ADDR的狀態(tài)寄存器寫(xiě)入DATA數(shù)據(jù),在testcase里調(diào)用該任務(wù)可以寫(xiě)成:

2.2 功能覆蓋率

功能驗(yàn)證的另一個(gè)關(guān)鍵問(wèn)題是驗(yàn)證工作到什么程度,如何保證驗(yàn)證的充分性。對(duì)于通信控制器芯片,更關(guān)心的是功能覆蓋率。功能覆蓋率是衡量設(shè)計(jì)的原始要求實(shí)現(xiàn)程度的指標(biāo)。

通信控制器功能實(shí)現(xiàn)主要體現(xiàn)在寄存器的配置組合上。前面提到,所采取的驗(yàn)證策略是在單通道下分別在Intel總線(xiàn)和:Motorola總線(xiàn)接口按照數(shù)據(jù)傳送協(xié)議為劃分標(biāo)準(zhǔn),將驗(yàn)證分為異步、同步和HDLC三大類(lèi),然后再按照數(shù)據(jù)傳送類(lèi)型,在中斷方式和DMA方式下驗(yàn)證各個(gè)功能。最后再測(cè)試全通道的數(shù)據(jù)收發(fā)。通信控制器的每一個(gè)功能均有相應(yīng)的testcase,配置寄存器的每一位都保證有翻轉(zhuǎn)。按照驗(yàn)證計(jì)劃,驗(yàn)證該通信控制器開(kāi)發(fā)的testcase共計(jì)225個(gè),通信控制器的全部功能均被覆蓋。

圖3~6示例了幾個(gè)testcase的仿真波形圖。圖3的testcase用來(lái)驗(yàn)證通信控制器Intel總線(xiàn)接口異步協(xié)議DMA傳送模式下的數(shù)據(jù)傳送,DWT(DMArequest transmit)是DMA傳送請(qǐng)求信號(hào),wrl和wr2是內(nèi)部信號(hào),當(dāng)FIFO從數(shù)據(jù)總線(xiàn)上每成功讀取8bit數(shù)據(jù)時(shí),wrl或者wr2信號(hào)跳變一次,結(jié)果顯示該testcase驗(yàn)證通過(guò)。圖4是Motorola總線(xiàn)接口異步協(xié)議中斷傳送模式下數(shù)據(jù)傳送的一個(gè)testcase,圖5是Intel總線(xiàn)接口HDLC協(xié)議中斷傳送模式下數(shù)據(jù)傳送的一個(gè)testease。與圖3的分析相類(lèi)似,波形顯示這兩個(gè)testcase驗(yàn)證通過(guò)。圖6是驗(yàn)證28個(gè)全局并口發(fā)送數(shù)據(jù)的testease,波形顯示四個(gè)并口先后發(fā)送數(shù)據(jù)55、66、77和F,該testease驗(yàn)證通過(guò)。

2.3 錯(cuò)誤狀態(tài)的驗(yàn)證

對(duì)錯(cuò)誤狀態(tài)的驗(yàn)證是一個(gè)很重要的環(huán)節(jié)。在testease中,加入錯(cuò)誤狀態(tài)激勵(lì),觀(guān)察輸出結(jié)果是否符合預(yù)期。一些錯(cuò)誤狀態(tài)比較容易實(shí)現(xiàn),如某個(gè)配置項(xiàng)賦定義以外的值,只需在配置文件相應(yīng)行上填入錯(cuò)誤狀態(tài)配置值即可。再如很短的時(shí)間內(nèi)發(fā)生了同一通道的兩次配置(即配置覆蓋),這只需在配置文件中的同一配置時(shí)刻參數(shù)段加入相同通道的又一次配置即可。另外一些錯(cuò)誤狀態(tài)可以根據(jù)通信協(xié)議自行設(shè)定,如發(fā)送端和接收端配置的數(shù)據(jù)幀頭同步字符不一致,接收時(shí)鐘和發(fā)送時(shí)鐘不同步等。

圖7是一個(gè)錯(cuò)誤狀態(tài)驗(yàn)證的testcase波形圖。該testease是驗(yàn)證通信控制器在Intel總線(xiàn)接口,同步協(xié)議的中斷方式傳送模式下數(shù)據(jù)傳送。發(fā)送端的同步幀設(shè)置為80,接收端的同步幀設(shè)置為8l。按照同步協(xié)議,同步幀不一樣,接收端的數(shù)據(jù)不能寫(xiě)入FIFO。如所預(yù)期,wrl和wr2未發(fā)生跳變,表明發(fā)送數(shù)據(jù)沒(méi)有被接收。

2.4 后仿真與樣片測(cè)試

在實(shí)際電路中,信號(hào)的跳變不是瞬間完成的,而是具有一定的時(shí)延。功能驗(yàn)證主要是驗(yàn)證電路的邏輯功能,信號(hào)的跳變是瞬間完成的,因此只能在功能上證明設(shè)計(jì)的正確性,而無(wú)法證明在實(shí)際電路中邏輯功能依然正確。后仿真是對(duì)版圖提取了寄生參數(shù)以后考慮了互聯(lián)延遲進(jìn)行的仿真。驗(yàn)證在引入實(shí)際時(shí)延之后系統(tǒng)功能是否正確。

構(gòu)建后仿真環(huán)境的思想與構(gòu)建前仿真的思想基本相同。在功能驗(yàn)證過(guò)程使用結(jié)構(gòu)化和逐層抽象的方法來(lái)設(shè)計(jì)驗(yàn)證環(huán)境,因此在后仿真的過(guò)程中可以復(fù)用前仿真的環(huán)境,測(cè)試用例也可以直接復(fù)用到后仿真的過(guò)程中。圖8是后仿真的一個(gè)波形。

采用上面介紹的驗(yàn)證方案,作者成功地對(duì)八通道多協(xié)議串行通信控制器芯片進(jìn)行了功能驗(yàn)證,該芯片已成功流片并進(jìn)行了樣片測(cè)試。將功能驗(yàn)證時(shí)各testcase芯片每個(gè)管腳的輸入以及相應(yīng)的輸出轉(zhuǎn)化為測(cè)試碼輸入測(cè)試機(jī),驗(yàn)證對(duì)于相同的輸入,芯片的實(shí)際輸出與功能驗(yàn)證時(shí)的輸出是否相符。測(cè)試碼按照測(cè)試機(jī)的要求有一定的格式給出了一行測(cè)試碼。芯片目前也通過(guò)了樣片測(cè)試并已經(jīng)實(shí)際應(yīng)用。

3 結(jié)語(yǔ)

大規(guī)模集成電路的驗(yàn)證是一項(xiàng)非常復(fù)雜的任務(wù),使用總線(xiàn)功能模型構(gòu)建可復(fù)用的驗(yàn)證平臺(tái)能夠提高集成電路的驗(yàn)證效率,縮短產(chǎn)品開(kāi)發(fā)周期。本文采用總線(xiàn)功能模型實(shí)現(xiàn)了一款八通道多協(xié)議串行通信控制器芯片的功能驗(yàn)證,相信這種方法對(duì)相關(guān)領(lǐng)域的設(shè)計(jì)驗(yàn)證具有一定的參考價(jià)值。