1 TMs320 F28335結(jié)構(gòu)特點(diǎn)

TMS320F28335采用高性能靜態(tài)CMOS技術(shù),具有150 MHz的工作頻率。系統(tǒng)組成包括:包含浮點(diǎn)運(yùn)算單元的CPU、片內(nèi)存儲(chǔ)器、中斷管理模塊、片內(nèi)集成外設(shè)。TMS320F28335的CPU采用與TMS320F28x相同的32位定點(diǎn)低功耗CPU,但其中包含一個(gè)浮點(diǎn)運(yùn)算單元(FPU),其32×32位的MAC操作及8級(jí)流水線技術(shù)使程序的執(zhí)行不用高速存儲(chǔ)器也能達(dá)到較高的速度。中斷擴(kuò)展模塊(PIE)共支持58個(gè)外設(shè)中斷,能夠快速響應(yīng)中斷。片上存儲(chǔ)器包括最高達(dá)512 kB的閃存與68 kB的RAM,代碼安全性模塊具有128位密碼保護(hù),用來保護(hù)Flash/OTP和部分SRAM,從而保證了相關(guān)寄存器的數(shù)據(jù)安全。BOOTROM中固化的代碼,提供了多種DSC啟動(dòng)方式。

TMS320F28335支持最多88個(gè)通用I/O口(GPIO),GPIO的多路開關(guān)寄存器(GPIO MUX)可以將一個(gè)引腳最多設(shè)置成4種可選工作模式:3種獨(dú)立的外設(shè)模式和1種通用的I/O模式,提高了引腳的利用率,使硬件設(shè)計(jì)時(shí)的布線更加簡便合理。GPIO0-GPIO63引腳可以連接到8路外部中斷,使DSC能夠?qū)ν獠吭O(shè)備進(jìn)行有效的中斷控制。

TMS320F28335內(nèi)部首次引入了6路直接存儲(chǔ)器存取(DMA)模塊,為數(shù)據(jù)在CPU不參與運(yùn)算的情況下在外設(shè)和存儲(chǔ)器之間進(jìn)行傳輸提供了一種硬件方法,為其他系統(tǒng)函數(shù)的執(zhí)行釋放了帶寬。另外,DMA可以重新布置內(nèi)存中的數(shù)據(jù),優(yōu)化CPU處理。DMA模塊是基于事件工作機(jī)制的,它需要外設(shè)中斷觸發(fā)開始數(shù)據(jù)傳輸,6個(gè)DMA通道可以分別設(shè)置中斷觸發(fā)源,并且每個(gè)通道包含自己的獨(dú)立PIE級(jí)中斷,以便CPU能夠控制DMA傳輸?shù)钠鹗蓟蛲瓿伞?/p>

同時(shí),TMS320F28335中包含了多種串行通信外設(shè),其中最多可以包括2個(gè)CAN通信模塊,3個(gè)SCI(UART)模塊,1個(gè)SPI模塊和2個(gè)McBSP模塊,并加入了1個(gè)I2C模塊。這些外設(shè)加強(qiáng)了DSC的通信功能,為多控制器聯(lián)接提供了豐富的資源。此外,TMS320F28335支持IDLE,STANDBY和HALT這3種低功耗工作方式,并可通過關(guān)閉各個(gè)獨(dú)立片上模塊的時(shí)鐘,降低整體功耗,適合于電池供電等低耗電量硬件系統(tǒng)。

2 硬件系統(tǒng)設(shè)計(jì)

2.1 方案概述

該系統(tǒng)主要功能是DSC通過ADC采樣芯片對(duì)12路模擬信號(hào)進(jìn)行同時(shí)采樣。在DSC中進(jìn)行數(shù)據(jù)處理后通過異步串行收發(fā)器上傳到上位機(jī)。同時(shí),上位機(jī)也可以通過異步收發(fā)器向DSC發(fā)送預(yù)先制定的命令,來控制信號(hào)處理板的工作模式和狀態(tài)。

按照功能要求,整個(gè)硬件電路可分為3部分:電源模塊、數(shù)字部分和模擬部分。其功能結(jié)構(gòu)框圖如圖1所示。

2.2 電源模塊設(shè)計(jì)

整個(gè)處理板的外部輸入電壓為5 V和±12 V,分別通過對(duì)應(yīng)的電壓轉(zhuǎn)換芯片為模擬和數(shù)字部分提供不同的電壓幅值。對(duì)于數(shù)字部分,電源模塊需要為DSC提供1.9 V的核電壓,同時(shí)為DSC的外圍和其他芯片提供3.3 V的外圍電壓。本系統(tǒng)選用LT1963AES8集成芯片提供1.9 V,LT1963AEST-3.3集成芯片提供3.3 V。對(duì)于模擬部分,系統(tǒng)要求輸入ADC的信號(hào)幅值范圍在±12V內(nèi),所以系統(tǒng)分別選用LT1086IT-12和LT11 75IT把輸入的±15V電壓轉(zhuǎn)換成±12V。

2.3 數(shù)字電路設(shè)計(jì)

數(shù)字部分電路主要是以DSC為中心的應(yīng)用電路。該部分主要是對(duì)ADC傳送的數(shù)據(jù)進(jìn)行處理、存儲(chǔ),同時(shí)完成DSC同上位機(jī)的通信和數(shù)據(jù)傳輸。由圖1可以看到,它包含以下幾個(gè)部分。外圍SRAM擴(kuò)展,EEPROM擴(kuò)展電路,SCI上位機(jī)通信接口電路。

2.3.1 外圍SRAM擴(kuò)展

考慮到TMS320F28335片內(nèi)的RAM資源有限,加上程序空間和數(shù)據(jù)空間RAM僅為34 kB,16位數(shù)據(jù)寬度,從而需要對(duì)片內(nèi)的RAM進(jìn)行擴(kuò)展,來滿足較大量程序的運(yùn)行。本系統(tǒng)選用Cypress公司的CY7C1011CV33-12ZSXE集成芯片,利用TMS320F28335提供的XINTF接口完成片外RAM的擴(kuò)展。

XINTF是TMS320F28335所提供的一個(gè)非復(fù)用異步總線,用來完成外部異步器件的擴(kuò)展。XINTF可以映射外設(shè)到3個(gè)固定的內(nèi)存映射區(qū)域,當(dāng)外部資源掛接到某個(gè)區(qū)域時(shí),則需要通過XINTF的一個(gè)片選信號(hào)來進(jìn)行外部資源的選定。

CY7C1011CV33-12ZSXE是一個(gè)CMOS的靜態(tài)RAM存儲(chǔ)器,其容量大小為64 kB,16位數(shù)據(jù)寬度。圖2是外圍SRAM擴(kuò)展電路連接圖。

如圖2所示,本系統(tǒng)選用ZONE7區(qū)域作為RAM的外圍擴(kuò)展。DSC通過其XZCS7管腳向片外SRAM發(fā)送片選信號(hào)。WE信號(hào)用來控制DSC對(duì)片外SRAM的讀寫,當(dāng)DSC的XWEo管腳為低電平,則DSC對(duì)片外RAM進(jìn)行讀寫操作;XWEo為高電平,同時(shí)DSC的XRD管腳為低電平,則為讀操作。

2.3.2 EEPROM擴(kuò)展

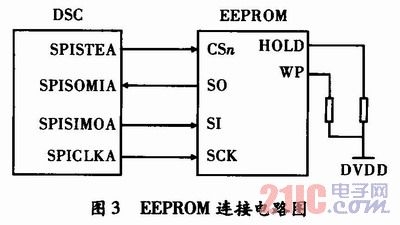

考慮到系統(tǒng)在加電后,需要對(duì)一些設(shè)備的狀態(tài)進(jìn)行一些初始化,而這些初始化的數(shù)據(jù)在設(shè)備運(yùn)轉(zhuǎn)時(shí)又需要不斷改變。因此,在設(shè)備運(yùn)轉(zhuǎn)過程中,實(shí)時(shí)將數(shù)據(jù)加以保存,以至于設(shè)備斷電后數(shù)據(jù)依舊存在。本系統(tǒng)利用TMS320F28335的SPI接口外擴(kuò)了一個(gè)EEPROM保存設(shè)備運(yùn)轉(zhuǎn)時(shí)實(shí)時(shí)獲取的初始化數(shù)據(jù)。本系統(tǒng)選用Atmel公司的AT25160集成芯片。該芯片的容量為2 kB,其寬度為8位數(shù)據(jù)寬度。模塊電路如圖3所示。

如圖3所示,DSC通過SPISTEA管腳發(fā)送片選信號(hào)選中EEPROM,通過SPICLKA管腳發(fā)送SPI傳輸時(shí)鐘,而數(shù)據(jù)的寫入和讀出則分別通過SPIS-IMOA和SPISOMIA管腳完成。EEPROM中的HOLD管腳用來暫停與主設(shè)備間串行數(shù)據(jù)傳輸,WP管腳則用來進(jìn)行對(duì)EEPROM的寫保護(hù),如果其為低電平,則主機(jī)無法向其寫人數(shù)據(jù)。系統(tǒng)對(duì)兩管腳輸入高電平,保證EEPROM在讀寫操作過程中一直可以進(jìn)行而不被中斷。

2.3.3 SCI上位機(jī)通信接口

為了實(shí)現(xiàn)上位機(jī)同DSC異步的通信和數(shù)據(jù)傳輸,本系統(tǒng)利用TMS320F28335所提供的SCI接口來完成所需要求。SCI是一個(gè)2線的異步串行端口,即常說的UART。其數(shù)據(jù)的收發(fā)支持全雙工通信,內(nèi)部收發(fā)均有一個(gè)16級(jí)的FIFO來緩存數(shù)據(jù)。為了保證數(shù)據(jù)可靠,SCI提供奇偶校驗(yàn),數(shù)據(jù)溢出檢測(cè)等操作。SCI接口輸出信號(hào)的電平是LV—TTL電氣標(biāo)準(zhǔn),通過RS232收發(fā)轉(zhuǎn)換器加以驅(qū)動(dòng),獲得RS232電氣標(biāo)準(zhǔn)的信號(hào),以便上位機(jī)接收。

2.4 模擬電路設(shè)計(jì)

模擬部分電路主要是以ADC為中心的應(yīng)用電路。其主要實(shí)現(xiàn)模擬信號(hào)的處理,采集等工作。其中核心部分為AD轉(zhuǎn)換。

AD轉(zhuǎn)換部分,主要是通過數(shù)字采樣來完成模擬信號(hào)到數(shù)字信號(hào)的轉(zhuǎn)變。本系統(tǒng)選用的ADC芯片是美國模擬電氣公司的AD7656。模數(shù)轉(zhuǎn)換芯片AD7656是高集成度、6通道6 bit逐次逼近(SAR)型ADC,內(nèi)含1個(gè)2.5 V基準(zhǔn)電壓和基準(zhǔn)緩沖器。該器件的功耗比最接近的同類雙極性ADC降低了60%。AD7656在每通道250kb·s-1采樣速率下的精度是同類產(chǎn)品的兩倍。可以由引腳和軟件選擇模擬電壓范圍:10 V或5 V;模擬電源電壓范圍為4.75~5.25 V,因而大范圍的工作電壓使其無需電平轉(zhuǎn)換等其他措施便可以直接與DSC相連;提供有并行和串行接口。可以工作在-40~85℃。標(biāo)準(zhǔn)模式5 V供電,250 kb·s-1時(shí)的功耗為140 mW,待機(jī)時(shí)僅為100μW。基于iCOMS技術(shù)制造的AD7656可以滿足工業(yè)領(lǐng)域?qū)Ψ直媛省⒍嗤ǖ馈⑥D(zhuǎn)換速率和功耗等方面的較高要求。

AD7656支持和DSC的并口、串口數(shù)據(jù)傳輸,通過SER/PAR SEL管腳的高低電平的選擇,來控制采樣后數(shù)字信號(hào)的傳輸方式。當(dāng)其為高電平,則使用串行傳輸方式,反之則使用并行傳輸方式。本系統(tǒng)選用并行傳輸方式。在具體的轉(zhuǎn)換過程中,每片AD7656內(nèi)部的6條采樣通路可以分為A、B、C共3組,其中每組通路包含2路通路。3組通路可以同時(shí)采樣,也可以單獨(dú)采樣,而每組內(nèi)的兩條通路同時(shí)采樣。管腳CONVSTA,CONVSTB,CONVSTC分別用來對(duì)A、B、C采樣通路進(jìn)行控制。當(dāng)一個(gè)上升沿電平到達(dá)任一管腳,則該管腳對(duì)應(yīng)模數(shù)轉(zhuǎn)換的2路通路被啟動(dòng),開始完成模數(shù)轉(zhuǎn)換。當(dāng)把三管腳連接,3組采樣通路,即所有的6條采樣通路同時(shí)采樣。系統(tǒng)選用3組通路同時(shí)采樣。

當(dāng)DSC連接有多片ADC時(shí),則需要通過CS片選管腳來進(jìn)行ADC的選擇。當(dāng)采樣開始,BUSY管腳將從低電平變?yōu)楦唠娖剑谡麄€(gè)采樣的過程中,BUSY一直保持高電平,當(dāng)采樣結(jié)束,BUSY則從高電平變?yōu)榈碗娖剑藭r(shí)DSC就可以開始讀取數(shù)據(jù)。本系統(tǒng)則利用該管腳作為DSC外部中斷源的輸入管腳。當(dāng)BUSY上電平由高變低,則通知DSC產(chǎn)生中斷,來進(jìn)行數(shù)據(jù)的讀取。

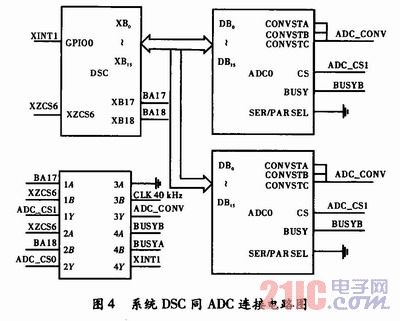

本系統(tǒng)選用2片AD7656完成12路數(shù)據(jù)采樣,通過DSC的XINTF ZONE6把ADC設(shè)備映射到DSC上,進(jìn)行數(shù)據(jù)傳輸。通過地址譯碼和邏輯控制實(shí)現(xiàn)2片ADC同DSC的連接。具體結(jié)構(gòu)如圖4所示。

圖4中左下角為邏輯部分,通過DSC的地址線BA17和BA18完成對(duì)ADC的選擇。可以得到ADC0和ADC1在DSC中的地址映射為0x180000和0x1400 00。而外部輸入40 kHz的時(shí)鐘,作為ADC的采樣頻率。兩個(gè)ADC對(duì)應(yīng)DSC的同一個(gè)中斷,當(dāng)任意一片ADC采樣完畢,都會(huì)引起DSC的中斷,從而進(jìn)行采樣數(shù)據(jù)的讀取。

3 系統(tǒng)軟件設(shè)計(jì)

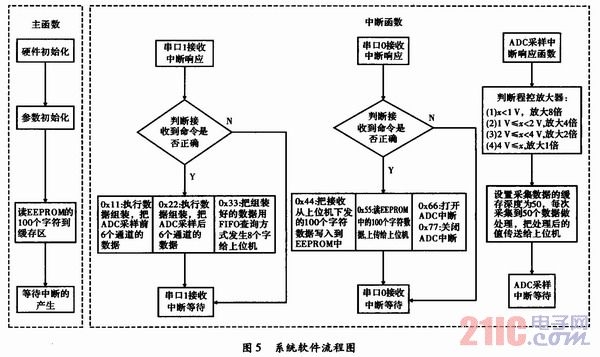

如前所述,整個(gè)信號(hào)處理板一共有12路模擬信號(hào)通路,通過傳感器接收到12路模擬信號(hào)。2片AD7656把12路模擬信號(hào)轉(zhuǎn)換為數(shù)字信號(hào)傳送給TMS320F28335,在TMS320F28335中對(duì)這些采集到的數(shù)據(jù)做相應(yīng)處理后通過SCI傳送給上位機(jī)。同時(shí)對(duì)有必要保存的數(shù)據(jù)通過SPI接口保存到EEPROM中。整個(gè)采集、通信過程由上位機(jī)發(fā)送相關(guān)的命令來加以控制。程序的流程如圖5所示。

在主函數(shù)中,程序首先完成相應(yīng)模塊的初始化,設(shè)定好CPU運(yùn)行的時(shí)鐘,選定好各個(gè)模塊的工作模式,然后讀取EEPROM中的設(shè)備初始化數(shù)據(jù),后進(jìn)行入等待狀態(tài)。此時(shí)CPU等待ADC采樣的數(shù)據(jù),當(dāng)ADC采樣過程結(jié)束,則進(jìn)入ADC中斷響應(yīng)函數(shù),在此函數(shù)中,主要完成數(shù)據(jù)的讀取,對(duì)于小信號(hào),通過程控放大器放大其幅值,然后存儲(chǔ)到自定義的緩存區(qū)中。兩個(gè)串口工作方式均由上位機(jī)發(fā)送命令,從而觸發(fā)SCI的串口收中斷服務(wù)函數(shù)。然后在中斷服務(wù)函數(shù)中完成對(duì)應(yīng)命令要求。系統(tǒng)選用串口1完成采集數(shù)據(jù)向上位機(jī)的傳輸,串口0完成向EEPROM發(fā)送需保存的數(shù)據(jù)和一些相關(guān)操作。而SCI0和SCI1分別對(duì)應(yīng)DSC外設(shè)中斷的INT9.1和INT9.3,外部中斷XINT1對(duì)應(yīng)INT1.4。程序設(shè)置兩個(gè)串口的傳輸速率均為38.4 kb·s-1。

在設(shè)備工作時(shí),由于SCI1的中斷源是上位機(jī)的命令發(fā)送,系統(tǒng)規(guī)定上位機(jī)每20ms發(fā)送一個(gè)數(shù)據(jù)接受命令,因此SCI1的中斷響應(yīng)周期為td= 20 ms。而由于采樣率為40 kHz,因此ADC的中斷服務(wù)函數(shù)響應(yīng)周期為0.025 ms。系統(tǒng)規(guī)定采集一組數(shù)據(jù)的個(gè)數(shù)為50,那么采集一組數(shù)據(jù)的時(shí)間即為tc=1.25 ms,所以在一次SCI1中斷過程中,ADC會(huì)采集16組數(shù)據(jù)。考慮到串口傳輸?shù)牟ㄌ芈蕿?8.4kb·s-1,因此傳送一個(gè)16位的數(shù)據(jù)時(shí)間為tt=0.417 ms。而一組數(shù)據(jù)采集時(shí)間加上串口數(shù)據(jù)傳輸?shù)臅r(shí)間為tc+tt=1.667 ms<

所設(shè)計(jì)的信號(hào)處理板以TMS320F28335為核心處理器,利用AD7656完成模擬信號(hào)采樣的功能硬件平臺(tái)。TMS320F28335片內(nèi)集成了豐富的外圍資源,通過驅(qū)動(dòng)軟件的配置和硬件系統(tǒng)的設(shè)計(jì),可以方便、高效地完成大量數(shù)字信號(hào)的處理和運(yùn)算。AD7656的6路模擬信號(hào)采集和16位高精度的模擬信號(hào)采樣,較好地完成了模擬信號(hào)的數(shù)字化轉(zhuǎn)換,減少了模擬信號(hào)采樣的失真。實(shí)驗(yàn)證明,信號(hào)處理板所采集到的數(shù)字信號(hào)的誤差值約為1.37 mV,可達(dá)14位的采樣精度。