l 前言

隨著電子技術(shù)的快速發(fā)展,對通信系統(tǒng)功能的要求不斷提高。基于同樣的硬件環(huán)境,由軟件來完成不同的通信功能的方式趨于成熟,通過改變程序可以很靈活地更改通信系統(tǒng)的功能和性能。于是,可編程高速器件如DSP,ARM等成了現(xiàn)代數(shù)據(jù)通信系統(tǒng)的主要角色。數(shù)字調(diào)制是用載波信號(hào)的某些離散狀態(tài)來表征所傳送的信息,然后在接收端對載波信號(hào)的離散調(diào)制參量進(jìn)行檢測。

四相相移鍵控(QPSK)方式已經(jīng)在數(shù)字調(diào)制技術(shù)中占有越來越重要的地位,該調(diào)制方式廣泛應(yīng)用于衛(wèi)星通信、電纜調(diào)制解調(diào)、視頻會(huì)議系統(tǒng)、蜂窩電話和其他數(shù)字通信等領(lǐng)域。它具有適中的頻譜利用率,很低的比特錯(cuò)誤率。由于高速數(shù)字信號(hào)處理器(如TI公司TMS320系列)的廣泛應(yīng)用,為數(shù)字方式實(shí)現(xiàn)調(diào)制解調(diào)器提供了有利的條件,同時(shí)省去了大量的硬件電路,如環(huán)型濾波器,VCO等。在DSP技術(shù)的支持下很容易實(shí)現(xiàn)。

2 QPSK的基本原理與算法

2.1 絕對正交相移鍵控(QPSK)

在絕對相移鍵控方式中,表達(dá)式為:

![]()

式中I(t)是同相支路信號(hào),Q(t)是正交支路信號(hào)。

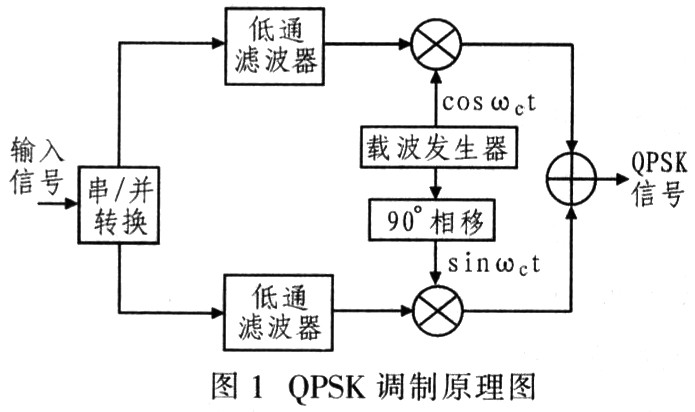

圖1給出實(shí)現(xiàn)QPSK調(diào)制的原理。輸入的二進(jìn)制數(shù)字信號(hào)經(jīng)過串并轉(zhuǎn)換電路分為兩路速率減半的雙極性信號(hào):同相信號(hào)I(t)和正交信號(hào)Q(t),經(jīng)低通濾波成形后分別與相互正交的兩路載波信號(hào)相乘,然后相加即可得到QPSK信號(hào),也可以采用相位選擇法來實(shí)現(xiàn)QPSK信號(hào),輸入的二進(jìn)制數(shù)字信號(hào)經(jīng)串/并轉(zhuǎn)換后,成為雙比特碼元,而載波發(fā)生器產(chǎn)生4種不同相位的載波波形,根據(jù)雙比特碼元的不同組合.每個(gè)比特周期從4種不同相位的載波中選擇一種輸出,然后經(jīng)帶通濾波器濾除帶外干擾信號(hào),就得到QPSK信號(hào),這種方式適用于載波頻率較高的場合。

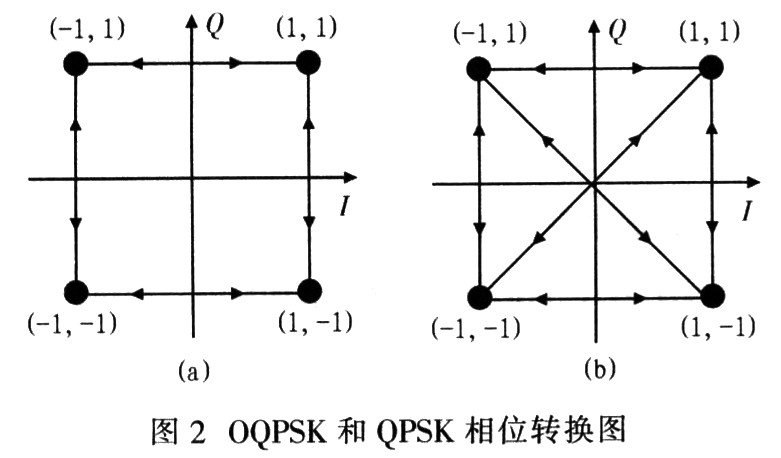

設(shè)原始數(shù)據(jù)流為dk(t)=d0d2d2…,取雙極性脈沖序列。其值為+1或一1,分別代表O或1,dk(t)經(jīng)數(shù)據(jù)分離器分成奇偶兩路,dI(t)=d0d2d4…和dQ(t)=d1d3d5…,每路的碼元寬度擴(kuò)展為2T。其中,奇數(shù)路數(shù)據(jù)d0(t)經(jīng)過時(shí)延送入O信道,對載波sinωct進(jìn)行二相調(diào)制;偶數(shù)路數(shù)據(jù)dI(t)送入I信道,對載波cosωct進(jìn)行二相調(diào)制。然后2個(gè)信號(hào)相加得到四相信號(hào)。碼元轉(zhuǎn)換時(shí),QPSK信號(hào)的相位可能產(chǎn)生90°的跳變,也可能產(chǎn)生180°的跳變,前者發(fā)生在2個(gè)信道的一路數(shù)據(jù)改變極性時(shí),后者發(fā)生在2個(gè)信道的數(shù)據(jù)同時(shí)改變極性時(shí)。

2.2 偏移正交相移鍵控(OQPSK)

在絕對相移鍵控(QPSK)的調(diào)制中,輸入的二進(jìn)制信號(hào)經(jīng)過串并轉(zhuǎn)換后得到的I,Q兩路數(shù)據(jù)是相互對齊的,當(dāng)輸入的數(shù)據(jù)由00變?yōu)?1或由Ol跳變?yōu)?0,即I,Q兩路數(shù)據(jù)同時(shí)出現(xiàn)跳變時(shí),輸出調(diào)制信號(hào)的相位會(huì)出現(xiàn)π的跳變,其相位變化關(guān)系由圖2(b)給出,信號(hào)在經(jīng)過限帶后有可能出現(xiàn)包絡(luò)為0的現(xiàn)象,從而使頻譜擴(kuò)展,會(huì)對相鄰信號(hào)產(chǎn)生干擾。另外在傳統(tǒng)的鎖相環(huán)恢復(fù)電路中,可能造成本地載波的相位模糊,使解調(diào)后的信號(hào)出現(xiàn)錯(cuò)誤,還要采取措施消除相位模糊,所以實(shí)際應(yīng)用中較少使用絕對相移鍵控。在第二代的窄帶CDMA(IS一95)系統(tǒng)中,下行鏈路采用QPSK方式,上行鏈路采用OQPSK方式。

圖3給出0QPSK的調(diào)制原理。在OQPSK調(diào)制中,輸入的數(shù)據(jù)先做串/并轉(zhuǎn)換,分成I、Q兩路,然后對Q支路的數(shù)據(jù)延時(shí)半個(gè)碼元周期,后面和QPSK方式一樣。這樣每個(gè)碼元周期內(nèi)I、Q兩路信號(hào)中只可能有一路發(fā)生變化,調(diào)制后信號(hào)的相位跳變不會(huì)出現(xiàn)π相位跳變。

3 硬件系統(tǒng)設(shè)計(jì)

3.1 硬件組成

(1)核心板核心板主要由一塊DSP組成,采用TI公司的TMS320VC5416。該器件采用增強(qiáng)型哈佛結(jié)構(gòu),片內(nèi)共有8條總線(1條程序總線、3條數(shù)據(jù)總線和4條地址總線),具有功耗小,高度并行等優(yōu)點(diǎn);片內(nèi)有128 K字節(jié)的ROM,16 K字節(jié)的DARAM,3個(gè)多通道緩沖串口(McBSPs),加強(qiáng)型的8/16位并行主機(jī)接口(HPI),16位可編程定時(shí)器,支持外部總線到內(nèi)部存儲(chǔ)器的DMA操作。該器件外圍輸入輸出電平為3.3 V,內(nèi)核電壓為1.8 V。

(2)電源部分 穩(wěn)壓電源電路采用5 V直流供電,通過AMSll7電源轉(zhuǎn)換器分別轉(zhuǎn)換成3.3 V和1.8 V。因存在模擬和數(shù)字2種信號(hào),同時(shí)需要模擬和數(shù)字供電,系統(tǒng)中利用2個(gè)10μH的電感將這2種電源分離,以免產(chǎn)生相互干擾。

(3)MCU部分 MCU采用STC公司的89LE58RD,其供電電壓為3.3 V,具有32個(gè)I/O引腳,20 K字節(jié)的片內(nèi)ROM,256字節(jié)片內(nèi)RAM。89LE58RD通過異步串口與PC機(jī)相連,其輸入輸出電平為TTL標(biāo)準(zhǔn),通信線路上的數(shù)據(jù)信號(hào)采用RS一232C電平標(biāo)準(zhǔn)。系統(tǒng)采用MAX202進(jìn)行電平標(biāo)準(zhǔn)轉(zhuǎn)換。

(4)A/D,D/A轉(zhuǎn)換采用D/A和A/D轉(zhuǎn)換器,該模塊選用了ADI公司的AD7303,它是一個(gè)8位雙通道電壓輸出D/A轉(zhuǎn)換器,最高工作時(shí)鐘為30 MHz。AD7303內(nèi)部有1個(gè)16位的移位寄存器、2個(gè)輸入寄存器和2個(gè)D/A轉(zhuǎn)換寄存器。16位移位寄存器的低8位(DB0~DB7)用來存儲(chǔ)待轉(zhuǎn)換的數(shù)字量,高8位(DB8~DBl5)是控制碼,通過控制碼選擇通道和不同的數(shù)據(jù)裝載方式,通過控制位LDC、A/B、CRl和CR0設(shè)置為兩路輸出方式。AD7303采用SPI方式與。DSP的多路緩沖串口(McBSP)相接。

(5)SRAM 靜態(tài)存儲(chǔ)SRAM采用IS6lLV25616,其速度為10 ns,存儲(chǔ)空間為256 K字節(jié),供電電壓為3.3 V。

3.2 實(shí)現(xiàn)方案

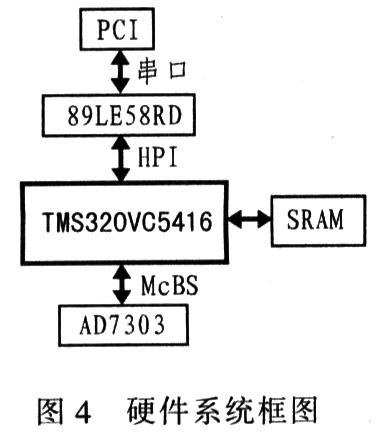

圖4給出調(diào)制實(shí)驗(yàn)系統(tǒng)總體設(shè)汁框圖。PC機(jī)為通信終端;單片機(jī)用來控制數(shù)據(jù)收發(fā);DSP運(yùn)行QPSK等相關(guān)算法;SRAM用來存儲(chǔ)算法及相關(guān)數(shù)據(jù)。當(dāng)系統(tǒng)重新加電時(shí),自動(dòng)把程序及相關(guān)數(shù)據(jù)導(dǎo)入到DSP中。PC機(jī)通過異步串口連接單片機(jī),利用串口調(diào)試軟件如“串口調(diào)試助手”,即可與單片機(jī)交換數(shù)據(jù)。單片機(jī)一方面與PC機(jī)交換數(shù)據(jù),另一方面則直接通過HPI接口從DSP內(nèi)存中讀寫數(shù)據(jù)。這樣DSP與PC機(jī)通信不需花費(fèi)時(shí)間,大大節(jié)省了DSP的資源。DSP利用多通道緩沖串行口McBSP發(fā)送數(shù)據(jù)給D/A轉(zhuǎn)換器,以便在模擬線路上進(jìn)行傳輸。

4 QPSK的設(shè)計(jì)與實(shí)現(xiàn)

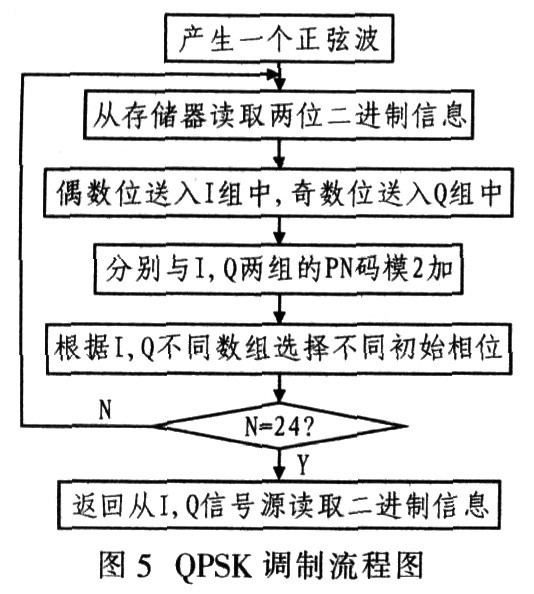

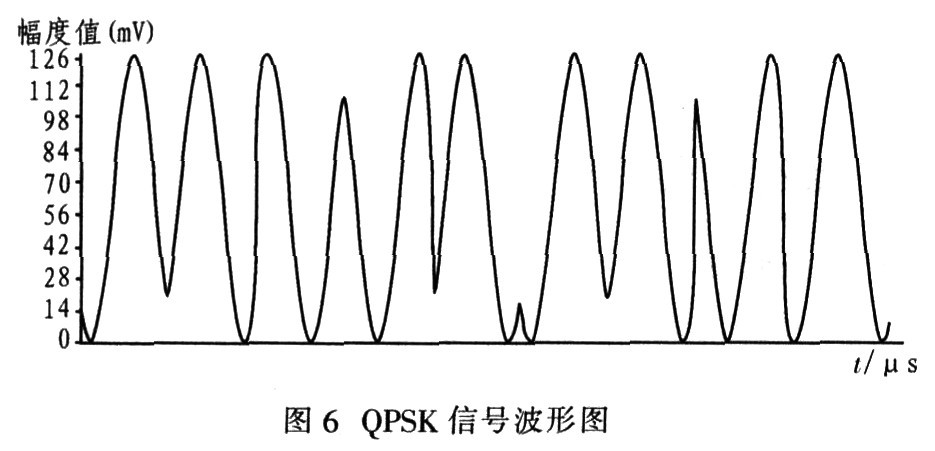

QPSK信號(hào)可看成是2個(gè)BPSK信號(hào)之和,它有4種不同的初始相位。首先在DSP中產(chǎn)生1個(gè)正弦波,然后從已經(jīng)存入存儲(chǔ)器的數(shù)據(jù)中每次讀出2位二進(jìn)制信息,串并轉(zhuǎn)換輸入的二進(jìn)制信息,把偶數(shù)位信息放人數(shù)組I(同相支路)中,奇數(shù)位信息放入數(shù)組Q(正交支路)中,把產(chǎn)生的I、Q兩路的一部分PN碼片分別存儲(chǔ)于DSP內(nèi)部存儲(chǔ)器,經(jīng)過串/并轉(zhuǎn)換后的二進(jìn)制信息與存儲(chǔ)器中的I、Q兩路的。PN碼片分別進(jìn)行模2加運(yùn)算,實(shí)現(xiàn)短碼擴(kuò)頻,短碼擴(kuò)頻后省去了低通濾波器,可直接正交調(diào)制,設(shè)計(jì)中采用了選相的方式,即根據(jù)擴(kuò)頻后的I、Q兩路的信息進(jìn)行選相。選相時(shí)I、Q的組合采用格雷編碼方式,當(dāng)I=0、Q=0時(shí)選擇初始相位0;當(dāng)I=0、Q=1時(shí)選擇初始相位π/2;當(dāng)I=l、Q=1時(shí)選擇初始相位π;當(dāng)I=1、Q=0時(shí)選擇初始相位3π/2。為保證每個(gè)碼元都能有完整的波形輸出,存儲(chǔ)的正弦波為兩個(gè)周期。1個(gè)周期有64個(gè)點(diǎn),初始相位為0,相當(dāng)于從第16個(gè)點(diǎn)開始連續(xù)讀1個(gè)周期正弦波。圖5是QPSK調(diào)制流程圖,圖6是調(diào)制后的QPSK信號(hào)波形圖,是在CCS仿真軟件中看到的波形圖。圖6中的縱坐標(biāo)為幅度值,單位為mV;橫坐標(biāo)為時(shí)間軸,單位為μs。

5 結(jié)語

實(shí)驗(yàn)證明,基帶數(shù)字調(diào)制算法QPSK系統(tǒng)達(dá)到了設(shè)計(jì)要求,且能提供較高性能。但因缺少射頻模塊及天線,該平臺(tái)不能在無線信道上調(diào)試和實(shí)驗(yàn),這是下一步研究目標(biāo)。