不同傳感網(wǎng)絡(luò)的應(yīng)用有著不同MAC協(xié)議,其中IEEE802.15.4是最具代表性的協(xié)議。本文給出了用FPGA的控制邏輯來實(shí)現(xiàn)無線傳感器網(wǎng)絡(luò)MAC控制器的設(shè)計(jì)方法,并最終實(shí)現(xiàn)了符合IEEE802.15.4協(xié)議的控制器。

1 總體設(shè)計(jì)方案

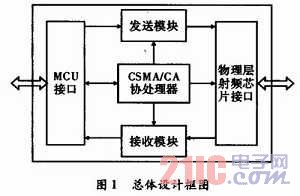

無線傳感器網(wǎng)絡(luò)控制器的FPGA設(shè)計(jì)包括無線傳感器網(wǎng)絡(luò)MAC子層的FPGA設(shè)計(jì)、MAC子層與上層協(xié)議的接口設(shè)計(jì)以及與物理層(PHY)的接口設(shè)計(jì)。該無線傳感器網(wǎng)絡(luò)的總體結(jié)構(gòu)設(shè)計(jì)如圖1所示。整個(gè)系統(tǒng)分為發(fā)送模塊、接收模塊、CSMA/CA協(xié)處理器模塊、PHY接口模塊和MCU接口模塊5個(gè)部分。發(fā)送模塊和接收模塊主要完成MAC幀的發(fā)送和接收功能,包括MAC幀的封裝和解包,它直接提供了到外部物理層芯片(PHY)的串行接口。CSMA/CA協(xié)處理器是MAC的核心,控制接收和發(fā)送狀態(tài)機(jī)協(xié)調(diào)半雙工收發(fā)控制,并且通過程序執(zhí)行的方式完成CSMA—CA算法。

2 模塊實(shí)現(xiàn)

2.1 MAC發(fā)送模塊

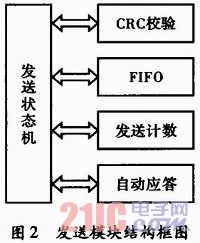

發(fā)送模塊可將上層協(xié)議提供的數(shù)據(jù)封裝之后通過PHY接口發(fā)送給PHY。發(fā)送狀態(tài)機(jī)按照幀的格式將數(shù)據(jù)進(jìn)行封裝,分別在數(shù)據(jù)的前端添加前導(dǎo)序列和幀起始分隔符以及在數(shù)據(jù)的后端添加CRC校驗(yàn)值,封裝后的整個(gè)數(shù)據(jù)包以串行格式發(fā)送出去。因此,發(fā)送部分的功能包括前導(dǎo)序列和幀起始分隔符插入、CRC計(jì)算、幀發(fā)送和自動(dòng)應(yīng)答等功能。

發(fā)送模塊包括發(fā)送FIFO(First In First Out)緩存器模塊(Tx_FIFO)、發(fā)送狀態(tài)機(jī)模塊(Tx_FSM)、自動(dòng)應(yīng)答模塊(Tx_Ack)、發(fā)送計(jì)數(shù)器模塊(Tx_Counter)和CRC計(jì)算模塊(Tx_Crc)等5個(gè)子模塊。其內(nèi)部結(jié)構(gòu)如圖2所示。

2.1.1 發(fā)送狀態(tài)機(jī)Tx_FSM

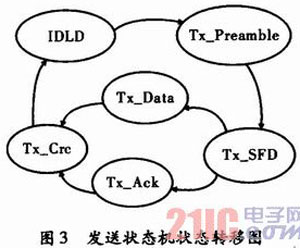

Tx_FSM是整個(gè)發(fā)送模塊的狀態(tài)機(jī),它是整個(gè)發(fā)送模塊的核心,主要用于產(chǎn)生發(fā)送過程中各個(gè)模快的控制信號(hào)。發(fā)送的狀態(tài)轉(zhuǎn)移,如圖3所示。TxCSP_en是來自MAC控制部分CSMA/CA協(xié)處理器的發(fā)送狀態(tài)機(jī)控制信號(hào)。當(dāng)TxCSP_en信號(hào)為高電平時(shí),啟動(dòng)狀態(tài)機(jī),開始幀的發(fā)送過程。

(1)IDLE:初始狀態(tài)。當(dāng)發(fā)送狀態(tài)機(jī)上電復(fù)位或者成功接收到數(shù)據(jù)包時(shí),進(jìn)入此狀態(tài)。如果收到TxCSP_en信號(hào)時(shí),開始數(shù)據(jù)發(fā)送過程,否則,保持此狀態(tài)。

(2)Tx_Preamble:發(fā)送前導(dǎo)序列。當(dāng)狀態(tài)機(jī)將跳變到此狀態(tài),開始向數(shù)據(jù)線上發(fā)送符合特定組合的前導(dǎo)碼序列。IEEE802.15.4協(xié)議的幀格式的前導(dǎo)序列是4 Byte O。

(3)Tx_SFD:發(fā)送幀起始分隔符。在這個(gè)狀態(tài)下開始發(fā)送幀的幀起始符,IEEE802.15.4協(xié)議的幀格式的幀起始符為10100111。同時(shí)啟動(dòng)計(jì)數(shù)器,對該過程進(jìn)行計(jì)數(shù)。

(4)Tx_Data:發(fā)送數(shù)據(jù)幀MPDU部分。這個(gè)狀態(tài)下發(fā)送幀的有效數(shù)據(jù),這個(gè)有效數(shù)據(jù)是來自上層。當(dāng)發(fā)送完8位有效數(shù)據(jù)后,便產(chǎn)生讀取FIFO緩存信號(hào),從接收FIFO讀取1Byte數(shù)據(jù)。

(5)Tx_Crc:發(fā)送數(shù)據(jù)包的CRC校驗(yàn)位。在這個(gè)狀態(tài)下,發(fā)送幀的16位CRC校驗(yàn)碼。

(6)Tx_Ack:發(fā)送應(yīng)答狀態(tài)。如果接收到的幀有應(yīng)答要求,則啟動(dòng)該狀態(tài)。

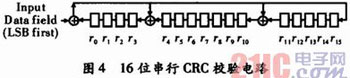

2.1.2 CRC校驗(yàn)電路

通過使用16位CRC串行校驗(yàn)來進(jìn)行幀的差錯(cuò)校驗(yàn),其中校驗(yàn)多項(xiàng)式采用。將要傳送幀的MPDU通過CRC校驗(yàn)?zāi)K,便產(chǎn)生了16位CRC校驗(yàn)碼。16位串行CRC校驗(yàn)電路如圖4所示。

2.1.3 發(fā)送模塊的仿真結(jié)果

圖5是發(fā)送模塊的仿真結(jié)果,Tx_clk是來自PHY接口的發(fā)送時(shí)鐘,s_out是幀以串行方式發(fā)送。最先發(fā)送的前導(dǎo)序列碼,接下來幀起始分隔符,再就是數(shù)據(jù)位,最后是CRC檢驗(yàn)位。

2.2 MAC接收模塊

接收模塊的主要功能:接收并識(shí)別從串行數(shù)據(jù)線上輸入的符合IEEE802.15.4協(xié)議格式的幀。如果協(xié)處理器RxCSP_en信號(hào)有效,則啟動(dòng)數(shù)據(jù)接收過程。通過接收狀態(tài)機(jī)的控制,按幀格式順序接收不同的數(shù)據(jù)域。當(dāng)接收到1Byte數(shù)據(jù)后,且Rx_fifowrite信號(hào)有效時(shí),數(shù)據(jù)被寫入到接收緩存RxFIFO中。

接收狀態(tài)機(jī)產(chǎn)生整個(gè)接收過程所需要的控制信號(hào),在控制信號(hào)的作用下將接收到的幀存儲(chǔ)到RxFIFO。接收部分的狀態(tài)轉(zhuǎn)移如圖6所示。

(1)IDIE:初始狀態(tài)。當(dāng)接收狀態(tài)機(jī)上電復(fù)位或者成功接收到幀時(shí),進(jìn)入到此狀態(tài)。收到RxCSP_en信號(hào)時(shí),開始數(shù)據(jù)接收過程。

(2)Rx_Preamhle:接收前導(dǎo)序列。啟動(dòng)序列檢測器,開始檢測數(shù)據(jù)線上符合IEEE802.15.4協(xié)議的序列。

(3)Rx_Length:接收數(shù)據(jù)幀長度。在這個(gè)狀態(tài)下,開始接收數(shù)據(jù)的長度,同時(shí)存入計(jì)數(shù)器寄存器。

(4)Rx_MPDU:接收數(shù)據(jù)幀MPDU部分。這個(gè)狀態(tài)下,接收幀的有效數(shù)據(jù)。每接收到1Byte有效數(shù)據(jù)后,便產(chǎn)生接收FIFO緩存寫信號(hào),同時(shí)將數(shù)據(jù)寫入到接收FIFO。如果接收數(shù)據(jù)CRC校驗(yàn)有誤或者接收過程中發(fā)生堵塞現(xiàn)象,則狀態(tài)機(jī)退回到初始狀態(tài)。

(5)Rx_CRC_CHECK:接收CRC校驗(yàn)。接收數(shù)據(jù)包的CRC校驗(yàn)碼,同時(shí)啟動(dòng)CRC校驗(yàn)的過程。

(6)Rx_RSSI_PAD:幀末尾RSSI值填充。計(jì)算RSSI強(qiáng)度值,并附著CRC校驗(yàn)結(jié)果,將該字節(jié)填入接收FIFO。

(7)Rx_CRC_PAD:CRC狀態(tài)和Correlation值填充。

2.3 CSMN/CA協(xié)處理器模塊

CSMA/CA協(xié)處理器是MAC控制器設(shè)計(jì)中的核心模塊。協(xié)處理器主要包括指令寄存器、4個(gè)輔助寄存器以及控制信號(hào)產(chǎn)生模塊。通過指令寄存器、4個(gè)輔助寄存器與系統(tǒng)CPU接口的功能。同時(shí),控制信號(hào)產(chǎn)生模塊產(chǎn)生MAC控制器發(fā)送和接收模塊所需要的控制信號(hào)。

MAC控制器包括4種工作狀態(tài):

(1)睡眠狀態(tài):在該狀態(tài)下,除協(xié)處理器模塊外,所有子模塊的時(shí)鐘都將停止,從而降低功耗。只有當(dāng)協(xié)處理器執(zhí)行發(fā)送使能指令或接收使能指令時(shí),才離開睡眠狀態(tài)。

(2)發(fā)送狀態(tài):當(dāng)協(xié)處理器執(zhí)行發(fā)送使能指令時(shí),進(jìn)入發(fā)送狀態(tài)。如果一幀發(fā)送完成,則自動(dòng)轉(zhuǎn)入接收狀態(tài)。

(3)接收狀態(tài):當(dāng)協(xié)處理器執(zhí)行接收使能指令時(shí),進(jìn)入接收狀態(tài)。因?yàn)榻邮諣顟B(tài)是主要的工作狀態(tài),所以在成功接收完一幀或幀校驗(yàn)失敗后依然處于接收狀態(tài)。

(4)發(fā)送應(yīng)答幀狀態(tài):當(dāng)協(xié)處理器執(zhí)行應(yīng)答指令時(shí),進(jìn)入到此狀態(tài)。

無論在那種狀態(tài),一旦執(zhí)行了休眠指令,控制器立即進(jìn)入睡眠狀態(tài)。

2.4 接口模塊

接口模塊分為和系統(tǒng)MCU的特殊功能寄存器接口以及和與物理層芯片的物理接口。MCU要想控制MAC控制器的運(yùn)行,就必須采用一種接口與它進(jìn)行通信,本文采用SPI接口。

SPI(Serial Peripheral Interface)是一種串行外圍設(shè)備接口,是Motorola首先在其MC68HCXX系列處理器上定義的。優(yōu)點(diǎn)如下:第一,它是一種高速的,全雙工,同步的通信總線;第二,它只占用4根線,節(jié)約了芯片的管腳,同時(shí)為PCB的布局上節(jié)省空間。SPI接口主要應(yīng)用在EEPROM,F(xiàn)lash,實(shí)時(shí)時(shí)鐘,A/D轉(zhuǎn)換器,還有數(shù)字信號(hào)處理器和數(shù)字信號(hào)解碼器之間。

SPI的通信原理:它以主從方式工作,這種模式通常有一個(gè)主設(shè)備,一個(gè)或多個(gè)從設(shè)備,需要至少4根線。

(1)SEL:從設(shè)備使能信號(hào),由主設(shè)備控制。

(2)MOSI:主設(shè)備數(shù)據(jù)輸出,從設(shè)備數(shù)據(jù)輸入。

(3)MISO:主設(shè)備輸入,從設(shè)備數(shù)據(jù)輸出。

(4)SCLK:時(shí)鐘信號(hào),由主設(shè)備產(chǎn)生。

其中,SEL是控制芯片是否被選中,也就是說只有片選信號(hào)為預(yù)先規(guī)定的使能信號(hào)時(shí),對此芯片的操作才有效。這就允許在同一總線上連接多個(gè)SPI設(shè)備成為可能。由SCLK提供時(shí)鐘脈沖,MOSI和MISO則基于此脈沖完成數(shù)據(jù)傳輸。數(shù)據(jù)輸出通過MOSI,MISO線,數(shù)據(jù)在時(shí)鐘上升沿或下降沿時(shí)改變,在緊接著的下降沿或上升沿被讀取,完成一位數(shù)據(jù)傳輸。輸入也使用同樣的原理。這樣,在至少8次時(shí)鐘信號(hào)改變內(nèi),就可以完成8位數(shù)據(jù)的傳輸。MAC控制器采取的是上升沿接收、下降沿發(fā)送、高位先發(fā)送。

3 綜合結(jié)果

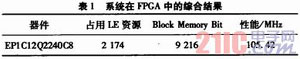

本設(shè)計(jì)采用Verilog語言,F(xiàn)PGA芯片使用Altera公司的Cyclone,整個(gè)設(shè)計(jì)都是在Altera公司的Quartus8.0下進(jìn)行綜合、布局布線以及仿真。表1是綜合結(jié)果。

4 結(jié)束語

本文給出了完全用FPGA實(shí)現(xiàn)無線傳感器網(wǎng)絡(luò)MAC控制器的設(shè)計(jì)方法,該方法只需外接物理層芯片和MCU便可完成網(wǎng)絡(luò)功能。從而有效降低了成本,減少了版面積,提高了整個(gè)系統(tǒng)的集成度。